IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: IV Month of publication: April 2017

DOI: http://doi.org/10.22214/ijraset.2017.4108

www.ijraset.com

Call: 🕥 08813907089 🔰 E-mail ID: ijraset@gmail.com

## International Journal for Research in Applied Science & Engineering Technology (IJRASET) Adaptive Simplified Successive Cancellation for Polar Codes Based on Frozen Bits

Nandhini. T<sup>1</sup>, Gnana Muruga Gandhi. N. G<sup>2</sup>, Kalimuthu. T<sup>3</sup> <sup>1,2,3</sup> Department of ECE, SCADCET, Tamil Nadu, India

Abstract: Polar codes have been recently proposed as the first low complexity of error correcting codes for wireless channels that can provably achieve the capacity of symmetric binary-input memory less channels. Here, the bit error rate performance of finite-length polar codes is performed under Successive-Cancellation decoding. In existing ASM controller is used in high radix computation, utilizes high hardware resources that increase implementation complexity with reduced performance. To overcome this by using proposed architecture, the length of polar code N can be reduced from N-1 to N/2-1 from the decoding latency of the code, it can replace high hardware resources in merged processing elements to control the decoding by state transition method results low power consumption. The 8-point polar coder is proposed that can be easily combined to form efficient N-point polar coder architecture, so that it can achieve parallelism and bit-pipelining techniques result in low power operation and easily expandable architecture with respect to data and/or co- efficient word length. Finally, in this paper the position of frozen bits and architecture of 8-bit SC decoder was analyzed. Our coding scheme also achieves the capacity of the physically degraded channel with better error control performance.

Keywords: polar codes, frozen bits, Simplified Successive-Cancellation decoding, decoding latency reduction, merged processing elements.

#### I. INTRODUCTION

Polar codes are the error correcting code the capacity of those codes can be achieved with efficient encoding and decoding algorithm for any symmetric binary memory less channels with explicit construction which produce low complexity [1]. The complexity for the block length N of encoding and decoding can be calculated through O (N log N) [2]. Code length of the polar code is  $N=2^n$ , which requires very long code length. Because of the successive cancellation decoding (SC) scheme, large code length tends to a long decoding latency.

Despite the long code length the polar code is suffer from many problems such as lossless and lossy source coding [3], problems with side information, multiple access channel, etc. And SC decoder also suffer from the long block length by the high latency, so that it can be operate at recursive approach which is multiple bit decision for minimize the decoding length of polar code into pair decoding of length N/2 constituent codes rate as zeros or ones. Due to long latency and low throughput problem SCL is suffer which is corresponding to early SC decoder. To reduce the latency of SCL decoders multiple bit decision approach has been proposed with low power consumption using asynchronous SC decoder. Compared to typical synchronous SC decoders, the proposed Simplified SC decoder operates at much lower clock frequencies and decodes a codeword in one long clock cycle. Hardware usage is high for synchronous decoder combinational architecture. High latency for synchronous decoder is occurred due to shorter block length N=4. The input u1 and u2 perform the process through the Function (F) and Gate (G). Computation F and G can be used in merged processing elements (MPE). Output of the function is out\_F and the gate has produces the two output which is out\_G<sub>0</sub> and out\_G<sub>1</sub>. It can be calculate as follows

Out\_F=sign (u1) sign (u2) min(|u1|,|u2|)

$Out_G0 = u1 + u2$

Out\_G1=u2-u1

To solve that problem the present work is motivated by using we reduce the long decoding latency of the polar codes by using the merged processing elements (MPE) of F and G computation. Simplified SC (SSC) decoder architecture was proposed by frozen bits and information bits.

#### II. POLAR CODE

Polar encoding is a linear block error correcting code .It can be denoted by the generator matrix  $X=G \quad nU_N$  where N=2 is the code length,  $U_N$  is the permutation matrix of bit reversal and G is the Krone er power of the kernel matrix. The generator matrix for

www.ijraset.com IC Value: 45.98 Volume 5 Issue IV, April 2017 ISSN: 2321-9653

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

code word length is applying by generating the Kronecker power to kernel matrix. For the generator matrix the co de length is calculated by x=u.

$X = [u_0 u_1 u_2 u_3 u_4 u_5 u_6 u_7] G_2 \bigotimes^3$

The block length of polar code (n, m) can be generated through m-bit source message which is transmitted to n-bit message X=(u0,u1,u2,...,un-1) by the reliability of n-bit message of u is multiplied with the generator matrix nxn. From the long block length of SC decoder suffer from high latency, so that it can be operate at multiple recursive divide and conquer approach minimize the problem of decoding the length of polar code into pair decoding of length N/2 constituent codes. If the constituent code is 0, the recursion can be simplified as this case decoded recursion can be replaced with 1, thereby avoiding the delay and computation.

The input vector of encoder as  $x \in F_2^N$  consist of information part if and a frozen part  $x_F^c$ , where f is chosen in according to polar code design rule of binary signal function. Frozen part of  $x_F^c$  is fixed up to zero in here. A frozen bit indicator vector b is a 0-1 vector of length N. The receiver can be calculates a vector  $l=(l1,...,l_N)$  with

$l_i = log(P(v_i|u_i=0)-P(v_i|u_i=1))$

and connect it into SC decoder

#### III. SUCCESSIVE CANCELLATION DECODING

The polar code with SC decoding can achieve the capacity of binary symmetric memory less channel. There are many other algorithm can be used to improve the error rate performance in finite block length. We have use SC decoding in this section and other algorithm of polar code such as Belief propagation (BP) decoding, Successive Cancellation List (SCL) decoding and Sphere decoding.

Let  $u_i^N$  be the input sequence to the polar encoder,  $v_i^N$  be the output. The SC decoding can be sequential manner in nature. The estimation of the bit  $u_i$  based on the received vector v and estimation of  $u^{-1}$  pervious bit  $u_1^{i-1}$ . Let

$$\frac{L_N^{(i)}(v, u^{\Lambda_1^{i-1}}) = WN(i)(v, u^{\Lambda_1^{i-1}}|u_i=0)}{WN(i)(v, u^{\Lambda_1^{i-1}}|u_i=1)}$$

ui can be estimated as

$\mathbf{u}^{A_{i}} = \left\{ \begin{array}{c} 0 \text{ if } L_{N}^{(i)}(\mathbf{v},\mathbf{u}^{A_{1}}^{i-1}) \geq 1 \& \mathbf{i} \notin^{e} \\ 1 \text{ if } L_{N}^{(i)}(\mathbf{v},\mathbf{u}^{A_{1}}^{i-1}) < 1 \& \mathbf{i} \notin^{e} \\ \text{Frozen bit otherwise} \end{array} \right.$

For the N length of polar decoding can requires totally 2(N-1) clock cycles by the decoder. It has 50% of largest hardware efficiency in each active stage which means higher than half merged processing element (MPEs) are idle at same time, this is happen because of the previous code depend on the estimation of current bit, which forces all the code bits can produce successive

www.ijraset.com IC Value: 45.98 Volume 5 Issue IV, April 2017 ISSN: 2321-9653

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

output. Fast decoding can be achieve by look ahead techniques, the loop computation can be reformulated which pre calculate all possible output of next code bit and then select proper one with multiplexer. Among all possible part only one with short latency and low hardware complexity can be selected.

#### IV. SIMPLIFIED SC DECODER ARCHITECTURE

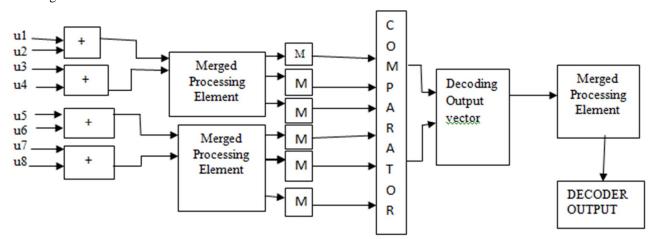

In here, the proposed Simplified SC (SSC) decoder architecture was used to removing the zero node trees (frozen bits) and replacing all one node trees (information bits) by matrix multiplication. Decoding in the system could be made by frozen bit indicator vector. The input of the system is U= (0, 1), the output V and transition probabilities {W (v|u):  $u \in U$ ,  $v \in V$ } where W is a discrete memory less channel. In each use of system a codeword  $u \in _2N$  is transmitted and channel output vector  $v \in VN$  is received. The number of required decoding procedure for the polar code with length N is N/2. Decoding procedure for the polar code length is N=8.For each stage s<sub>i</sub> is active in 2<sup>s</sup><sub>i-1</sub> times and it has N/2si MPE, the number of MPE calculations can be defined as below. of MPE = N/2x log2N

Fig.1 Proposed architecture of 8-bit SC decoder

The decoding latency of 8-bit SC decoder can reduce about 58% and the number of MPE calculation by about 60%. Position of frozen bits and information bit can be determined by using channel polarization technique. The first half the input bits are changed into frozen bits in information bit (u1~uN/2) which is located. By the loss of information bits in previous section is formed according to the rank of the frozen bit position in the second half of the position are occurred based on changes in number of frozen bits in second half (u N/2+1~uN).Decoding of the bit is done in the reverse manner with respect to encoding. It required two separate decoding sections for the block length which are 4 for decodes the code C1 and C2. The input bits u1, u2, u3 and u4 are frozen bits and u4, u6, u7 and u8.

For the N length of polar decoding can requires totally 2(N-1) clock cycles by the decoder. It has 50% of largest hardware efficiency in each active stage which means higher than half merged processing element (MPEs) are idle at same time, this is happen because of the previous code depend on the estimation of current bit, which forces all the code bits can produce successive output. Fast decoding can be achieve by look ahead techniques, the loop computation can be reformulated which pre calculate all possible output of next code bit and then select proper one with multiplexer. Among all possible part only one with short latency and low hardware complexity can be selected. The input from the merged processing element is counted in iteration count. For each input bit is counted in iteration count from that the count value is increased. After counting the input bit the performing the operation processing element. The decoded input is performs the operation successive cancellation in processing element of function generator to store the output in the buffer. Decoding is the opposite process that conversion of encoded format back to the original sequence of characters. The advantage is low power consumption, reduces switching activities and provides area efficient architecture. It can be used in tele- communication, mobile communication , hard drives, memory.

#### V. SIMULATION RESULT

In this paper I have designed the proposing technique. This process is designed using Verilog. The RTL description is synthesis and simulated in Xilinx ISE 13.2i. The simulated wave forms are presented below.

www.ijraset.com IC Value: 45.98

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

The 64-bit input data is given as input to polar encoder. It performs the encoding operation which generated the number randomly such as 1 or 0 using simplified successive cancellation decoder. The noise in the generated random signal can be replaced by the de blocking filter. After encoding the decoder output is obtained using simplified successive cancellation logic and merged processing element. The merged processing array performs the butterfly operation of FFT to produce decoding output as shown in fig 2.

| ime        | Value    | 39,067,649,990 ps     | 39 | ,067,649,992 ps |          | 39,067,649,994 ps | 39,067,649,996 |

|------------|----------|-----------------------|----|-----------------|----------|-------------------|----------------|

| ₩0[7:0]    | 00100100 |                       |    |                 | 00100100 |                   |                |

| ≼ v1[7:0]  | 10000001 |                       |    |                 | 10000001 |                   |                |

| ₩{ v2[7:0] | 00001001 |                       |    |                 | 00001001 |                   |                |

| 📲 v3[7:0]  | 01100011 |                       |    |                 | 01100011 |                   |                |

| 📲 v4[7:0]  | 00001101 |                       |    |                 | 00001101 |                   |                |

| V5[7:0]    | 10001101 |                       |    |                 | 10001101 |                   |                |

| V6[7:0]    | 01100101 |                       |    |                 | 01100101 |                   |                |

| 📲 v7[7:0]  | 00010010 |                       |    |                 | 00010010 |                   |                |

| 🔚 clk      | 1        |                       |    |                 |          |                   |                |

| ᠡ rst      | 0        |                       |    |                 |          |                   |                |

| 🔚 enable   | 1        |                       |    |                 |          |                   |                |

| u0[7:0]    | 00100100 |                       |    |                 | 00100100 |                   |                |

| 📷 u1[7:0]  | 10000001 |                       |    |                 | 10000001 |                   |                |

| u2[7:0]    | 00001001 |                       |    |                 | 00001001 |                   |                |

| u3[7:0]    | 01100011 |                       |    |                 | 01100011 |                   |                |

| 📷 u4[7:0]  | 00001101 |                       |    |                 | 00001101 |                   |                |

|            |          | X1: 39,067,649,994 ps |    |                 |          |                   | Ē              |

Fig2. Output signal

The simulation using Quartus II is resulted as the power consumption of the total thermal power dissipation is 55.96mw. It has low user provided insufficient toggle rate data. Compared to existing process it can reduce the delay by using the proposed architecture of Simplified Successive Cancellation (SSC).

#### VI. CONCLUSION

The latency of polar code can reduce by using Merged Processing Element of proposed architecture by analysis the position of frozen bit and proposed architecture of Simplified SC (SSC) decoder. A very low utilization rate was achieved by the use of butterfly-based 8-point polar code architecture .The technique parallelism and bit-pipelining result in low power consumption is 55.96 mw with reduce area and delay.

#### REFERENCES

- [1] E. Arıkan, "Polar codes: A pipelined implementation," in Proc. Int. Symp. Broadband Commun. (ISBC2010), Melaka, Malaysia, 2010, pp. 11–14.

- [2] C. Leroux, I. Tal, A. Vardy, and W. J. Gross, "Hardware architectures for successive cancellation decoding of polar codes," 2010. [Online]. Available: http://arxiv.org/abs/1011.2919

- [3] A. Pamuk, "An FPGA implementation architecture for decoding of polar codes," in Proc. 8th Int. Symp. Wireless Commun. (ISWCS), 2011, pp. 437-441.

- [4] C. Zhang and K. K. Parhi, "Low-latency sequential and overlapped architectures for successive cancellation polar decoder," IEEE Trans. Signal Process., vol. 61, no. 10, pp. 2429-2441, May 2013.

- [5] Kai Niu and Kai Chen, "CRC-aided decoding of polar codes," IEEE Commun. Lett., vol. 16, no. 10, pp. 1688-1671, Oct. 2012

- [6] C. Zhang and K. K. Parhi, "Latency analysis and architecture design of simplified SC polar decoders," IEEE Trans. Circuits Syst. II, ExpressBriefs, vol. 61, no. 2, pp. 115-119, Feb. 2014.

- [7] E. Arikan,"A performance comparison of polar codes and Reed-Muller codes," IEEE Commun. Lett., vol. 12, pp. 447-449, 2008.

- [8] A. Mishra, A. Raymond, L. Amaru, G. Sarkis, C. Leroux, P. Meinerzhagen, A. Burg, and W. Gross, "A successive cancellationdecoder ASIC for a 1024-bit polar code in 180 nm CMOS," in Proc. IEEE Asian Solid State Circuits Conf. (A-SSCC), 2012, pp. 205–208.

- Y. Fan and C.-Y. Tsui, "An efficient partial-sum network architecture for semi-parallel polar codes decoder implementation," IEEE Trans. Signal Process., vol. 62, no. 12, pp. 3165–3179, Jun. 2014.

- [10] B. Yuan and K. Parhi, "Low-latency successive-cancellation list decoders for polar codes with multibit decision," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 23, no. 10, pp. 2268–2280, Oct. 2015.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)