# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: V Month of publication: May 2017

DOI:

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

# The Modified SEPIC Converter with Extra Boost Unit and Without Coupling Inductor for PV Application

Akshay Kumar D<sup>1</sup>, Dr. R. V. Parimala<sup>2</sup>

<sup>1</sup>PG student Department of Electrical and Electronics Engineering, BNMIT, Bengaluru, INDIA. <sup>2</sup>HOD, Department of Electrical and Electronics Engineering, BNMIT, Bengaluru, INDIA.

Abstract-In this paper, the modified SEPIC converter with extra boost circuit and without coupling inductor is proposed for PV application using perturb and observe mppt algorithm. The proposed DC-DC converter has only one MOSFET switch with minimum voltage stress and this reduces the complex circuit design. The proposed converter is connected in between PV panel and load to obtain high voltage without extreme duty ratio. In this paper input voltage of 40V is obtained from PV panel is fed to converter in order to obtained output voltage of 400V with switching frequency of 100kHz. The circuit operation and passive parameter design of this proposed converter are discussed in details.

Keywords-SEPIC, MPPT algorithm, PV panel.

### I. INTRODUCTION

Today, Indian energy scenario is mainly focuses on harvesting and maximum usage of green energy resources such as fuel cell, wind energy and solar energy etc, due to depleting nature of conventional fuels and increasing energy demand of society. In order to meet demand the high voltage DC –DC converters must be incorporate between PV panels and grid. As PV panel have less output voltage of about 12 to 40 V, these must be boost to 440 V for grid applications. Therefore, DC-DC converter having high voltage output required to be placed between PV array and high voltage dc grid. Unfortunately, conventional high voltage converter are not available because of high duty ratio and complex circuit design. In order to have high voltage converters, following type of converter have been proposed by 1) addition of switching capacitors or switching inductors to conventional converters[1-2]; 2) series connection of outputs [3-4];3) combining output of several conventional converters[5];4) integrating coupled inductor and voltage-doubling circuit or switching inductor[6-11]; 5) interleaving technique[12-13].however, all of these techniques have their own demerits. High setup gain, simple modified control structure, higher efficiency and minimum voltage stress are the features still needed.

In this paper, the modified SEPIC converter with extra boost unit circuit and without inductor coupled is proposed forPV application using Perturbs and observe MPPT algorithm.It produces higher voltage ratio, reduced voltage stress of switch and continuous operation of input current.

### II. PV CELL MODELING AND MPPT ALGORITHM

### A. PV CELL MODELLING

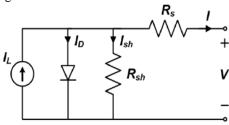

The circuit configuration of PV cell is shown in fig.1.In this circuit  $R_s$  is series resistance of PN junction cell and  $R_{sh}$  is shunt resistance which is inversely in relation with leakage current to the ground.  $I_D$  and  $I_{sh}$  are diode current and shunt leakage current, where output current I is obtained by applying KCL.

Fig .1. Circuit configuration of PV cell.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

$$I_L = I_{Ph} - \left(I_d + I_{sh}\right) \tag{1}$$

Above equation is simplified by taking  $I_d + I_{sh} = I_o$  and hence equation becomes

$$I_{L}=I_{Ph}-I_{O} \tag{2}$$

Photon current is generated on absorption of solar radiation; hence photocurrent is directly proportional to variation of solar irradiance and temperature, is given by.

$$I_{ph} = \left(I_{scr} + k_i \Delta T\right) \frac{G}{G_r} \tag{3}$$

Where  $I_{scr}$  is short circuit current at normal conditions (25°C and 1000w/m²),  $k_i$  is short circuit current temperature coefficient. G is solar irradiance in W/m² and  $G_r$  is nominal irradiance in normal conditions (25°C and 1000w/m²). $\Delta T$  is difference of operating temperature and nominal operating temperature ( $T - T_{ref}$ ). Reverse saturation current is given by.

$$I_d = I_{rs} * \left(\frac{T}{T_{ref}}\right)^3 exp\left[\left(\frac{qE_{qo}}{AK} * \frac{\Delta T}{T_{ref}T}\right)\right]$$

(4)

Where Irs is reverse saturation current for nominal temperature and irradiance and Ego is band gap energy of semiconductor material, current I is given by

$$I = I_L - I_O(\exp(q \frac{v + IR_S}{AKT}) - 1) - \frac{v + IR_S}{R_P}$$

(5)

#### B. Perturb and observe algorithm

This method is widely used, the operating output voltage is sampled and then it changes the operating output voltage in the required direction and samples the dP/dV. If  $\frac{dp}{dv}$  is positive, then it increases the output voltage towards the MPP till  $\frac{dp}{dv}$  is negative. This iteration is continues till the algorithm reaches the final MPP. This is not applicable when then solar irradiation various continuously. The voltage never reaches the required value, but perturbs in between the maximum power point (MPP).

### III. OPEATION OF PROPOSED CONVERTER

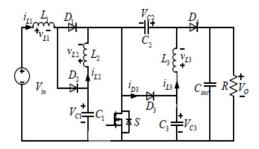

The proposed converter circuit configuration is shown below in Fig.2,It is obtained from a conventional SEPIC converter ,where capacitance  $C_1$ , inductance  $L_1$ ,diodes  $D_1$  and  $D_2$ ,forms an extra boost unit circuit, while capacitance  $C_3$ , and diode  $D_3$  are forms an clamping circuit for MOSFET switch S .For the study of proposed converter ,let the following assumptions are made :1) converter is operated in steady state mode.2) all components are ideal;3) C2 andC3 are equal, Cout is more in order to make constant output voltage.

Fig.2.Single switch proposed converter.

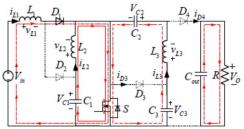

Mode I [ $t_0$ - $t_1$ ]: When t= $t_0$ , switch S is switch on. Diode  $D_1$  isforward biased, while diodes  $D_2$ ,  $D_3$  and  $D_4$  are reverse biased. The circuit configuration and direction of current in this mode is shown in Fig. 3.Intitially assumed that all capacitors are fully charged, in this mode, the input voltage  $V_{in}$  energizes the inductor  $L_1$  via $D_1$  and switch S. Then the inductor voltage  $V_{L1}$  across  $L_1$  is  $V_{in}$ . The capacitor  $C_1$  energizes inductor  $L_2$  via switch S, and then the inductor voltage  $V_{L2}$  across  $L_2$  is  $V_{C1}$ . The capacitor  $C_3$  energizes  $L_3$  and  $C_2$

### **International Journal for Research in Applied Science & Engineering Technology (IJRASET)**

viaswitch S, and then the inductor voltage  $V_{L3}$  across  $L_3$  ( $V_{C3}$ - $V_{C2}$ ). So, the inductor currents  $i_{L1}$ ,  $i_{L2}$  and  $i_{L3}$  linearly increase. The capacitor  $C_{out}$  gives stored energy to the load R, and makes the output voltage  $V_o$ constant. When  $t=t_1$ , Switch s is turned off, Mode I completed.

Fig .3. Circuit configuration of mode I in CCM.

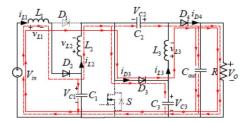

Mode II  $[t_1-t_2]$ : When  $t=t_1$ , switch S is turned off.  $D_1$  is reverse biased, while  $D_2$ ,  $D_3$  and  $D_4$  are forward biased. The circuit configuration and direction of current in this mode is shown in Fig.5. Capacitor C<sub>1</sub> is charges by the input voltage V<sub>in</sub>and inductor  $L_1$  via $D_2$  and  $V_{L1}$  is  $(V_{in}-V_{C1})$ . At the same time,  $V_{in}$ ,  $L_1$  and  $L_2$ charges  $C_3$ via $D_2$ , then  $V_{L2}$  is  $(V_{C1}-V_{C3})$ . Moreover, the stored energy of  $V_{in}$ ,  $L_1$ ,  $L_2$  and  $L_3$  supply to  $C_{out}$  and load R, and  $V_{L3}$  is equal to  $-V_{C2}$ . So, the inductor currents  $i_{L1}$ ,  $i_{L2}$  and  $i_{L3}$  decrease linearly. When t=t2, switch S is turned on and mode II is completed.

Fig .4.circuit configuration of mode IIin CCM.

From inductor voltage second balanced principle, we have

$$D V_{in} = (1-D) (V_{C1}-V_{In})$$

(6)

$$DV_{C1} = (1-D) (V_{C3} - V_{C2})$$

(7)

$$D(V_{C3}-V_{C2}) = (1-D)V_{C2}$$

(8)

Assuming capacitor voltage is constant during steady state operation from Equation (6), (7), (8), capacitor voltages are,

$$V_{in}=(1-D)V_{C1}$$

(9)

$$V_{C1} = (1-D)V_{C3}$$

(10)

$$V_{C2} = DV_{C3} \tag{11}$$

During stage II

$$V_0 = V_{C2} + V_{C3}$$

(12)

Voltage gain in CCM mode is expressed by

$$M_{CCM} = \frac{V_O}{V_{in}} = \frac{(1+D)}{(1-D)^2} \tag{13}$$

#### IV. PASSIVE PARAMETER DESIGN

### Inductor design

From fig.3.inductor L1 current ripple in CCM is expressed by

$$\Delta i_{L1} = \frac{V_{in}D}{f_{SL_1}} \tag{14}$$

$$\Delta i_{L1} = \frac{V_{in}D}{f_S L_1}$$

$$L_1 = \frac{V_{in}D}{f_S \Delta i_{L1}} = \frac{V_{in}D}{\Delta i \% I_{L1} f_S}$$

$$\tag{14}$$

Where  $\nabla i\%$  = inductor current ripple acceptance.

Similarly, inductor  $L_2$  and  $L_3$  are defined by

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

$$L_2 = \frac{V_{C1}D}{f_S\Delta i_{L2}} = \frac{V_{C1}D}{\Delta i\% I_{L2}f_S}$$

(16)

$$L_{3} = \frac{(V_{C3} - V_{C2})D}{f_{S} \, \Delta i_{L3}} = \frac{V_{C1} \, D}{\Delta i^{6} I_{L3} f_{S}} \tag{17}$$

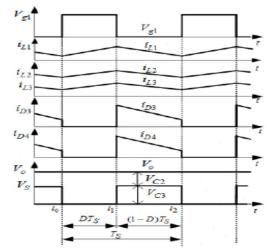

Fig.5.Theoretical wave form of CCM mode.

From Fig.4, the below current relationships are obtained, for mode I

$$i_{C3} = -i_{L2}$$

(18)

$$i_{C2} = -i_{C3} = i_{L3}$$

(19)

From mode II

$$i_{C1} = i_{L1} - i_{L2}$$

(20)

$$i_{C2} = -i_{C3} = i_{L3} - I_o$$

(21)

Fromcapacitor ampere second balance principle, we have

$$I_{L2} = (1-D) I_{L3}$$

(22)

$$I_{L3} = (1-D) I_O$$

(23)

If the power output Po, converteref ficiency  $\eta$  and resistive load R are known, as

$$I_{L1} = I_{in} = \frac{P_o}{nV}$$

(24)

$$I_{O} = \sqrt{\frac{P_{O}}{R}} \tag{25}$$

### B. Capacitor design

Since capacitor C<sub>2</sub> current is equal to that of C<sub>3</sub> during mode I, the voltage potential of C<sub>2</sub> or C<sub>3</sub> is expressed by

$$\Delta V_{C2} = \frac{I_{L3}D}{C_2f_5} \tag{26}$$

$$\Delta V_{C3} = \frac{I_{L3}D}{C_2f_5} \tag{27}$$

Then

$$C_2 = C_3 = \frac{I_{L3}D}{\Delta V \% V_{C3} f_s} (28)$$

Where,  $\Delta V\%$  = capacitor voltage ripple acceptance, in addition, the capacitor  $C_1$  and  $C_{out}$  are large in order to keep the constant output voltage.

### C. Semiconductor components design

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

From Fig.3 and Fig.4,  $V_{DS}$  of the switch S in mode II is  $V_{C3}$ , the diode voltage of  $D_1$  is  $V_{L2}$  in mode II or  $V_{C3}$  -  $V_{C1}$ , that diode voltage on  $D_2$  equals to  $V_{L2}$  or  $V_{C1}$  in mode I, diode voltage of  $D_3$  is  $V_{C3}$ , and diode voltage  $D_4$  equals to the difference between Vo and  $V_{C2}$ . Then we have

$$V_{DS} = V_{C3} = \frac{V_{in}}{(1-D)^2} = \frac{V_0}{1+D}$$

(29)

$$V_{D1} = V_{C3} - V_{C1} = \frac{D}{(1-D)^2} V_{in} = \frac{D}{1+D} V_0$$

(30)

$$V_{D2} = V_{L2} = V_{C1} = \frac{V_{in}}{1 - D} = \frac{(1 - D)}{(1 + D)} V_O$$

(31)

$$V_{D3} = V_{C3} = \frac{D}{1+D} V_0 \tag{32}$$

$$V_{D4} = V_{o^{-}} V_{C2} = \frac{D}{1+D} V_{o}$$

(33)

Since current via switch S in mode I is the summation of inductor currents  $i_{L1}$ ,  $i_{L2}$  and  $i_{L3}$ , then peakcurrent in the switch will be

$$I_{\text{SMAX}} = \left(\frac{1 + \Delta i\%}{2}\right) \left(I_{L1} + I_{L2} + I_{L3}\right) \tag{34}$$

Both diode currents  $i_{D1}$  and  $i_{D2}$  are part of inductor current  $i_{L1}$ , and then the peak diode currents of  $i_{D1}$  and  $i_{D2}$  will be

$$I_{\text{D1MAX}} = I_{\text{D2MAX}} = \left(\frac{1 + \Delta i \%}{2}\right) I_{L1} \tag{35}$$

It is known that  $i_{D3} = i_{L2} + i_{C2} = i_{L3} + i_{C3}$ ,  $i_{C2} = i_{C3}$  in mode II, then peak current of diode $i_{D3}$  is

$$I_{\text{D3MAX}} = \left(\frac{4+2\Delta i\%}{8}\right) (I_{L2} + I_{L3})$$

(36)

Finally, the current via  $D_4$  is output current  $I_0$

### V. RESULTS AND DISCUSSION

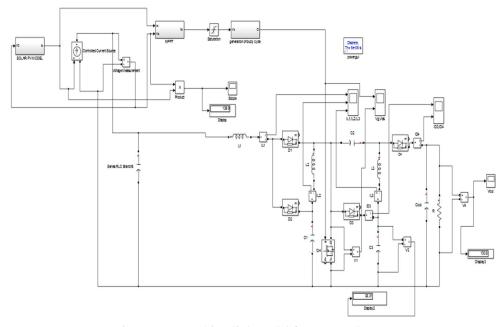

In order to analysised the theoretical analysis, the operation of proposed Converter is simulated using MATLAB simulink and shown below Fig.6 and component design values are listed in table 1

Fig.6.MATLAB/simulink model for proposed converter.

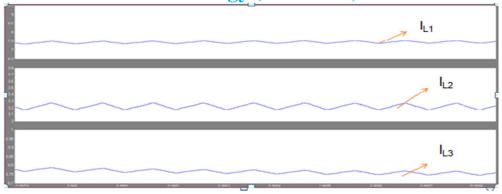

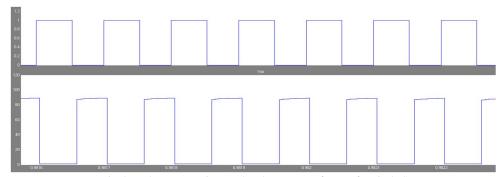

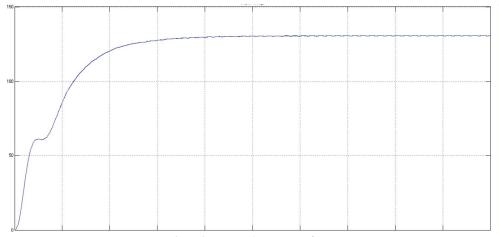

The simulation waveforms of inductor currents  $I_{L1}$ ,  $I_{L2}$  and  $I_{L3}$ , wave form of switching pulse generation and voltage across switch S and output voltage waveform are shown in Fig.7, Fig.8, and Fig.9 respectively. Obviously, the inductors current are continuous. So the converter is operating in CCM. From all the above, the simulation results agree with the theoretical analysis.

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig.7.Inductor current waveforms.

Fig.8. pulse generation and voltage waveform of switch S.

Fig.9.Output voltage waveform.

### VI. CONCLUTION

In this paper, the modified SEPIC converter with extra boost unit circuit and without coupling inductor is proposed. It produces high voltage output without coupling inductor. Moreover, there is one MOSFET switch and the peak voltages of semiconductor switch are less than the output voltage, this makes the power switch with lower rating and all these features made this proposed converter suitable for PV application.

### **REFERENCES**

- [1] Xiong, Song, Siew-Chong Tan, and Siu-Chung Wong. "Analysis and design of a high-voltage-gain hybrid switched-capacitor buck converter", IEEE Trans on Circuits and Systems I: Regular Papers, vol.59, no.5, pp.1132-1141, May 2012.

- [2] Axelrod, Boris, Yefim Berkovich, and Adrian Ioinovici. "Switched capacitor/switched-inductor structures for getting transformer less hybrid DC–DC PWM converters", IEEE Trans on Circuits and Systems I: Regular Papers, vol.55, no.2, pp.687-696, Feb 2008.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

- [3] Park, Ki-Bum, Gun-Woo Moon, and Myung-Joong Youn. "Non isolated high step-up stacked converter based on boost-integrated isolated converter", IEEE Trans on Power Electronics, vol.26, no.2, pp.577-587, Feb 2012

- [4] Lee, J-Y, and Hwang, S-N, "Non-isolated high-gain boost converter using voltage-stacking cell", Electronics Letters, vol.44, no.10, pp.644-646, Oct 2008

- [5] Morales-Saldana, J. A., et al. "Multi loop controller design for a quadratic boost converter", IET Electric Power Applications, vol.1, no.3, pp.362-367, 2007

- [6] Zhao, Yi, et al. "High step-up boost converter with coupled inductor and switched capacitor", 5th IET International Conference on Power Electronics, Machines and Drives (PEMD 2010), 2010

- [7] Spiazzi, Giorgio, Paolo Mattavelli, and Alessandro Costabeber. "High step-up ratio, fly back converter with active clamp and voltage multiplier", IEEE Trans on Power Electronics, vol.26, no.11, pp.3205-3214, Nov 2011

- [8] Chen, Shih-Ming, et al. "A cascaded high step-up dc-dc converter with single switch for micro source applications", IEEE Trans on Power Electronics, vol.26, no.4, pp.1146-1153, Apr 2011

- [9] Lee, Yuang-Shung, et al. "Quadratic boost converter with switched capacitor and coupled inductor for PV system applications", 2013 IEEE10th International Conference on. Power Electronic and Drive Systems (PEDS), 2013

- [10] Hsieh, Yi-Ping, et al. "Novel high step-up DC-DC converter with coupled-inductor and switched-capacitor techniques", IEEE Trans on Industrial Electronics, vol.59, no.2, pp. 998-1007, Feb 2012

- [11] Yang, Lung-Sheng, et al. "Novel high step-up DC-DC converter with coupled-inductor and voltage-doubler circuits", IEEE Trans on Industrial Electronics, vol.58, no.9, pp.4196-4206, Sep 2011

- [12] Li, Weichen, et al. "Interleaved high step-up ZVT converter with built-in transformer voltage doubler cell for distributed PV generation system", IEEE Trans on Power Electronics, vol.28, no.1, pp.300-313, Jan 2013

- [13] Henn, Gustavo AL, et al. "Interleaved-boost converter with high voltage gain", IEEE Trans on Power Electronics, vol.25, no.11, pp. 2753-2761, Nov 2010.

### **BIOGRAPHY**

AKSHAY KUMAR D<sup>1</sup> obtained B.E (E&E) degree from AIT, Chikkamagaluru, under VTU, Belagavi and now pursuing M.TECH (CAID) from BNMIT, Bengaluru, under VTU Belagavi and area of interest are power electronics power system and control theory.Email id:akshay.boregowda633@gmail.com

Dr. R.V.PARIMALA<sup>2</sup> obtained B.E (E&E) degree from Sri Jayachamarajendra College of Engineering, Mysore University, M.E (Power Systems) from National Institute of Engineering, Mysore University & Ph.D (Distribution Automation) from VTU, Belagavi. She has 27 years of teaching experience with 13 publications in reputed International Journals & Conferences and Distribution System Automation, Artificial Intelligence application to Power System and Power Electronics. Email Id:ryparimala@bnmit.in

10.22214/IJRASET

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)