IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 12 Issue: IV Month of publication: April 2024

DOI: https://doi.org/10.22214/ijraset.2024.60600

www.ijraset.com

Call: 🕥 08813907089 🔰 E-mail ID: ijraset@gmail.com

## Design and Simulation of Vedic Multiplier Using Verilog HDL

Swarit Pandey<sup>1</sup>, Vaibhav Mohan<sup>2</sup>, Kamal Bhatia<sup>3</sup>, Shilpa Srivastava<sup>4</sup> Department of Electronics & Communication Engineering ABES Engineering College Ghaziabad, India

Abstract: This Paper is created for the simulation of a high speed Vedic multiplier. In the proposed paper, the multiplier circuit is designed by using algorithms that involve Vedic Mathematics. Calculations that involve Vedic mathematics are derived from the old contexts known as Vedas. The VHDL programs are synthesized and simulated using Xilinx ISE simulator. The study of Vedic multipliers is done in comparison with the conventional multipliers to find the fact that which multiplier is fast and efficient and the research and analysis has shown that the Vedic multiplier is more efficient than conventional multipliers because of its fast response in digital signal processing and it gives less delay in system logic design. Vedic mathematics used in the Vedic multiplier increases the speed of multiplier as it reduces the number of partial products. Hence, the speed of the overall digital design can be increased by implementing a Vedic multiplier.

Keywords: Multiplier, Adder; Testbench; RTL, Power Reduction

#### I. INTRODUCTION

Multipliers are a major part of DSP algorithms that are used in various fields including computer applications and digital system designing. Multiplication is the most fundamental function in an arithmetic operation. Operations that involve multiplications are slower than addition and subtraction hence it is advised to implement a multiplier that performs fast multiplications to increase the speed of the calculation as fast multiplications result in fast calculations. A high-speed multiplier is needed in system and logical design because it decreases the processors time in DSP algorithms and algorithms involving FET. The need for fast multipliers has become significantly important because the computing applications of the computer is expanding day by day. Vedic multiplier is a fast, convenient and logical way of performing calculations that uses Vedic mathematics derived from the ancient contexts known as 'Vedas'. It minimizes the processors time by reducing the number of delays and partial products. Vedic multiplier is preferred over conventional multipliers as it produces minimum number of partial products while performing multiplication operation.

#### II. METHODOLOGY

The project is implemented using the following tools and software:

- 1) XILINX ISE SIMULATOR

- 2) VERILOG HDL

- 3) URDHVA- TIRYAKBHYAM SUTRA

- Algorithm-

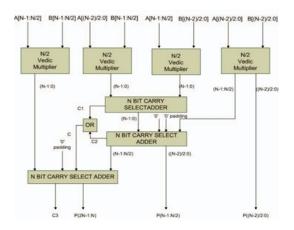

- Flowchart of NxN Vedic Multiplier Multiplier :

Applied Solution

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 12 Issue IV Apr 2024- Available at www.ijraset.com

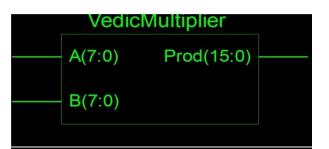

• Block Diagram of 8x8 Multiplier :

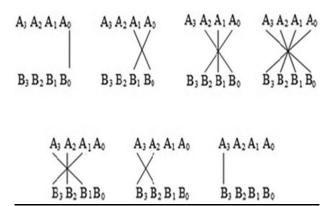

• 2x2 Multiplier :

Step 1: A1 x B1 = (multiplying the left side) Step 3: A2 x B2 = (multiplying the right side) Step 2: (B2 x A1) + (B1 x A2) = (cross-multiplying) both sides)

• 4x4 Multiplier :

4x4 Multiplier is implemented by using 2x2 Vedic Multiplier blocks.

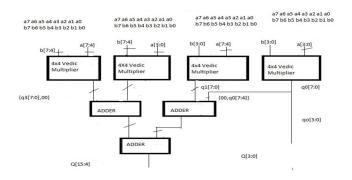

• 8x8 Multiplier :

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 12 Issue IV Apr 2024- Available at www.ijraset.com

This diagram illustrates the basic structure of the 8x8 Vedic multiplier using four 4x4 multipliers and 12-bit adders. Each 4x4 multiplier performs the multiplication of two 4-bit numbers, and the adders accumulate the partial products to produce the final result.

#### III. SIMULATION RESULT

Simulation Result of 2x2 Multiplier on Xilinx ISE Tool:

Simulation Result of 4x4 Multiplier on Xilinx ISE Tool:

| ne         | Value | 0.000<br>0 ns | ns | ÷. |    | 200 | Ins | î. |    |

|------------|-------|---------------|----|----|----|-----|-----|----|----|

| 🔏 out[7:0] | 4     | Ċ             | 4  | X  | 27 | X   | 169 | X  | 10 |

| 👹 a[3:0]   | 4     |               | 4  | X  | 9  | X   | 13  | X  | 5  |

| 😽 b[3:0]   | 1     | $\square$     | 1  | X  | 3  | X   | 13  | X  | 2  |

|            | 1     | JU            |    | ź  |    | ŧ   |     | ŷ: |    |

|            |       |               |    |    |    |     |     |    |    |

|            |       |               |    |    |    |     |     |    |    |

|            |       |               |    |    |    |     |     |    |    |

|            |       |               |    |    |    |     |     |    |    |

|            |       |               |    |    |    |     |     |    |    |

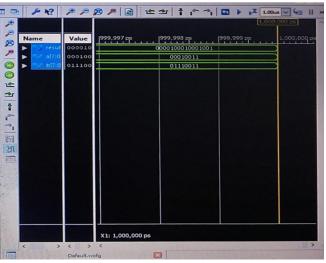

Simulation Result of 8x8 Multiplier on Xilinx ISE Tool:

A A Dalled Scherner

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 12 Issue IV Apr 2024- Available at www.ijraset.com

#### IV. RESULT AND CONCLUSION

- 1) This implementation is carried out on Spartan-6 board, and the results are displayed on the LCD of the Spartan-6 The Xilinx software has been an effective tool in the modelling of 2x2, 4x4 and 8x8 multipliers based on the principles of Vedic Mathematics, specifically the Urdhvatiryakbhyam sutra. The multiplier designs are implemented using digital circuits consisting of half adder and full adder circuits.

- 2) The implementation of vedic multiplier circuits has resulted in fast calculations by decreasing the processors time and delay. The given review paper is an outline of 2x2 and 4x4 vedic multiplier implementation which further lays down the outline of other NxN multipliers.

- 3) The proposed model of 2-bit and 4-bit and Vedic multiplier uses logic gates and carry adders, resulting in fast response, memory usage, and logic levels when compared to other conventional multipliers. The design is implemented using a carry select adder for performing the calculation of partial products This vedic multiplier simulation is used for fast multiplications in computer, DSP and FFT applications.

- 4) The 8-bit Vedic multiplier architecture uses logic gates and carry adders. Together latency, memory usage and logic levels are reduced when compared to the drag coefficient designs.

#### REFERENCES

- [1] Jagadguru Swami Sri Bharati Krishna Tirthji Maharaja authored "Vedic Mathematics,", India, in 1986.

- [2] A multiplier design in ancient Indian Vedic mathematics was presented by Honey Durga Tiwari, Ganzorig Gankhuyag, Chan MO Kim, and Yong Beom Cho from the Department of Electronics Engineering at Konkuk University in Seoul, South Korea.

- [3] "Design and Implementation of High Speed 4x4 Vedic Multiplier" was authored by Debasish Subudhi, Kanhu Charan Gauda, and Abinash Kumar Pala, published in Volume 4, Issue 1 1, November 2014, with ISSN 2277 128X.

- [4] Jagadguru Swami Sri Bharath Krishna Tirthji's work, "Vedic Mathematics or Sixteen Simple Sutras from the Vedas," was published by Motilal Banarasidas in Varanasi (India) in 1986.

- [5] Cristian Violatti provided information on "The Vedas" in an article titled Ancient History Encyclopedia, retrieved from https://www.ancient.eu/The\_Vedas/in January 2013.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)