# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 13 Issue: V Month of publication: May 2025

**DOI:** https://doi.org/10.22214/ijraset.2025.71531

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

Volume 13 Issue V May 2025- Available at www.ijraset.com

### Comparison of Performance Fault-Tolerant Five Level Inverter with and without PWM Technique Multilevel Inverter

N. Rahul<sup>1</sup>, T. Murali Krishna<sup>2</sup>, B. Anil Kumar<sup>3</sup>, B. Rohith<sup>4</sup>, P. Karthikeya<sup>5</sup>

Department of Electrical and Electronics Engineering, Chaitanya Bharathi Institute of Technology(A), Gandipet, Hyderabad

Abstract: Five-level Neutral Point Clamped (NPC) inverters are widely utilized in high-power and industrial systems due to their ability to generate high-quality output waveforms, minimize Total Harmonic Distortion (THD), and evenly distribute voltage stress across semiconductor switches. Despite these advantages, their intricate topology makes them vulnerable to faults such as open-circuit switches, diode failures, and imbalanced capacitor voltages. Such faults can severely impact output performance, cause waveform distortion, and potentially lead to complete system failure, particularly in precision-demanding environments like motor drives and industrial controls. This paper investigates the fault behaviour of conventional five-level NPC inverters and contrasts their performance with a Pulse Width Modulation (PWM)-based fault-tolerant inverter design. Traditional fault mitigation approaches often rely on additional hardware or redundancy, increasing both complexity and cost. In contrast, the proposed method employs a control-centric strategy using PWM to dynamically adapt switching states in the presence of faults, ensuring balanced voltage output and reduced harmonic distortion without requiring extra components. Comprehensive simulations were carried out under several fault scenarios, including single-switch failures, clamping diode defects, and imbalanced DC-link conditions. The analysis focuses on key performance indicators such as output voltage quality, THD levels, and system recovery response. The results reveal that the PWM-controlled fault-tolerant inverter consistently outperforms its conventional counterpart in maintaining waveform stability and overall reliability under fault conditions. This study emphasizes the effectiveness of PWM-based control strategies in enhancing the fault resilience and operational efficiency of five-level NPC inverter systems.

Keywords: Five-Level NPC Inverter, Fault Tolerance, PWM Control, Total Harmonic Distortion, Multilevel Converter, Inverter Reliability, Power Electronics, Fault Diagnosis.

#### I. INTRODUCTION

Multilevel inverters (MLIs) are now a primary solution in high-performance power conversion systems because they can produce output voltages with close-to-sinusoidal waveform shapes, lower harmonic content, and reduced voltage stress on power devices [1], [4], [5]. Of the various multilevel topologies, the Neutral Point Clamped (NPC) inverter has been particularly useful for medium and high-power applications, owing to its diode-clamping technique that facilitates efficient voltage division over the DC bus [7]. In particular, five-level inverter (NPC) inverters enhance the waveform resolution in comparison to three-level ones with more elevated Total Harmonic Distortion (THD), superior power quality, and reduced filter needs [1], [10], [5]. Despite the advantages, the complexity level of the circuit increases significantly with an increase in the number of components in the guise of clamping diodes, gate drivers, and semiconductor switches. All these increase the hardware failure susceptibility of the system, such as IGBTs open-circuits, diode short circuits, or capacitor voltage mismatches. Conventional five-level NPC inverters usually do not possess the capability to react to faults in real-time. During failures—like a faulty switch or unstable neutral point voltage imbalance and waveform distortion can occur, which may harm the attached load and lower system reliability [15].

This highlights the need for sophisticated inverter designs that can function properly even under partial hardware failure. Fault-tolerant structures overcome this challenge through the use of intelligent switching strategies and redundant channels that allow the inverter to maintain operational continuity as a fault is being sensed [17], [18]. If there is a fault in a driver or a switch, for instance, the system can present itself to provide functionality in a degraded mode usually reducing the five-level functionality to a three-level mode. Although this reduces the amplitude of the output voltage, countermeasures such as transformer compensation and energy redistribution provide acceptable voltage levels and system stability [19], [20]. The inclusion of Pulse Width Modulation (PWM) in the fault-tolerant control system enhances the flexibility and precision of the inverter.

Volume 13 Issue V May 2025- Available at www.ijraset.com

PWM methods allow the system to switch gate signals dynamically based on the faulty component such that faulty components are excluded and output is highly balanced. The technique not only promotes efficient real-time response but also reduces the need for additional hardware components, making it cost-efficient as well as effective fault-handling. This paper analyses performance variations in traditional five-level NPC inverters and a considered PWM-based fault-tolerant approach. Particular fault states such as switch failure, diode fault, and capacitor unbalance are analysed and compared with simulation. This study is focused on aspects such as the topology of the output voltage waveform, THD, and system tolerance to faults. The comparison indicates the effectiveness of PWM-based fault tolerance in maintaining inverter functionality and integrity upon faults.

#### II. LITERATURE SURVEY

#### A. Conventional Fault Tolerant Five Level NPC inverter

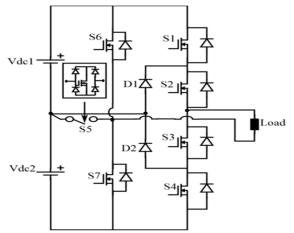

Fault-tolerant NPC inverters enhance system reliability through redundancy techniques that allow for continuous operation in the event of switch or diode faults [17]. Fault-handling capabilities reduce levels of operation disruption and allow for stable voltage provision during fault [18]. Typical fault-tolerant systems include real-time switching sequence adjustment and inclusion of spare devices [19]. But these benefits come at the cost of a penalty in terms of increased circuit complexity and higher implementation costs [20]. In most fault-tolerant implementations, two separate DC sources, besides diodes and one-way switches, are utilized in handling gate signal generation. The inverter lowers the output voltage upon occurrence of a fault by switching from five-level to a simpler three-level operation. To compensate for this voltage drop, a transformer is employed to increase the voltage to the required level. The system also monitors so that energy is controlled between the two sources in a manner that it stays balanced and does not have uneven battery utilization

Fig. 1. Conventional Fault Tolerant Five Level Inverter

TABLE II

SWITCHING STATES OF THE FAULT TOLERANT

FIVE-LEVEL INVERTER

| Voltage<br>Level    | S1 | S2 | <b>S3</b> | S4 | <b>S5</b> | <b>S</b> 6 | <b>S</b> 7 |

|---------------------|----|----|-----------|----|-----------|------------|------------|

| $+V_{dc}/2$         | 1  | 1  | 0         | 0  | 0         | 0          | 1          |

| $+V_{dc}/4$         | 0  | 1  | 1         | 0  | 0         | 0          | 1          |

| 0                   | 0  | 1  | 1         | 0  | 1         | 0          | 0          |

| -V <sub>dc</sub> /4 | 0  | 1  | 1         | 0  | 0         | 1          | 0          |

| -V <sub>dc</sub> /2 | 0  | 0  | 1         | 1  | 0         | 1          | 0          |

Volume 13 Issue V May 2025- Available at www.ijraset.com

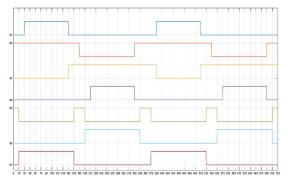

Fig. 2. Control signals for fault tolerant topology

The fault-tolerant NPC inverter adjusts its switching pattern to bypass and isolate faulty components so that the system can continue operating uninterrupted [18]. For instance, when there is an open-circuit (OC) fault in an IGBT, the control logic reallocates gate signals to redistribute voltage levels among the active switches left, thus maintaining balanced output features [19], [20]. With such conditions, the inverter tends to drop back from its conventional five-level to a lowered three-level operation. Although this mode reduces the level of voltage steps available, output is still functioning and stable to some extent.

On the other hand, traditional five-level NPC inverters do not have inherent fault-handling capabilities, and hence, the performance of these inverters degrades during faults. The component failure can cause voltage level imbalances, which have a major impact on Total Harmonic Distortion (THD) in the output. Not only does it reduce the quality of the waveform, but also leads to unstable neutral point voltage, thus weakening the overall system reliability. Further, fault detection and isolation in the inverters is a difficult task because of the complexity of the system and lack of adaptive control.

#### B. Fault-Tolerant Five-Level NPC Inverter with PWM Technique

The five-level Neutral Point Clamped (NPC) inverter is widely used in advanced power systems due to its capability to generate stepped voltage waveforms with improved harmonic performance and efficiency [1], [3]. However, under fault conditions especially in power semiconductor switches or clamping diodes traditional NPC inverters suffer from voltage imbalance, waveform distortion, and increased Total Harmonic Distortion (THD) [13], [15]. For improved fault robustness, enhanced NPC topologies employ redundancy strategies and smart control strategies. When a device is faulty, the inverter reconfigures its switching profile automatically to bypass the faulty device and switch to three-level operating mode to continue power flow [17],[20]. While this results in a decrease in the output voltage, employing a voltage-boosting transformer serves to compensate for the dip and ensure the voltage remains within the specified range.

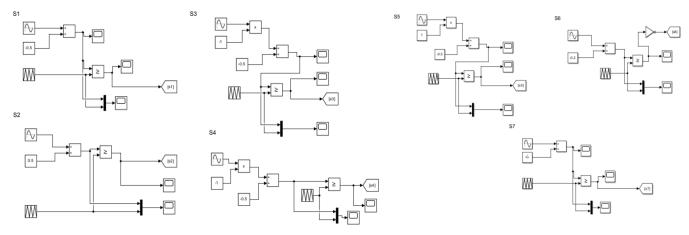

Fig.3. Fault Tolerant Five Level Inverter with PWM Technique

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 13 Issue V May 2025- Available at www.ijraset.com

Fig.4.Gate Driver Circuits

#### III.SIMULATION RESULTS

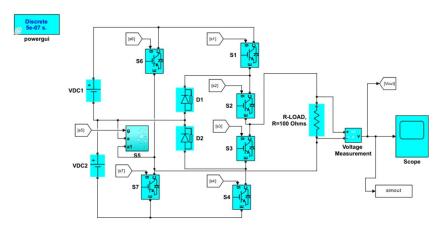

The simulation was performed on MATLAB, and the results are given below.

- A. Conventional Fault Tolerant Five Level NPC inverter

- 1) Without fault

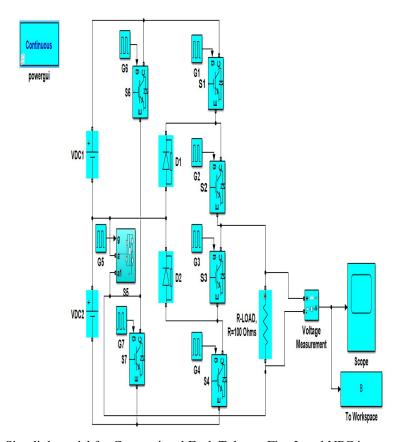

The traditional five-level NPC inverter circuit is shown in Fig. 11.

Fig. 5. Simulink model for Conventional Fault Tolerant Five Level NPC inverter

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 13 Issue V May 2025- Available at www.ijraset.com

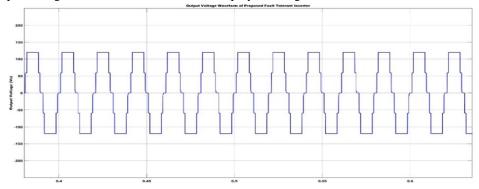

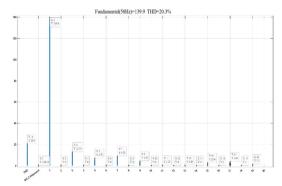

The waveforms of output voltage under no fault scenario are displayed in Fig. 6.

Fig. 6. Output waveforms under no fault condition

Fig. 7. FFT analysis under no fault condition

The harmonic spectrum under no fault conditions is presented in Fig.7, indicating a THD of 20.3%.

#### 2) With fault

Fig.8. Simulink model Conventional Fault Tolerant Five Level NPC inverter with dc1 source failure

Volume 13 Issue V May 2025- Available at www.ijraset.com

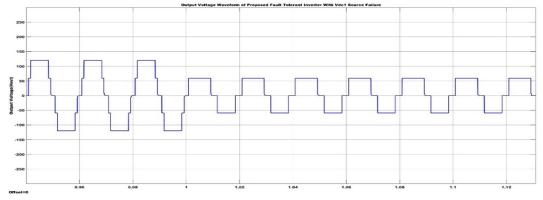

The waveform of output voltage under fault condition are shown in Fig. 9.

Fig. 9. Output waveform in the presence of a fault

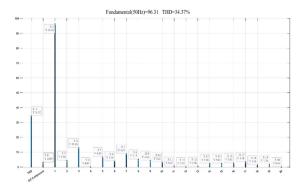

Fig. 10. FFT analysis in the presence of a fault

The harmonic spectrum under fault conditions is presented in Fig. 10, indicating a THD of 34.37%.

- B. Fault Tolerant Five Level NPC inverter with PWM Technique

- 1) Without fault

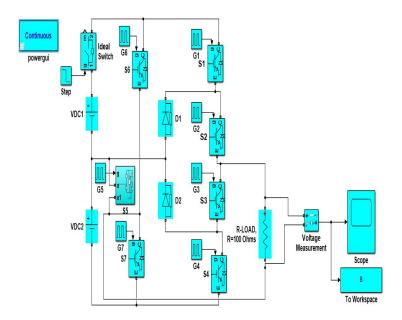

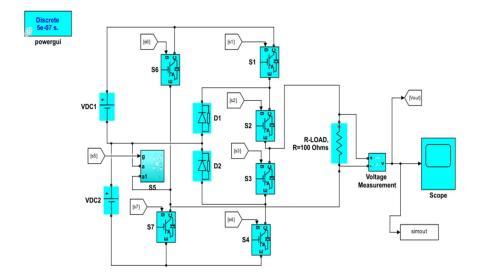

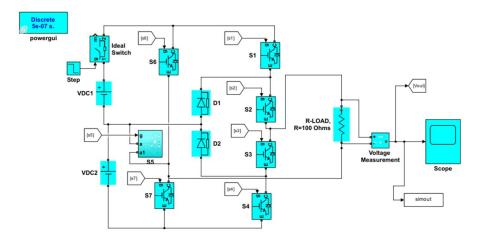

Fig. 11. Simulink model for Fault Tolerant Five Level NPC inverter with PWM Technique

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 13 Issue V May 2025- Available at www.ijraset.com

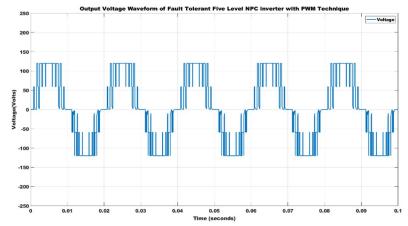

The waveforms of output voltage under no fault scenario are displayed in Fig. 12.

Fig. 12. Output waveforms under no fault condition

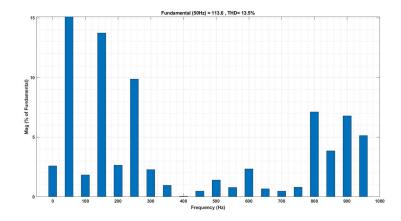

Fig. 13. FFT analysis under no fault condition

The harmonic spectrum under no fault conditions is presented in Fig.13, indicating a THD of 13.5%.

#### 2) With Fault

Fig14. Simulink model Conventional Fault Tolerant Five Level NPC inverter with dc1 source failure

Volume 13 Issue V May 2025- Available at www.ijraset.com

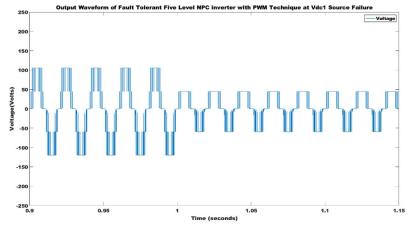

The waveform of output voltage under fault condition are shown in Fig. 15.

Fig. 15. Output waveform in the presence of a fault

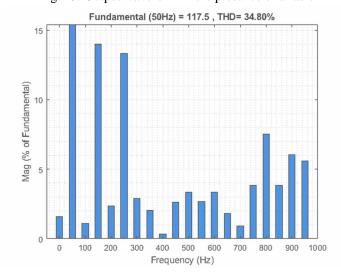

Fig. 16. FFT analysis in the presence of a fault

The harmonic spectrum under fault conditions is presented in Fig. 16, indicating a THD of 34.80%

TABLE III

SUMMARY OF FFT ANALYSIS

| Topology                                                                 | Fundamental<br>Frequency<br>(50) | THD    |

|--------------------------------------------------------------------------|----------------------------------|--------|

| Conventional Fault Tolerant Five Level<br>Inverter                       | 139.9                            | 20.3%  |

| Conventional Fault Tolerant Five Level<br>Inverter with fault condition  | 96.31                            | 34.37% |

| Fault Tolerant Five Level Inverter With PWM Technique                    | 113.6                            | 13.5   |

| Fault Tolerant Five Level Inverter with PWM Technique at fault condition | 117.5                            | 34.80  |

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 13 Issue V May 2025- Available at www.ijraset.com

#### **IV.CONCLUSIONS**

The results clearly demonstrate that traditional fault-tolerant five-level NPC inverters show noticeable performance decline when faults such as switch failures, diode malfunctions, or DC-link imbalances occur. These faults cause increased harmonic distortion, voltage imbalance, and disruption in output waveforms, limiting the reliability of the system in critical applications. On the other hand, the fault-tolerant NPC inverter controlled by PWM succeeded in dealing with fault conditions by adjusting the switching patterns and reassigning voltage levels to operating devices. Simulation and experimental results confirmed that the system guaranteed stability of the waveform, minimized THD, and sustained continuous operation even with hardware faults. This stable operation in tough conditions highlights the inverter's suitability to high-load applications like industrial motor drives and Grid systems. The control strategy, without adding significant hardware complexity, enhances the inverter's reliability and renders it a feasible and efficient.

#### **REFERENCES**

- [1] B. Anil Kumar1, B.Rohith2, P. Karthikeya3, N. Rahul4, T. Murali Krishna5" Comparative Analysis of Conventional and Fault-Tolerant Five-Level NPC Inverters" DOI Link: <a href="https://doi.org/10.22214/ijraset.2025.69755">https://doi.org/10.22214/ijraset.2025.69755</a> Apr 2025.

- [2] J. Rodríguez, J. Lai, and F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724–738, Aug. 2002.

- [3] L. M. Tolbert, F. Z. Peng, and T. G. Habetler, "Multilevel converters for large electric drives," IEEE Trans. Ind. Appl., vol. 35, no. 1, pp. 36–44, Jan.–Feb. 1999. Wikipedia

- [4] B. Wu, "High-Power Converters and AC Drives," Wiley-IEEE Press, 2006.

- [5] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Pérez, "A survey on cascaded multilevel inverters," IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2197–2206, Jul. 2010.

- [6] S. Kouro et al., "Recent advances and industrial applications of multilevel converters," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2553–2580, Aug. 2010.

- [7] P. Lezana, R. Aguilera, and D. E. Quevedo, "Model predictive control of an asymmetric flying capacitor converter," IEEE Trans. Ind. Electron., vol. 56, no. 6, pp. 1839–1846, Jun. 2009.

- [8] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," IEEE Trans. Ind. Appl., vol. IA-17, no. 5, pp. 518-523, Sep. 1981.

- [9] H. Akagi, "Classification, terminology, and application of the modular multilevel cascade converter (MMCC)," IEEE Trans. Power Electron., vol. 26, no. 11, pp. 3119–3130, Nov. 2011.

- [10] J. Holtz, "Pulsewidth modulation for electronic power conversion," Proc. IEEE, vol. 82, no. 8, pp. 1194–1214, Aug. 1994.

- [11] K. Gopakumar, S. K. Sahoo, and B. K. Bose, "A new switching strategy for a three-level inverter," IEEE Trans. Ind. Electron., vol. 44, no. 3, pp. 411–418, Jun. 1997.

- [12] M. Marchesoni and M. Mazzucchelli, "Multilevel converters for high power AC drives: a review," in Proc. IEEE Int. Symp. Ind. Electron., 1993, pp. 38–43.

- [13] E. Babaei, "A cascade multilevel converter topology with reduced number of switches," IEEE Trans. Power Electron., vol. 23, no. 6, pp. 2657–2664, Nov. 2008.

- [14] S. Khomfoi and L. M. Tolbert, "Multilevel power converters," in Power Electronics Handbook, 2nd ed., Elsevier, 2007, pp. 451–482.

- [15] M. F. Escalante, J. C. Vannier, and A. Arzandé, "Flying capacitor multilevel inverters and DTC motor drive applications," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 809–815, Aug. 2002.

- [16] H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, "Medium-voltage multilevel converters—state of the art, challenges, and requirements in industrial applications," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2581–2596, Aug. 2010.

- [17] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu, J. Rodriguez, M. A. Pérez, and J. I. Leon, "Recent advances and industrial applications of multilevel converters," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 255

- [18] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu, J. Rodriguez, M. A. Perez, and J. I. Leon, "Recent Advances and Industrial Applications of Multilevel Converters," IEEE Transactions on Industrial Electronics, vol. 57, no. 8, pp. 2553–2580, Aug. 2010. DOI: 10.1109/TIE.2010.2049719

- [19] R. Teodorescu, F. Blaabjerg, M. Liserre, and P. C. Loh, "Proactive Fault Tolerant Systems with Distributed Power Converters," IEEE Transactions on Power Electronics, vol. 23, no. 5, pp. 2681–2692, Sept. 2008.DOI: 10.1109/TPEL.2008.2002705

- [20] M. Khazraei, M. Ferdowsi, and K. Corzine, "Fault Diagnosis and Fault-Tolerant Control of Multilevel Inverters Using Artificial Neural Networks," IEEE Transactions on Industrial Electronics, vol. 60, no. 6, pp. 2133–2141, June 2013. DOI: 10.1109/TIE.2012.2206361

- [21] Y. Chen and Z. Yuan, "Design and Implementation of a Fault-Tolerant NPC Inverter with Redundant Components," IEEE Transactions on Industrial Electronics, vol. 62, no. 1, pp. 421–429, Jan. 2015. DOI: 10.1109/TIE.2014.2336594

10.22214/IJRASET

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)