# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 12 Issue: VI Month of publication: June 2024

DOI: https://doi.org/10.22214/ijraset.2024.63177

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

Volume 12 Issue VI June 2024- Available at www.ijraset.com

### Design and Analysis of High Gain Dual Stage Opamp in Cadence 180 nm Technology

Aishwarya Chittur<sup>1</sup>, Teja Rapolu<sup>2</sup>, Sangeetha Sahithi .T<sup>3</sup>, Sudhir Dakey<sup>4</sup>

<sup>1, 2, 3</sup>Student, <sup>4</sup>Assistant Professor, Department of Electronics and Communication Engineering, Maturi Venkata Subbarao (MVSR)

Engineering College, Hyderabad, Telangana, India

Abstract: Operational amplifier contains basic current mirror and dual input differential amplifier. Basic Current mirror is an electronic circuit which contains two transistors. The operation of the current mirror is that whenever current is applied to drain of one of the transistors with some magnitude same current will produce at the output of another transistor, hence the name mirror of the input signal. Operational amplifier contains two legs- inverting leg, non- inverting leg. If signals are applied to inverting and non-inverting legs, operational amplifier used as an amplifier and comparator or adder or subtractor. A two stage operational amplifier consists of a differential amplifier at the input stage. While the second stage is a high gain stage biased by the output of differential amplifier.

Keywords: Operational amplifier, current mirror, differential amplifier, inverting, non inverting

#### I. INTRODUCTION

The surface knowledge of the operational amplifier is essential to implement any analog circuit as an amplifier. Differential amplifier play a vital role in operational amplifier, to amplify two differential signals. The differential amplifier is a basic building block of an operational amplifier. The differential amplifier is the first stage, which accurately amplifies the difference between two input signals while rejecting any signals that are common to both inputs. This stage is crucial for achieving high precision in signal amplification. The current mirror, acting as the second stage, ensures consistent current flow within the amplifier circuit. It helps in stabilizing and boosting the gain further, ensuring that the amplifier can handle a wide range of input signals with minimal distortion. Isolation, instrumentation, and fully differential amplifier are the factors which effect differential amplifier classification. Use of differential amplifier is it draws small power during biasing condition.

#### II. LITERATURE SURVEY

- 1) Sachin K Rajput, B K Hemant these authors proposed that designing a two-stage high gain low power Op Amp with current buffer compensation provides stability, higher gain, low power consumption but had demerits like increased complexity, size and area considerations.

- 2) Gaurab Gunjan Pathak, Debajit Das proposed that Design and simulation of a two stage op-amp using DG MOSFET for low power and low voltage amplifications using Double-Gate (DG) MOSFETs has low power consumption, low voltage operation but is sensitive to process variations, has limited bandwidth.

- 3) J.P. Eggermont, B. Gentinne, and D. Flandre proposed that designing a single-stage op-amp design utilizing a basic current mirror and a differential amplifier has merits like high-temperature operation, current mirror usage, single-stage design.

#### III. AIM, OBJECTIVES AND ADDITIVE CIRCUIT

#### A. Aim

The main aim of the project is to design and analyse high gain dual stage operational amplifier.

#### B. Objectives

The objectives of the project are

- 1) To design a dual stage operational amplifier.

- 2) To show that dual stage operational amplifier provides more gain and more gain bandwidth product than a single stage op amp.

- 3) To compare power and enhanced amplification in single stage op amp and dual stage op amp.

- 4) To design integrator as an application

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 12 Issue VI June 2024- Available at www.ijraset.com

#### C. Additive Circuit

The Additive circuit that we are adding to the project is an Integrator. An inverting amplifier whose output voltage is proportional to the negative integral of the input voltage is an Integrator. Output signal magnitude is determined by the length of time a voltage is present at its input as the current through the feedback loop charges or discharges the capacitor as the required negative feedback occurs through the capacitor.

#### IV. SOFTWARE USED

Cadence Virtuoso is a prominent Electronic Design Automation (EDA) solutions provider, offering a comprehensive suite of tools for analog, mixed signal and integrated circuit (IC) design. It provides a suite of tools and features that enable us to process the design from initial schematic capture to final layout and verification.

The Key features of Cadence Virtuoso are Schematic Capture, Layout Editor, Simulation and Analysis, Design and Rue Checking, Physical Verification, Parametric Analysis and Custom Design.

The main Advantages of Cadence Virtuoso over other platforms are:

High precision, Comprehensive toolset and Industry Standard.

#### V. BLOCK DIAGRAMS

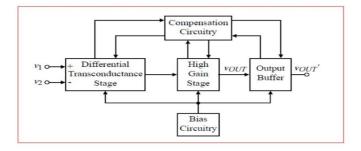

#### A. General Block Diagram of two-stage op amp

Block diagram of a general, two-stage op amp:

Differential Transconductance Stage amplifies the difference between the two input voltages (V1+ and V1-) and converts it in to a current. High Gain Stage further amplifies the current from the differential stage and converts it back to a voltage. The gain of this stage is also typically high, but it's not as high as the gain of the first stage. Compensation Circuitry helps to stabilize the op-amp and prevent it from oscillating. Bias Circuitry provides the DC voltages and currents that are needed to power the op-amp. Output Buffer isolates the output of the op-amp from the load .

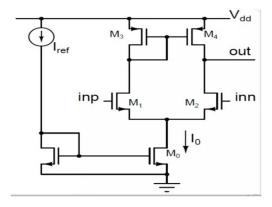

#### B. Single Stage op AMP

Volume 12 Issue VI June 2024- Available at www.ijraset.com

This is a single-stage operational OPAMP amplifier. It has 2PMOS transistors and 4 NMOS transistors. First two NMOS circuit is a basic current mirror. A remaining circuit called a differential amplifier. Differential amplifier contains two legs as a two inputs M1 act as interfered input, if any signal applied across to that input-output signal by an amplifier. If any signal applied to the second leg of the differential amplifier it will produce as comparator output or adder or subtract or output. Hence it will produce differential signal strength at output of the differential amplifier.

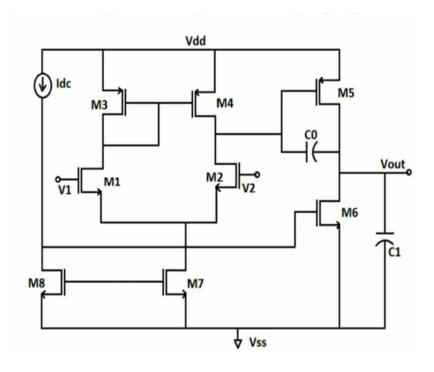

#### C. Dual Stage op AMP

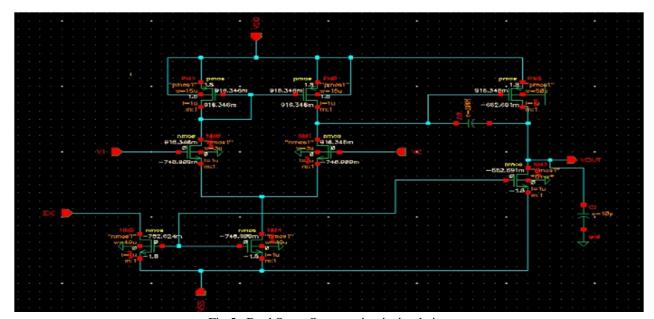

#### 1) First Stage: Differential Amplifier

M1 and M2 are the input transistors forming the differential pair. The differential pair is responsible for amplifying the difference between the input voltages.M3 and M4 are the active load transistors for the differential pair. They act as current sources, providing high impedance which allows for high gain in this stage. Iref is the reference current source that sets the tail current for the differential pair. It defines the amount of current flowing through the differential pair and hence determines the transconductance of M1 and M2.

#### 2) Second Stage: Gain Stage

M5 is a common-source amplifier transistor. It amplifies the signal further from the first stage .C0 is the compensation capacitor used for frequency compensation to ensure stability of the op-amp. It helps to dominate the pole of the frequency response, making the system stable.

#### 3) Output Stage

M6 is the output transistor. It works as a source follower providing a low output impedance which is important for driving the load capacitor .C1: represents the load capacitance which the op-amp will drive. It includes any external load capacitance connected to the output as well as parasitic capacitance.

#### 4) Biasing and Current Mirrors

M7 and M8 transistors are part of the biasing network. They ensure that the proper DC biasing conditions are maintained for the op-amp. M8 is typically used to provide a current mirror configuration to replicate the current from Iref to M5 ensuring the proper current distribution throughout the op-amp

Volume 12 Issue VI June 2024- Available at www.ijraset.com

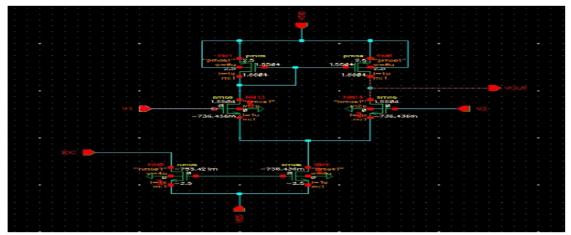

#### VI. SCHEMATIC DESIGN AND SIMULATION RESULTS

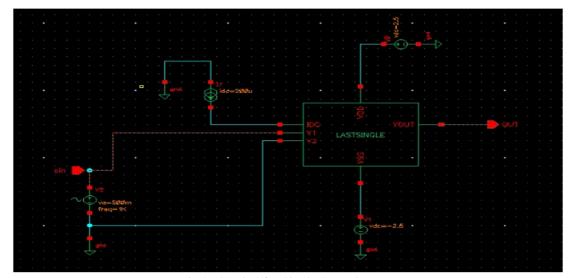

Fig 1 . Single Stage Op-amp circuit simulation

Fig 2. Symbol for Single Stage Op-amp

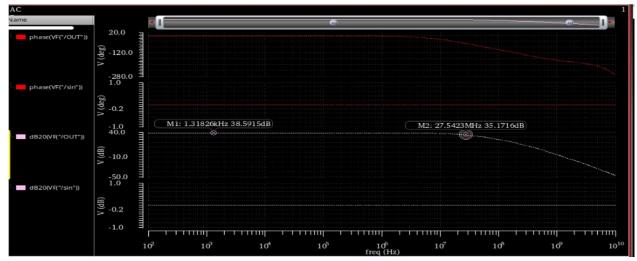

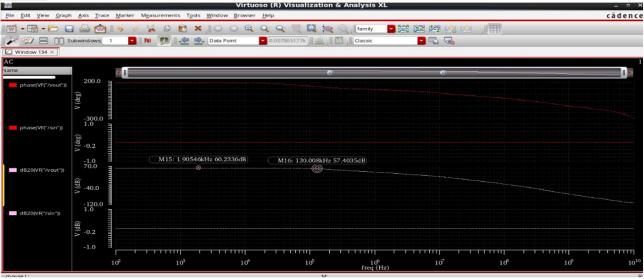

Fig 3. Gain and Gain-Bandwidth product of Single Stage

Volume 12 Issue VI June 2024- Available at www.ijraset.com

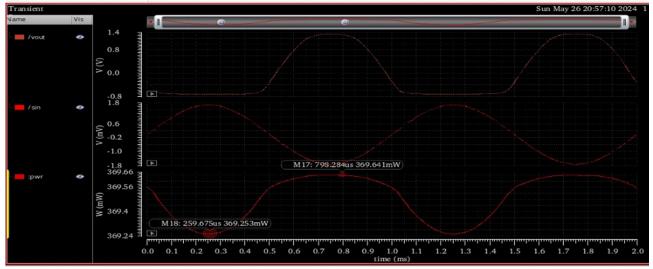

Fig 4 . Static and Dynamic Power of Single Stage Op-amp

Fig 5 . Dual Stage Op-amp circuit simulation

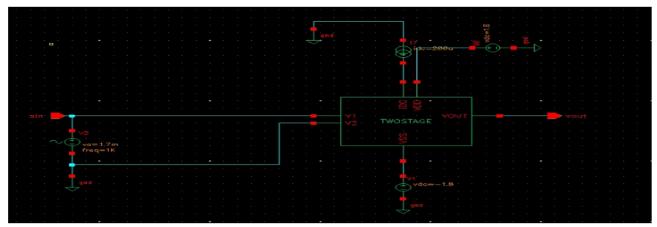

Fig 6 . Symbol for Dual Stage Op-amp

Volume 12 Issue VI June 2024- Available at www.ijraset.com

Fig 7. Gain and Gain-Bandwidth product of Dual Stage

Fig 8. Static and Dynamic Power of Single Stage Op-amp

#### VII. EXPERIMENTAL RESULTS

| S.no |                     | GAIN(dB) | GAIN-BANDWIDTH<br>PRODUCT(Mhz) | POWER(STATIC &<br>DYNAMIC) (mW)     |

|------|---------------------|----------|--------------------------------|-------------------------------------|

| i    | Single Stage Op-amp | 38       | 22                             | 666.846(Static)<br>666.227(Dynamic) |

| ii   | Dual Stage Op-amp   | 60       | 30                             | 369.64(Static)<br>369.25(Dynamic)   |

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 12 Issue VI June 2024- Available at www.ijraset.com

#### VIII. CONCLUSION

We can see from the experimental results the outputs of single stage ,dual stage and integrator. Gain of dual stage (60 dB) greater than single stage (38 dB). Gain bandwidth of dual stage (30Mhz) greater than single stage (22 Mhz). Power of dual stage (369.64mW) less than single stage (666.846mW). Overall amplification of the operational amplifier is increased compared to a single-stage amplifier.

#### IX. FUTURE SCOPE

The future scope of full adders, which are fundamental components in digital electronics, is broad and influenced by several emerging technologies and trends in the field of computing and electronics. Here are some key areas where full adders are likely to see significant developments and applications:

- 1) Advanced Communication Systems

- 2) Internet of Things (IoT)

- 3) Electric Vehicles (EVs)

- 4) Renewable Energy

- 5) Quantum Computing and Advanced Research

#### REFERENCES

- [1] Madhuri Kadam "Dual Stage CMOS Operational Amplifier Design in Sky-Water 130nm Technology" 2021 International Conference on Advances in Computing, Communication, and Control (ICAC3)

- [2] Srilakshmi Ravali Madabhushanam, Lalitha Malladi, Soumya Reddy Gudepu Design High gain dual stage operational amplifier using CMOS 45nm Technology Proceedings of the Fourth International Conference on I SMAC 2020 IEEE.

- [3] M. K. Pandey, S. S. Rajput, "Design of a Low-Voltage Low-Power CMOS Op-Amp with Enhanced Gain for Biomedical Applications," IEEE Trans. Circuits Syst. II, vol. 66, no. 4, pp. 589-593, Apr. 2019.

- [4] Shaik Karimullah, D. Vishnu Vardhan, N.Bala Dastagiri, B.Abdul Rahim,"Design of high gain Low Power Operational Amplifier", International Journal of Advance Trends in Engineering, Science Technology (IJATEST) Volume.4, Special Issue.1Dec.2016

- [5] LeYe, Congyin Sh"Highly Power-Efficient Active-RC Filters With Wide Bandwidth-Range Using Low-Gain Push-Pull Opamps" IEEE Transactions on Circuits and Systems -I (January 2013).

- [6] Santosh Kumar Gupta, Gaurab Gunjan Pathak, DebajitDas and Chandan Sharma, "Design and simulation of a two stage op-amp using DG MOSFET for Low Power and Low Voltage Amplifications," International Journal of Wisdom Based Computing, Vol1 (3), Dec 2011. IEEE. 22

- [7] D. Grasso, D. Marano, G. Palumbo, S. Pennisi et al, "Improved reversed nested Miller frequency compensation technique with voltage buffer and resistor," IEEE Trans. Circuits Syst Express Briefs, vol. 54,no. 5, pp. 382–386,published on May 2007.

- [8] High-Gain and High-Slew-Rate Two-Stage Class A-AB Op Amp- Google Scholar.

- [9] A dual-supply two-stage CMOS op-amp for high-speed pipeline ADCs application- Google Scholar.

10.22214/IJRASET

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)