IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 10 Issue: IX Month of publication: September 2022 DOI: https://doi.org/10.22214/ijraset.2022.46620

www.ijraset.com

Call: 🕥 08813907089 🔰 E-mail ID: ijraset@gmail.com

# Design of Power and Area Efficient Approximate Multipliers for Edge Detection Algorithm

Nanammal.V<sup>1</sup>, Neha Gangrade<sup>2</sup>

<sup>1</sup>Asst.Professor, Department of Electronics and Communication Engineering, Jeppiaar Engineering College, Chennai – 600119. <sup>2</sup>P G Scholar, Department of VLSI Design, Jeppiaar Engineering College, Chennai – 600119.

Abstract: In this paper, we present a novel approximate computing scheme suitable for realizing the energy-efficient multiplyaccumulate (MAC) processing. First we design the approximate 4-2 compressors generating errors in the opposite direction while minimizing the computational costs. Based on the probabilistic analysis, positive and negative multipliers are then carefully developed to provide a similar error distance. Simulation results on various practical applications reveal that the proposed MAC processing offers the energy-efficient computing scenario by extending the range of approximate parts. This Design is implemented by Verilog HDL and simulated by Modelsim 6.4 c. The Performance is measured by Xilinx tool Synthesis Process. The proposed Sobel edge detection algorithm uses approximation methods to replace the complex operations; This design is done by Matlab and Modelsim using hdldameon, This proposed multipliers arerpelaced in the sobel operator based image Edge detection.

# I. INTRODUCTION

In applications like multimedia signal processing and data mining which can tolerate error, exact computing units are not always necessary. They can be replaced with their approximate counterparts. Research on approximate computing for error tolerant applications is on the rise. Adders and multipliers form the key components in these applications. In approximate full adders are proposed at transistor level and they are utilized in digital signal processing applications. Their proposed full adders are used in accumulation of partial products in multipliers. To reduce hardware complexity of multipliers, truncation is widely employed in fixed-width multiplier designs. Then a constant or variable correction term is added to compensate for the quantization error introduced by the truncated part. Approximation techniques in multipliers focus on accumulation of partial products, which is crucial in terms of power consumption. Broken array multiplier is implemented, where the least significant bits of inputs are truncated, while forming partial products to reduce hardware complexity. The proposed multiplier saves few adder circuits in partial product accumulation. Two designs of approximate 4-2 compressors are presented and used in partial product reduction tree of four variants of  $8 \times 8$  Array multiplier. The major drawback of the proposed compressors is that they give nonzero output for zero valued inputs, which largely affects the mean relative error (MRE) as discussed later. The approximate design proposed in this brief overcomes the existing drawback. This leads to better precision. In static segment multiplier (SSM) proposed, m-bit segments are derived from n-bit operands based on leading 1 bit of the operands. Then, m  $\times$  m multiplication is performed instead of n  $\times$  n multiplication, where m<n. Partial product perforation (PPP) multiplier omits k successive partial products starting from jth position, where  $j \in [0, n-1]$  and  $k \in [1, min(n-j, n-1)]$  of a n-bit multiplier. In [8],  $2 \times 2$  approximate multiplier based on modifying an entry in the Karnaugh map is proposed and used as a building block to construct  $4 \times 4$  and  $8 \times 8$  multipliers. In [9], inaccurate counter design has been proposed for use in power efficient Wallace tree multiplier. A new approximate adder is presented which is utilized for partial product accumulation of the multiplier. For 16-bit approximate multiplier 26% of reduction in power is accomplished compared to exact multiplier. Approximation of 8-bit Wallace tree multiplier due to voltage over-scaling (VOS) is discussed. Lowering supply voltage creates paths failing to meet delay constraints leading to error. Previous works on logic complexity reduction focus on straightforward application of approximate adders and compressors to thepartial products. In this brief, the partial products are altered to introduce terms with different probabilities. Probability statistics of the altered partial products are analyzed, which is followed by systematic approximation. Simplified arithmetic units (half-adder, full-adder, and 4-2 compressor) are proposed for approximation. The arithmetic units are not only reduced in complexity, but care is also taken that error value is maintained low. While systemic approximation helps in achieving better accuracy, reduced logic complexity of approximate arithmetic units consumes less power and area. The proposed multipliers outperforms the existing multiplier designs in terms of area, power, and error, and achieves better peak signal to noise ratio (PSNR) values in image processing application.

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue IX Sep 2022- Available at www.ijraset.com

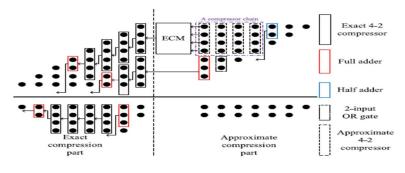

# II. PROPOSED MULTIPLIER BLOCK DIAGRAM

Three approximate 4-2 compressors (UCAC1, UCAC2, and UCAC3) are proposed in this section. Then, the ECM is presented to detect an input pattern with a large probability and correct the erroneous compensation in this case. Furthermore, the proposed designs are embedded in 8-bit multipliers based on the partial product tree. And all the analyses are performed with the uniform distribution. The proposed approximate compressors and ECM are designed to simplify and accelerate the compression process, four 8-bit multipliers (N = 8) are designed to evaluate these blocks, accordingly.

- 1) MUL1: Multiplier with UCAC1 and Constant Correcting Bit;

- 2) MUL2: multiplier with UCAC1 and ECM;

- *3) MUL3:* multiplier with UCAC2 and EC

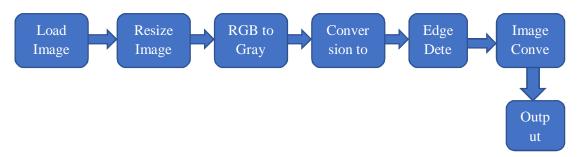

#### III. SOBEL EDGE DETECTION BLOCK DIAGRAM

Edge detection algorithms are widely used in various research fields like Image Processing, Video Processing and Artificial Intelligence etc. Edges are most important attribute of image information, and a lot of edge detection algorithms are defined in literature. Sobel edge detection algorithm is chosen among of them due to its property of less deterioration in high level of noise. FPGA is becoming the most dominant form of programmable logic over past few years and it has advantages of low investment cost and desktop testing with moderate processing speed and thereby offering itself as suitable one for real time application. This paper describes an efficient architecture for Sobel edge detector which is faster and takes less space than the Existing architecture.

### IV. SOBEL EDGE DETECTION

Algorithm for Sobel Edge Detection The Sobel Edge Detection Operator is  $3\times3$  spatial mask. It is based on first derivative-based operation. The Sobel masks are defined as:

| -1     | -2 | -1 | -1             | 0 | 1 |

|--------|----|----|----------------|---|---|

| H1 = 0 | 0  | 0  | (1) $H_2 = -2$ | 0 | 2 |

| 1      | 2  | 1  | -1             | 0 | 1 |

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue IX Sep 2022- Available at www.ijraset.com

Suppose the pixel value of a  $3 \times 3$  sub-window of an image is as shown as in Table

| D0 | D1 | D2 |

|----|----|----|

| D3 | D4 | D5 |

| D6 | D7 | D8 |

The pixel intensity values of a 3×3 sub-window of an image applying the Sobel mask on the sub-window of Fig. 1 yields

$$G_x = (D6 + 2 \times D7 + D8) - (D0 + 2 \times D1 + D2)$$

= f1 - f2 Where, f1 = (D6 + 2 × D7 + D8) and f2 = (D0 + 2 × D1 + D2)

$$G_y = (D2 + 2 \times D5 + D8) - (D0 + 2 \times D3 + D6)$$

= f3 - f4 Where, f3 = (D2 + 2 × D5 + D8) and f4 = (D0 + 2 × D3 + D6)

#### V. RESULTS AND DISCUSSION

A. MAC Design using Proposed Compressor

| Messages                                             |                  |                  |        |        |        |        |        |        |        |        |      |      |         |  |

|------------------------------------------------------|------------------|------------------|--------|--------|--------|--------|--------|--------|--------|--------|------|------|---------|--|

| /MAC_Unit_Multiplier_by_Compressor/Clk               | St0              |                  |        |        |        |        |        |        |        |        |      |      |         |  |

| /MAC_Unit_Multiplier_by_Compressor/Rst               | St0              |                  |        |        |        |        |        |        |        |        |      |      |         |  |

| + <> /MAC_Unit_Multiplier_by_Compressor/Multiplier   | 42               | 42               |        |        |        |        |        |        |        |        |      |      |         |  |

| + <> /MAC_Unit_Multiplier_by_Compressor/Multiplicant | 10               | 10               |        |        |        |        |        |        |        |        |      |      |         |  |

| + <> /MAC_Unit_Multiplier_by_Compressor/Acc_Out      | 420              | 0                | 420    | 840    | 1260   | 1680   | 2100   | 2520   | 2940   | 3360   |      |      |         |  |

| + <> /MAC_Unit_Multiplier_by_Compressor/Mul_Result   | 420              | 420              |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/Adder_R            | 0000001101001000 | 0000000110100100 | 000000 | 000001 | 000001 | 000010 | 000010 | 000010 | 000011 | 000011 |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/A              | 00101010         | 00101010         |        |        |        |        |        |        |        |        |      |      |         |  |

| #/MAC_Unit_Multiplier_by_Compressor/MM0/B            | 00001010         | 00001010         |        |        |        |        |        |        |        |        |      |      |         |  |

| /MAC_Unit_Multiplier_by_Compressor/MM0/Pro           | 0000000110100100 | 0000000110100100 |        |        |        |        |        |        |        |        |      |      |         |  |

|                                                      | 00000000         | 00000000         |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/PP1            | 00101010         | 00101010         |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/PP2            | 00000000         | 00000000         |        |        |        |        |        |        |        |        |      |      |         |  |

| #                                                    | 00101010         | 00101010         |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/PP4            | 0000000          | 0000000          |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/PP5            | 0000000          | 0000000          |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/PP6            | 0000000          | 0000000          |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/PP7            | 0000000          | 0000000          |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/Mai            | 00101010         | 00101010         |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/Mai            | 00001010         | 00001010         |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/Mai            | 0000000          | 0000000          |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/Mai            | 00101010         | 00101010         |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/Mai            | 0000000          | 0000000          |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/Mai            | 00101010         | 00101010         |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/Mai            | 0000000          | 0000000          |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/Mai            | 0000000          | 0000000          |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/Mai            | 0000000          | 0000000          |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/Mai            | 0000000          | 0000000          |        |        |        |        |        |        |        |        |      |      |         |  |

| MAC_Unit_Multiplier_by_Compressor/MM0/Mai            | 00101010         | 00101010         |        |        |        |        |        |        |        |        |      |      |         |  |

| Δ MΔC Unit Multiplier by Compressor/MM0/Mai          | SHO              |                  |        |        |        |        |        |        |        |        |      | <br> | <br>    |  |

| Now                                                  | 1100 ps          | ps 200 ps        | 40     | ps     | 600    |        |        | ) ps   | 1000   |        | 1200 | 1400 | 1600 ps |  |

|                                                      | 396 ps           |                  | 396    | 5 ps   |        |        |        |        |        |        |      |      |         |  |

B. Device Utilization Summary of Normal Multiplier MAC Design

| Device Utilization Summary                     |       |           |             |         |  |  |  |  |

|------------------------------------------------|-------|-----------|-------------|---------|--|--|--|--|

| Logic Utilization                              | Used  | Available | Utilization | Note(s) |  |  |  |  |

| Number of Slice Flip Flops                     | 16    | 3,840     | 1%          |         |  |  |  |  |

| Number of 4 input LUTs                         | 246   | 3.840     | 6%          |         |  |  |  |  |

| Logic Distribution                             |       |           |             |         |  |  |  |  |

| Number of occupied Slices                      | 134   | 1,920     | 6%          |         |  |  |  |  |

| Number of Slices containing only related logic | 134   | 134       | 100%        |         |  |  |  |  |

| Number of Slices containing unrelated logic    | 0     | 134       | 0%          |         |  |  |  |  |

| Total Number of 4 input LUTs                   | 246   | 3,840     | 6%          |         |  |  |  |  |

| Number of bonded <u>IOBs</u>                   | 34    | 97        | 35%         |         |  |  |  |  |

| Number of GCLKs                                | 1     | 8         | 12%         |         |  |  |  |  |

| Total equivalent gate count for design         | 1,616 |           |             |         |  |  |  |  |

| Additional JTAG gate count for IOBs            | 1,632 |           |             |         |  |  |  |  |

Volume 10 Issue IX Sep 2022- Available at www.ijraset.com

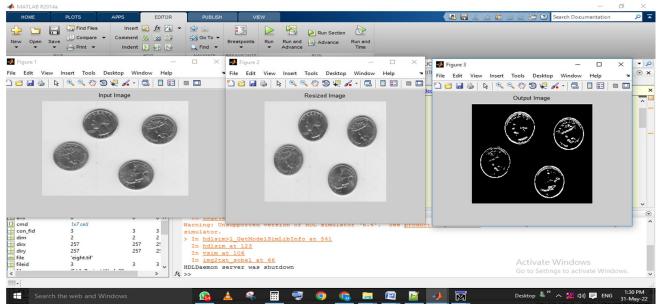

C. Final Output

#### REFERENCES

- [1] P. N. Whatmough, S. K. Lee, H. Lee, S. Rama, D. Brooks, and G.-Y. Wei, "14.3 A 28 nm SoC with a 1.2 GHz 568 nJ/prediction sparse deep-neural-network engine with >0.1 timing error rate tolerance for IoT applications," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2017, pp. 242–243.

- [2] V. Gupta, D. Mohapatra, A. Raghunathan, and K. Roy, "Low-power digital signal processing using approximate adders," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 32, no. 1, pp. 124–137, Jan. 2013.

- [3] M. Kazhdan, "An approximate and efficient method for optimal rotation alignment of 3D models," IEEE Trans. Pattern Anal. Mach. Intell., vol. 29, no. 7, pp. 1221–1229, Jul. 2007.

- [4] M. J. Wainwright and M. I. Jordan, "Log-determinant relaxation for approximate inference in discrete Markov random fields," IEEE Trans. Signal Process., vol. 54, no. 6, pp. 2099–2109, Jun. 2006.

- [5] J. Jo, J. Kung, and Y. Lee, "Approximate LSTM computing for energy efficient speech recognition," Electronics, vol. 9, no. 12, p. 2004, Nov. 2020.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)