# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 10 Issue: IV Month of publication: April 2022

DOI: https://doi.org/10.22214/ijraset.2022.41437

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

Volume 10 Issue IV Apr 2022- Available at www.ijraset.com

### Physical Design of VCO with Wide Frequency Tuning Range Using Deep Submicron CMOS Technology

Amol Nakhale<sup>1</sup>, Prof. M. N. Thakare<sup>2</sup>, Dr. N. M. Chore<sup>3</sup>

<sup>1, 2, 3</sup>Department of VLSI, Department of Electronics & Telecommunication Engineering, Bapurao Deshmukh College of Engineering, Sewagram, Wardha – 442 102 (M.S.)

Abstract: This paper presents a new design approach of CMOS voltage controlled oscillator (VCO) with low power and wide frequency tuning range. A novel current starved delay cell has been proposed based on dual delay path architecture. The results have been obtained in 45 nm CMOS technology with supply voltage 1 V. The proposed VCO achieves a controllable frequency range from 1.81 GHz to 10.55 GHz with a wide tuning range. The control voltage (Vctrl) has been varied from 0.3V to 1V for obtaining the different output frequencies. The power dissipation of proposed VCO is 34.932 uW with current consumption as 0.079 mA at a control voltage of 1V and very optimised surface area as 14.8µm2.

Keywords: Current starved delay cell, Low Power, Tuning range, VCO, etc.

#### I. INTRODUCTION

The voltage-controlled oscillator (VCO) is very useful in applications such as: analog-to-digital converters [1] [2], phase-locked loops [3], and it continues. In last three decades, the high speed and low power consumption are the major design consideration in portable electronic devices.

Voltage Controlled Oscillator (VCO) is an oscillator whose output frequency can be varied over a range and can be controlled by the input DC voltage. The output frequency of VCO may vary from a few hertz to GHz, depending on the design of the VCO. The period of oscillator is equal to the product of the number of stages and delay of each inverter [4]. The delays can be controlled using two ways, capacitance and current of the device. With changing length of transistor technology, capacitance can be altered to observe change in frequency but at a current existing application requires to have one stable single channel length, hence the inverter current is altered. Connecting a trail of the inverter blocks with a feedback gives a 'Ring' configuration to the oscillator. Furthermore, biasing circuit is included in the design to introduce the control voltage into the oscillator for control over frequency of oscillations. Hence, it's called Ring VCO [4].

Another VCO architecture is an improved version of Ring VCO, called Current Starved VCO. The operation is similar to Ring VCO with additional MOS transistors are added so as to operate as current sources with the MOS transistors that operate as inverter. This technique is known as current starving. The current source produces control current to lower the threshold voltage of inverter transistors, which increases the effective drive resistance and thus increases the delay [3].

The desired considerations in designing a VCO is associated to accomplish low power consumption, minimum layout area, high frequency and wide control tuning and voltage range. These target specifications become very difficult to achieve due to the continuous down scaling of silicon CMOS technologies [10]. Now a days, designing a VCO in a ring topology is frequently a more attractive alternative because it allows accomplishing a wide tuning (control voltage) range, small layout area, high gain, low cost, robustness to variations, simplicity and scalability in nanoscale CMOS processes [7] [8]. As we know that, CMOS technology shrinking with time and shifting towards nanometer feature sizes which interconnect in the order of delays and leakage power, dominating gate delays and dominating power. High performance and low power circuit design face many challenges [7] [8] [10].

A voltage control oscillator can be design by using different technique but the most efficient technique is to use the ring oscillator, as ring oscillators are very small in size & compatible with digital circuitry. Hence the VCO design by using ring oscillators makes them ideally suited to provide clocks for systems. The oscillation frequency F\_osc of a VCO can be evaluated by,

$$F\_osc = \frac{1}{2N \, Stages \, tD}$$

$$F_{osc} = \frac{ID}{2N \, Stages \, CG \, Vth}$$

Volume 10 Issue IV Apr 2022- Available at www.ijraset.com

Where, ID is drain current, N indicates the number of stages and t is a time constant that depends on the associated resistance of the active load and the value of the capacitor load [5]. F\_osc varies in a range determined by a control voltage Vctrl, and depends on the number of CMOS differential stages N, but decreasing N yields a reduction in gain, which may result in the oscillation mitigation [1] [2] [5].

This paper proposed a physical design of current starved VCO using CMOS 45nm technology with BSIM 4 MOS modelling technique considering low power design with wide tuning range of frequency. The proposed VCO is simulated to Monte Carlo simulations and power dissipations variations for random variables. The analysis is repeated 50 times and the effect of the same is varied on the power dissipation is verified. This analysis will show the behavior of proposed VCO to robust.

#### II. PROPOSED DESIGN OF VCO

A voltage-controlled oscillator (VCO) is an electronic oscillator designed to be controlled in oscillation frequency by a voltage input. The VCO generates a clock with a controllable Frequency. The VCO is commonly used for clock generation in phase lock loop circuits. The clock may vary typically by  $\pm -50\%$  of its central frequency. The proposed typical transistor sizing with respect to Width and Length is given in the table below considering the current of each transistor.

| Tuble 1. Troposed Transistor Sizing |           |            |                   |           |            |

|-------------------------------------|-----------|------------|-------------------|-----------|------------|

| Transistor (PMOS)                   | Width (W) | Length (L) | Transistor (NMOS) | Width (W) | Length (L) |

| P1                                  | 0.240 um  | 0.040 um   | N1                | 0.200 um  | 0.340 um   |

| P2                                  | 0.440 um  | 0.040 um   | N2                | 0.200 um  | 0.040 um   |

| P3                                  | 0.440 um  | 0.040 um   | N3                | 0.200 um  | 0.040 um   |

| P4                                  | 0.440 um  | 0.040 um   | N4                | 0.200 um  | 0.040 um   |

| P5                                  | 0.440 um  | 0.040 um   | N5                | 0.200 um  | 0.040 um   |

| P6                                  | 0.440 um  | 0.040 um   | N6                | 0.200 um  | 0.040 um   |

Table 1: Proposed Transistor sizing

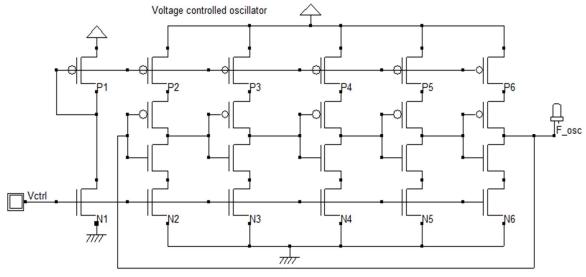

The current-starved inverter chain uses a voltage control 'Vctrl' to modify the current that flows in the N1, P1 branch. The current through N1 is mirrored by N2, N3, N4, N5 and N6. The some current flows in P1. The current Through P1 is mirrored by P2, P3 and P4. Consequent by the change in 'Vctrl' induces a global change in the inverter currents and acts directly on the delay. The figure 1 shows the schematic design of VCO using 45 nm technology. It is a transistorized design where 'Vctrl' is a controlling input and 'F\_osc' is the output.

Figure 1: Schematic design of VCO

Volume 10 Issue IV Apr 2022- Available at www.ijraset.com

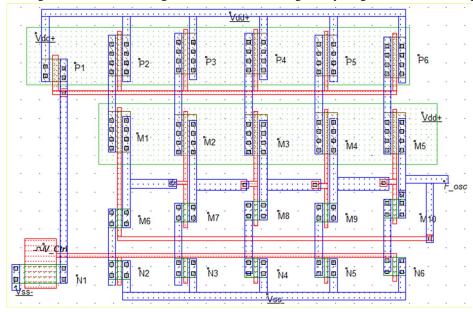

The VCO design is based on an inverter type ring oscillator supplied by a current coming from the voltage to current converter [5]. The VCO consists of five-stage fully differential delay cells performing full switching. Phase noise [5], tuning range, power consumption and device size are the main areas to be considered while designing any VCO circuit. Nowadays, the VCO designs are made in such a way that greater emphasis is on reducing power consumption, so it is difficult to achieve low phase noise and wide tuning range because of more emphasis on the low-power VCO designs [15]. The physical design of VCO is drawn using Microwind EDA Layout editing tool and verified using BSIM4 MOS Modelling for layout guidelines with Design Rule Check.

Figure 2: Physical design of VCO

#### III. RESULT AND DISCUSSSION

The proposed Current Starved ring VCO is simulated using Microwind software CMOS 45nm technology with control voltage variation from 0.1V to 1V.

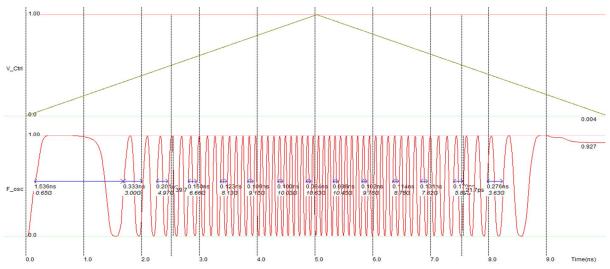

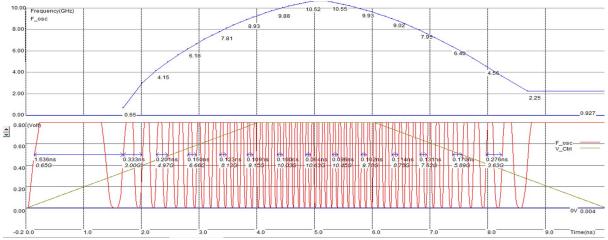

Figure 3: Transient analysis for voltage of VCO

The figure 3 shows the transient analysis of VCO. From the simulation it is clear that VCO starts oscillating with increase in frequency as the Vctrl starts increasing. The power dissipation of proposed VCO is 34.932 uW with current consumption as 0.079 mA at a control voltage of 1V.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue IV Apr 2022- Available at www.ijraset.com

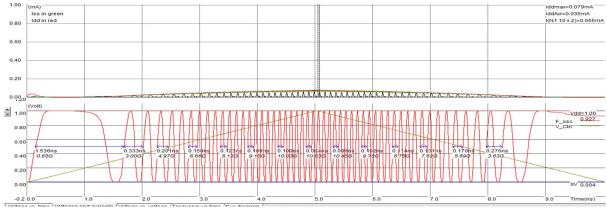

Figure 4: Transient analysis for current of VCO

We chose to modify Vctrl very slowly, in order to see the influence on the oscillations. We put Control higher than 0.5 V, because there are no any oscillations under that value. The proposed VCO achieves a controllable frequency range from 1.81 GHz to 10.55 GHz. VCO starts oscillating with 0.65GHz and maximum frequency is 10.55GHz.

Figure 5: AC analysis of VCO

For observing the performance and stability of the proposed VCO, there is variation of supply VDD from 0.3V to 1V, the output frequency VCO increases with the increase supply voltage linearly. It proves the high stability of the VCO. The result shows the linear increase in Frequency with respect to increase in control voltage.

Table 2: Simulation results of VCO with respect to change in control voltage

|                         | VDD=1 V          |                   |  |

|-------------------------|------------------|-------------------|--|

| Control Voltago (Vatrl) | Output Frequency | Power Dissipation |  |

| Control Voltage (Vctrl) | (F_osc)          |                   |  |

| 0.3 V                   | 1.81 GHz         | 13.226 uW         |  |

| 0.4 V                   | 3.78 GHz         | 25.151 uW         |  |

| 0.5 V                   | 5.60 GHz         | 35.529 uW         |  |

| 0.6 V                   | 7.13 GHz         | 44.382 uW         |  |

| 0.7 V                   | 8.42 GHz         | 52.081 uW         |  |

| 0.8 V                   | 9.45 GHz         | 58.655 uW         |  |

| 0.9 V                   | 10.21 GHz        | 63.785 uW         |  |

| 1.0 V                   | 10.76 GHz        | 67.797 uW         |  |

|                         |                  |                   |  |

Volume 10 Issue IV Apr 2022- Available at www.ijraset.com

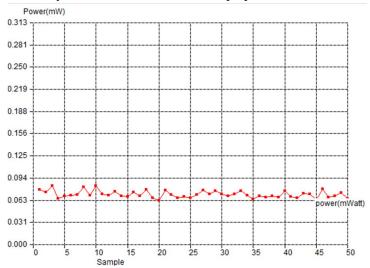

Monte Carlo analysis is an integrated circuit's statistical analysis in which a circuit devices parameters and mismatch are varied randomly. Monte Carlo simulation allows the designer to consider the possible effects of a random variation of certain circuit's parameter over its performance [16]. Monte Carlo analysis is carried out through the variation of Width (W) and Length (L) for each one of the 30 feasible solutions over many runs. The outcome of the Monte Carlo simulations is employed to compute the mean and the standard deviation of the objective function value [7] [16]. The proposed CMOS VCO is simulated to Monte Carlo simulations and power dissipations variations for 30 feasible random variables. The analysis is repeated 50 times and the effect of the same is varied on the power dissipation. This analysis will show the behaviour of proposed VCO to robust.

Figure 6: Monte Carlo simulation for VCO

Monte Carlo analysis is performed on the proposed VCO design. The analysis is repeated 50 times and the effect of the same is varied on the power dissipation is verified. Simulation result is shown in figure 6. From the simulations, the power dissipation ranges between 0.063mW to 0.085 mW.

#### IV. CONCLUSION

The proposed structure of the VCO is designed using current starved ring path techniques to achieve high oscillation frequency and a wide tuning range. VCO achieves a controllable frequency range from 0.65 GHz to 10.55 GHz with a very wide frequency tuning range with the variation in control voltage from 0.1V to 1V keeping supply voltage at 1V. The proposed VCO dissipates a power of 34.932 uW with current consumption as 0.079 mA at a control voltage of 1V and very optimized surface area as 14.8µm2.at a control voltage of 1V. The result shows the linear increase in Frequency with respect to increase in control voltage. The Monte Carlo analysis is performed on the proposed VCO design provided the robust nature of proposed design.

The proposed VCO design has been compared with previously reported design and the present approach shows significant power saving with high oscillation frequency.

#### REFERENCES

- [1] Tamimi, K.M.; El-Sankary, K.; Fouzar, Y., "VCO-Based ADC with Built-In Supply Noise Immunity Using Injection-Locked Ring Oscillators", IEEE Trans. Circuits Syst. Express Briefs 2019, 66, 1089–1093.

- [2] Sharma, J.; Krishnaswamy, H., "A 2.4-GHz Reference-Sampling Phase-Locked Loop That Simultaneously Achieves Low-Noise and Low-Spur Performance", IEEE J. Solid State Circuits 2019, 54, 1407–1424

- [3] Jacob Baker, Harry W. Li and David E. Boyce, "CMOS Circuit Design, Layout and Simulation", IEEE Press Series on Microelectronics Systems, pg. 355-361 and pg.551-612, 2000.

- [4] Danesh, M.; Sanyal, "A. 0.13 pW/Hz Ring VCO-Based Continuous-Time Read-Out AD for Bio-Impedance Measurement", IEEE Trans. Circuits Syst. II Express Briefs 2020.

- [5] Pieter A. J. Nuyts, Patrick Reynaert, Wim Dehaene, "Continuous-Time Digital Front-Ends for Multistandard Wireless Transmission", Springer International Publishing, ISBN: 978-3-319-03925-1, Chapter 4, pg. 143-146.

- [6] Gui, X.; Green, M.M., "Design of CML ring oscillators with low supply sensitivity", IEEE Trans. Circuits Syst. Regul. Pap. 2013, 60, 1753–1763.

- [7] Zhang, Z.; Chen, L.; Djahanshahi, H., "A SEE Insensitive CML Voltage Controlled Oscillator in 65 nm CMOS", In Proceedings of the 2018 IEEE Canadian Conference on Electrical & Computer Engineering (CCECE), Quebec City, QC, Canada, 13–16 May 2018; pp. 1–4.

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue IV Apr 2022- Available at www.ijraset.com

- [8] Prof. Sandeep K. Shelke, Prof. Priti J. Rajput, Prof. Santosh Bari, "Implementation & Comparison of Different oscillators for ISM and WI -FI Band Applications", IEEE 2017 11th International Conference on Intelligent Systems and Control (ISCQ)

- [9] Kavyashree K, Chandana D S, Pruthvi Raj Anantharam Bhat, Sangeetha B G, "Design and Analysis of Voltage Controlled Oscillators in 45nm CMOS Process", Second International Conference on Innovative Mechanisms for Industry Applications (ICIMIA 2020) IEEE Xplore Part Number: CFP20K58-ART; ISBN: 978-1 7281-4167-1

- [10] Abdul Majeed K.K, Binsu J Kailath, "CMOS Current Starved Voltage Controlled Oscillator Circuit for a Fast Locking PLL", IEEE INDICON 2015 1570186537

- [11] Luciano Severino de Paula1, Sergio Bampi2, Eric Fabris1, Altamiro Amadeu Susin, "A Wide Band CMOS Differential Voltage Controlled Ring Oscillator", 978-1-4244-2332-3/08/\$25.00 © 2008 IEEE

- [12] Sandhiya S., Revathi.S, Dr. B. Vinothkumar, "Design of Voltage Controlled Oscillator in 180 nm CMOS Technology", International Research Journal of Engineering and Technology (IRJET)

- [13] Pankaj A. Manekar, Prof. Rajesh H. Talwekar, "Design of Low Phase Noise Ring VCO in 45NM Technology" International Journal of Scientific & Engineering Research, Volume 4, Issue 6, June-2013

- [14] G. Jovanovi'c, M. Stoj'cev, Z. Stamenkovic, "A CMOS Voltage Controlled Ring Oscillator with Improved Frequency Stability", SCIENTIFIC PUBLICATIONS OF THE STATE UNIVERSITY OF NOVI PAZAR

- [15] Mrs. Devendra Rani, Prof. Sanjeev M. Ranjan, "A Voltage Controlled Oscillator using Ring Structure in CMOS Technology", International Journal of Electronics and Computer Science Engineering

- [16] Perla Rubi Castañeda-Aviña 1, Esteban Tlelo-Cuautle 1 and Luis Gerardo de la Fraga, "Single-Objective Optimization of a CMOS VCO Considering PVT and Monte Carlo Simulations", Math. Comput. Appl. 2020, 25, 76; doi:10.3390/mca25040076

- [17] Swati Gulhane, Sujata Kadam, "Design of CMOS based VCO for PLL with improved Frequency Range", INTERNATIONAL JOURNAL FOR ADVANCE RESEARCH IN ENGINEERING AND TECHNOLOGY

- [18] Mr. Jayant P. Sakurikar, Asst. Prof. Divyanshu Rao, Prof. Ravi Mohan, "Design and Performance Analysis of LC Oscillator and VCO for ISM and WI-FI Band Applications", International Journal Of Engineering And Computer Science ISSN: 2319-7242 Volume 4 Issue 6 June 2015, Page No. 12624-12628

- [19] Prof. Seema Zanje, "Design of LC Oscillator and VCO for ISM and WI-FI Band Applications", International Journal of Innovative Research in Engineering & Management (IJIREM) Volume-1, Issue-3, November-2014

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)