# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 12 Issue: VI Month of publication: June 2024

DOI: https://doi.org/10.22214/ijraset.2024.63098

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

Volume 12 Issue VI June 2024- Available at www.ijraset.com

### Flipped Voltage Follower based LDOs for Precise Clocking Circuits: A Comparative Study

Chinmay D Hegde<sup>1</sup>, Vishnu Sai Jayam<sup>2</sup>, Prakash Chand Kuve<sup>3</sup>, Dr. Srividya P<sup>4</sup>

<sup>01, 2, 4</sup>Dept. of ECE, R V College of Engineering, Bengaluru

<sup>3</sup>Senior Technical Staff Engineer Microchip Technology Pvt. Ltd, Bengaluru

Abstract: This work presents a comparative study between basic Flipped Voltage Follower (FVF), Cascoded FVF (CAFVF) and Buffered FVF (BFVF) Low Dropout Regulators (LDO) along with simulation results in tsmcN40 PDK. The designs support a load current of 5u-10mA with a on-chip capacitive load of 100fF, for a dropout of 700 mV (From 1.8V to 1.1V). This work also employs both miller compensation and non-dominant pole cancellation techniques in BFVF to get better phase margin and PSRR. Line regulation of 3.3 mV/V and load regulation of 20.4 uV/mA was obtained for 10mA load current, with less than 0.5 uS response time in BFVF.

Index Terms: FVF, LDO, Fast response, CAFVF, BFVF

### I. INTRODUCTION

The motivation for developing Low Noise LDO for clocking circuits stems from the critical need for precise and stable timing signals in electronic systems. Clocks are fundamental in synchronizing various components within a circuit, and any noise or instability in the power supply can directly affect the performance of these clock signals. Noise in the power supply can introduce jitter and phase noise into the clock signal, which can degrade the overall performance of the system, leading to errors and reduced reliability.

Low noise LDOs are specifically designed to minimize power supply-induced variations, providing a clean and stable voltage to clock circuits. This ensures that the clock signals remain accurate and consistent, which is essential for high- performance computing, telecommunications, and data pro- cessing applications. FVF based LDOs have less reponse time compared to traditional LDOs and good noise performance. Another advantage is that it doesn't require large load capacitor and can work sufficiently well with as low capacitance as 40pF.

### II. LITERATURE SURVEY

Literature review on different LDO architectures is made first and then FVF is choosen as it has fast transient response, minimum load and line regulation, appreciable PSRR and very low RMS noise. In [1], the methods for slow loop feedback in FVF are described and tri-loop architecture is implemented, PSRR max of -10dB is achieved. This also uses a Super Source Follower (SSF), a load cap of 300pF is used and UGB of 400 MHz is achieved. Paper [5] explains in detail all the FVF architectures available and their advantage and disadvantage. It also discusses the design aspects of the CAFVF and BFVF, along with stability and bandwidth expansion methods. In [9], overshoot and undershoot damper along with Negative Capacitive Circuit (NCC) are used to achieve -76 dB PSRR at 1 MHz and 131 mV/V line regulation. In [14], tri-loop architecture is implemented with SSF based LSFVF, which achieved 600MHz UGB, line regulation of 37.1 mV/V and load regulation of 1.1 mV/mA. It had voltage variation of 82 mV at  $T_{edge}$ .

In [6], difference between on-chip and off-chip topologies in LDO architectures are explained and design considerations for on-chip capacitor architectures are elucidated. Also enhance- ment of stability and PSRR using multiple error amplifiers and frequency compensation stage are mentioned with brief introduction to different topologies like differentiator, trans- impedance and voltage subtractor.

In [15], the methods of increasing bandwidth of FVF loop are discussed. The effect of introducing Source Follower, Super Source Follower and Voltage Combiner are explained and results are shown. In [8], N-type FVF is implemented with SSF and cascoded current sources and PSRR of -84dB is achieved at 1 MHz. It also has very less noise of 17.2 nV/sqrt(Hz) is obtained by using low load capacitance of 50 pF.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 12 Issue VI June 2024- Available at www.ijraset.com

III. BASIV FVF AND CASCODED FVF

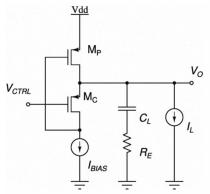

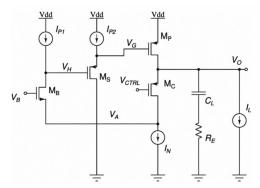

### The basic FVF structure is shown in Figure 1. The control

Fig. 1. Basic FVF structure.

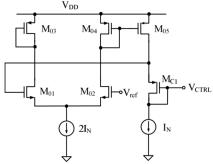

voltage is generated from op-amp and is shown in Figure 2. The output of regulator is descreibed by below equations:

Fig. 2. Control voltage generator.

$$V_{ctrl} = V_{ref} - V_{SG(MC1)} \tag{1}$$

$$V_O = V_{ctrl} - V_{GS(C)} \tag{2}$$

$$VO = V_{ctrl} + V_{SG(C)}$$

(3)

$$VO = Vref - VSG(MC1) + VSG(C)$$

(4)

From above equations, it can be concluded that if  $V_{SG(MC1)}$  and  $V_{SG(C)}$  are equal,

$$V_O = V_{ref} \tag{5}$$

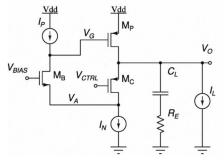

One of major drawbacks of basic FVF LDO is minimum loading requirement. When the  $I_L$  is minimum, the overdrive voltage of  $M_P$  will reduce &  $M_C$  will be pushed to trio region thus altering the output voltage. This can be avoid by using bleeding current at the output which will continuou source current from LDO but at the cost of increased pow consumption. Cascoded FVF is the improved version of FVF design to mitigate minimum loading requirement. The schematic shown in Figure 3.  $M_B$  acts as common gate amplifier which

Fig. 3. Cascoded FVF structure.

Volume 12 Issue VI June 2024- Available at www.ijraset.com

will increase the gate voltage of  $M_P$  making it to supply only required current even at minimum load and keeps  $M_C$  in saturation across varying load. Also  $V_A$  is fixed to keep the current sink  $I_N$  in saturation at all times, shown in (6)

$$VA = VBIAS - V_{GS(M_{BIAS})}$$

(6)

Even though minimum loading requirement is mitigated in CAFVF, the pole present at the gate of  $M_P$  is still at lower frequency i.e., low fast loop bandwidth due to high impedance appearing at the node as well as large aspect ratio of  $M_P$  leading to high parasitic capacitance. Also it has no control on undershoot or overshoot.

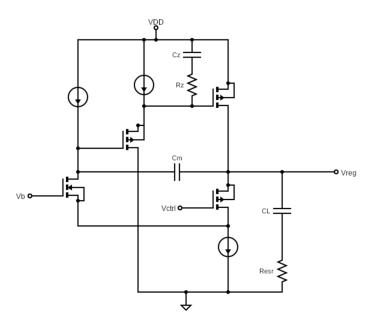

### IV. BUFFERED FVF

BFVF is a combination of CAFVF and a level shifter which contains a source follower that can push the pole at gate of the power transistor to high frequency thus increasing the bandwidth. Also it has control on both overshoot and undershoot. Schematic is shown in Figure 4

Fig. 4. Buffered FVF structure.

Fig. 5. Improved Buffered FVF structure.

pole is now  $V_H$ , which makes it constant pole which doesn't vary with load current, thus more easy to compensate using miller compensation. Output is the first non-dominant pole, and can be cancelled by introducing a solid zero at  $V_C$ , which should occur just before non-dominant pole. The improved schematic is shown in Figure 5. The values of  $C_m$ ,  $C_z$  and  $C_z$  and  $C_z$  are used for zero insertion.

Volume 12 Issue VI June 2024- Available at www.ijraset.com

### V. SIMULATION RESULTS

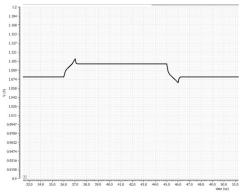

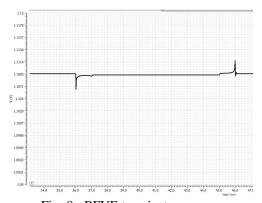

The simulation results for FVF is shown in Figure 6 Line

Fig. 6. FVF transient response.

regulation and load regulation was more, and moreover more bleeding current as high as 2 mA was required to make it work when supply reached 1.98, else fast loop was failing. The output for CAFVF is shown in Figure 7. Although output is stable, the undershoot is more and can't be controlled by any bias current in circuit. This is mainly due to miller capacitance, which directly couples the output to gate transistor of pass transistor.

Fig. 7. CAFVF transient response.

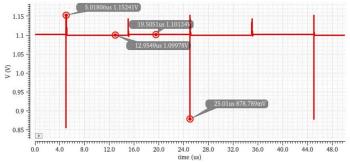

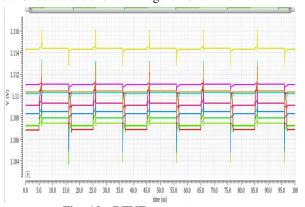

Moving onto BFVF, the results are shown in Figure 8 The observations from BFVF simulations are:

- 1) Load regulation is 204uV/10mA.

- 2) Line regulation is 1.2mV/360mV.

- 3) Output was settling between 1.107 1.114V across corners.

- 4) Overshoot and undershoot are very minimal. Small ringing found at overshoot but all outputs are settling.

Fig. 8. BFVF transient response.

- Volume 12 Issue VI June 2024- Available at www.ijraset.com

- 5) PM is maintained at 45 degree, which is sufficient for stability.

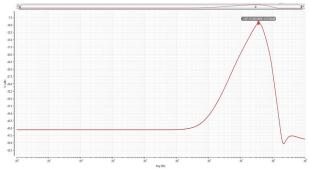

- 6) The DC PSRR is -45dB, but as frequency approaches the unity gain, PSRR increases and variation from supply couples to output. The maximum PSRR observed was 9.375dB at 35.48 MHz.

- 7) For a fixed frequency of 10 MHz, the RMS noise was between 15 to 25 nV/sqrt(Hz).

The PSRR response is shown in Figure 9

Fig. 9. BFVF PSRR response.

Design was verified across PVT corners and results are shown in Figure 10

Fig. 10. BFVF across corners.

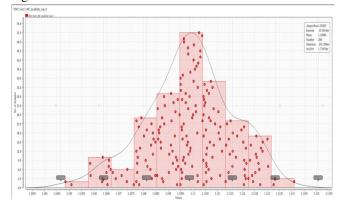

To check robustness, monte-carlo simulation was run and results are shown in Figure 11. It can be observed that for a 200 point run, min and max are 1.105V to 1.115V, with a standard deviation of 1.768mV, and all test points passed.

### VI. CONCLUSION AND FUTURE SCOPE

The conclusion drawn from three designs are elucidated in Table I

Fig. 11. Monte Carlo Analysis.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 12 Issue VI June 2024- Available at www.ijraset.com

TABLE I

COMPARATIVE ANALYSIS

| COMPARATIVE AVALISIS |               |          |          |

|----------------------|---------------|----------|----------|

| Para-                | Architectures |          |          |

| meters               | FVF           | CAFVF    | BFVF     |

| Min current          | High          | Zero     | Zero     |

| Poles                | Two           | Three    | Four     |

| Dom. pole node       | $V_G$         | $V_G$    | $V_H$    |

| Line regulation      | Not settling  | More     | Less     |

| Load regulation      | High          | Low      | Low      |

| $V_{spike}$          | Low           | High     | Low      |

| PSRR                 | Worst         | Moderate | Good     |

| UGB                  | High          | Moderate | Moderate |

| Loop gain            | Low           | Moderate | High     |

The target output voltage was 1.1V with 3% variation, that means output can vary from 1.067 to 1.133V. The actual output varied between 1.107 to 1.114V across all corners, which is well within the target. DC Load regulation is 20.4uV/mA. DC line regulation is much less than 1mV/V and transient line regulation is 3.33mV/V. PSRR of -9.3 dB maximum was observed and overshoot and undershoot were in control, both being less than 2.5mV. The future scope of the project can be listed as below:

- 1) Different approach to be taken for frequency compensation, as miller capacitance will worsen the PSRR

- 2) PSRR has to be reduced still, by applying different methods and techniques

- 3) Techniques to decrease the load capacitor further has to be studied and implemented

- 4) Layout to be implemented and verify post-layout simulation results

- 5) The design has to be tested with a real load inside the chip, rather than simulations

### REFERENCES

- [1] G. Cai, Y. Lu, C. Zhan, and R. P. Martins, "A fully integrated fvf ldo with enhanced full-spectrum power supply rejection," IEEE Transactions on Power Electronics, vol. 36, no. 4, pp. 4326–4337, Apr. 2021, issn: 1941-0107. doi: 10.1109/tpel. 2020.3024595.

- [2] Y. Lu, M. Chen, K. Wang, Y. Yang, and H. Wang, "A capacitorless flipped voltage follower ldo with fast transient using dynamic bias," Electronics, vol. 11, no. 19, p. 3009, Sep. 2022, issn: 2079-9292. doi: 10.3390/electronics11193009.

- [3] Y. Li, L. Wang, Y. Wang, S. Wang, M. Cui, and M. Guo, "A low-power, fast- transient fvf-based output-capacitorless Ido with push-pull buffer and adaptive re- sistance unit," Electronics, vol. 12, no. 6, p. 1285, Mar. 2023, issn: 2079-9292. doi: 10.3390/electronics12061285.

- [4] C.-J. Park, M. Onabajo, and J. Silva-Martinez, "External capacitor- less low drop- out regulator with 25 db superior power supply re- jection in the 0.4–4 mhz range," IEEE Journal of Solid-State Cir- cuits, vol. 49, no. 2, pp. 486–501, Feb. 2014, issn: 1558-173X. doi: 10.1109/jssc.2013.2289897.

- [5] P. R. Surkanti, A. Garimella, and P. M. Furth, "Flipped voltage follower based low dropout (Ido) voltage regulators: A tutorial overview," in 2018 31st International Conference on VLSI Design and 2018 17th International Conference on Embedded Systems (VLSID), IEEE, Jan. 2018. doi: 10.1109/vlsid.2018.68.

- [6] J. Torres, M. El-Nozahi, A. Amer, et al., "Low drop-out voltage regulators: Capacitor- less architecture comparison," IEEE Circuits and Systems Magazine, vol. 14, no. 2, pp. 6–26, 2014, issn: 1531-636X. doi: 10.1109/mcas.2014.2314263.

- [7] J. Mihhailov, V. Strik, S. Strik, and T. Rang, "Low noise Ido archi- tecture with consideration for low voltage operation," in 2014 14th Biennial Baltic Electronic Conference (BEC), IEEE, Oct. 2014. doi: 10.1109/bec.2014.7320551.

- [8] L. Shao, R. Xi, Y. Ding, et al., "A low noise high psrr ldo based on n-type flipped voltage follower," in 2022 IEEE International Power Electronics and Application Conference and Exposition (PEAC), IEEE, Nov. 2022. doi: 10.1109/peac56338. 2022.9959400.

- [9] S. J. Yun, J. S. Yun, and Y. S. Kim, "Capless Ido regulator achieving 76 db psr and 96.3 fs fom," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 64, no. 10, pp. 1147–1151, Oct. 2017, issn: 1558-

- [10] 3791. doi: 10.1109/tcsii. 2016.2628965.

- [11] X. Han, W.-H. Ki, L. Wu, and Y. Gao, "Ultrahigh psr output-capacitor- free adap- tively biased 2-power-transistor ldo with 200-mv dropout," IEEE Solid-State Cir- cuits Letters, vol. 5, pp. 106–109, 2022, issn: 2573-9603. doi: 10.1109/lssc.2022. 3172318.

- [12] J. Zhu, K. Li, Y. An, and J. Guo, "A high-psrr high-precision fast-transient-response capacitor-free Ido for Idar receiver soc," in 2023 IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), IEEE, Oct. 2023. doi: 10.1109/icta60488.2023.10364255.

- [13] R. Li, Y. Zeng, Y. Lin, J. Yang, and H.-z. Tan, "High-psr and fast- transient ldo reg- ulator with nested adaptive fvf structure," in 2020 IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), IEEE, Nov. 2020. doi: 10.1109/icta50426.2020.9332114.

- [14] Y. T. Chang, F. L. Hung, R. H. Xue, Y. D. Shiau, and P. Y. Cheng, "Ldo linear reg- ulator with super-source follower," in 2014 International Symposium on Computer, Consumer and Control, IEEE, Jun. 2014. doi: 10.1109/is3c.2014.122.

- [15] Y. Lu, Y. Wang, Q. Pan, W.-H. Ki, and C. P. Yue, "A fully- integrated low-dropout regulator with full-spectrum power supply re- jection," IEEE Transactions on Cir- cuits and Systems I: Regular Papers, vol. 62, no. 3, pp. 707–716, Mar. 2015, issn: 1558-0806. doi: 10.1109/tcsi.2014.2380644.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 12 Issue VI June 2024- Available at www.ijraset.com

- [16] A. Panigrahi and A. Mathew, "Aspects of enhancing loop band width for fvf based ldo regulators: An intuitive analysis," in 2023 Inter-national Conference on Com- puter, Electronics amp; Electrical En- gineering amp; their Applications (IC2E3), IEEE, Jun. 2023. doi: 10.1109/ic2e357697.2023.10262484.

- [17] R. Magod, N. Suda, V. Ivanov, R. Balasingam, and B. Bakkaloglu, "A low-noise output capacitorless low-dropout regulator with a switched- rc bandgap reference," IEEE Transactions on Power Electronics, vol. 32, no. 4, pp. 2856–2864, Apr. 2017, issn: 1941-0107. doi: 10.1109/tpel.2016.2576480

- [18] K. G. Shetty P S, D. R. Aradhya H V, and E. Goda, "Comparison of dynamic voltage scaling (dvs) of core voltage using the on-board voltage regulator and external voltage regulator via i2c protocol in automotive micro controller," Journal of University of Shanghai for Science and Technology, vol. 23, no. 06, pp. 794–804, Jun. 2021, issn: 1007-6735. doi: 10.51201/jusst/21/05350.

10.22214/IJRASET

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)