# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 10 Issue: VI Month of publication: June 2022

DOI: https://doi.org/10.22214/ijraset.2022.44238

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 10 Issue VI June 2022- Available at www.ijraset.com

### **High Speed UART Implementation Using VHDL**

K. Akhila Naga Satyavathi<sup>1</sup>, D.V. Sowjanya<sup>2</sup>, Sravya Akula<sup>3</sup>

<sup>1</sup>Student - B. Tech IV year, Assistant Professor - ECE Dept

Department of Electronics and Communication Engineering, Sreenidhi Institute of Science and Technology, Hyderabad, Telangana, India

Abstract: The Universal Asynchronous Receiver and Transmitter (UART) could be a custom designed circuit that allows serial communication between a laptop and a computer peripheral. The complex nature of combined circuit generation has made machine design time consuming at the gate and switch flop levels. As a results of this reality, the style designer made the choice to use hardware description language during the virtual machine layout process. VHDL could be a hardware description language that's accustomed model digital systems. It contains information that you just may find useful. It includes information which will be accustomed explain the virtual machine's behaviour shape, also because the ability to explicitly specify its timing. VHDL could be a difficult and verbose language with many complicated assembles that have complicated semantic meanings and is difficult to grasp initially. The language facilitates hierarchical machine modelling likewise as top don methodologies. It provides an easier method for checking the UART and assisting within the discovery of any discrepancies. It also allows for a more behavioural explanation of the module's characteristics. It makes the look implementation easier to read and understand, and it also provides the flexibility to simply describe dependencies among numerous procedures that arise in complex event-driven systems. Thus, the layout employs VHDL as a layout language to reap the transmitter module. First, the running version of the transmitter is defined. Then, using VHDL, all of the transmitter's blocks are designed and defined.

Keywords: UART, VHDL.

#### I. INTRODUCTION

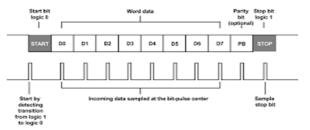

The UART is an abbreviation for Universal Asynchronous Receiver Transmitter. The UART is a mixture of hardware that's used for serial communications over a laptop or over any peripheral tool serial port. The UART is commonly used constantly with the verbal exchange requirements which include RS-232 or RS-485. As we know, the processing of statistics in our non-public computer systems or every other peripheral gadgets takes place with inside the parallel shape because it guarantees pace. But, whilst the statistics in those character structures is to be communicated to the outdoor gadgets, it's miles to be transformed right into a serial shape as verbal exchange of parallel statistics proves to be value inefficient. Hence for this purpose, we want a tool that's known as because the UART. This tool (UART) is absolutely liable for breaking the parallel local statistics in any sending machine right into a serial shape after which its miles once more used to transform this very identical statistics into parallel shape on the receiving tool. 314960-34290. The parent above suggests the simple body layout used for the UART communications. The line on which the statistics bytes are to be dispatched is held at common sense 1 whilst there may be no statistics on the road, or in different words, whilst the road is idle. UART consists of 3 crucial modules that are the baud charge generator, the receiver and the transmitter. In this paper the UART is layout for the verbal exchange among FPGA and TDC (Treatment Delivery Controller). The UART body includes one begin bit, eight statistics bit and one prevent bit. A UART is a verbal exchange tool that's specially used for verbal exchange among laptop and peripheral gadgets. This challenge proposes the hardware implementation of VHDL primarily based totally UART which have been changed to beautify its performance. This challenge turned into applied in VHDL and the synthesis is carried out the use of Xilinx software program and Spartan library. This layout is fairly incorporated and has greater flexibility.

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue VI June 2022- Available at www.ijraset.com

#### II. IMPLEMENTATION

The major additives of UART which include transmitter and receiver are defined below:

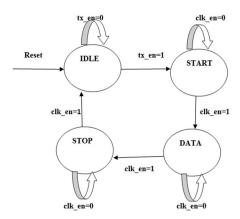

#### A. Uart Transmitter Module

The transmitter layout includes a clock divider to generate the transmission clock from the clock supply available, a shift sign up to shift the statistics out of the transmitter and a finite country gadget layout to govern the operation of the transmission machine. The one-of-a-kind components of this transmitter module are as follows:  $\Box$  Clock divider for the transmitter (Prescaled counter).  $\Box$  nine-bit shift sign up.  $\Box$  FSM (Finite State Machine) displaying the states of the transmitter.

#### B. Uart Receiver Module

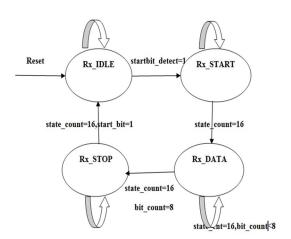

RX\_IDLE State:- When UART receiver module is reset, the country gadget might be on this country.

The country gadget will watch for begin bit detection at the serial statistics line. A begin bit detection is recognized whilst there may be a fall transition at the serial statistics line from idle

country 1 into common sense 0. A begin bit detection will reason the country gadget to enter Rx\_Start . RX\_START State:- In this country, the country gadget will watch for sixteen baud clock cycles earlier than going into the following country, RX\_DATA. RX\_DATA State:- The country gadget will pattern the statistics obtained on the maximum best time, that's on the centre of the bit. Each bit is then being saved into an inner sign up Rx statistics to shape an entire eight-bit statistics. When a entire statistics of eight bit has been obtained, the country gadget will cross into Rx Stop State.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 10 Issue VI June 2022- Available at www.ijraset.com

#### III. REQUIREMENTS

We require the subsequent additives need to be delivered withinside the layout 1. XILINX Software: Xilinx answers permit smarter, connected, and differentiated structures, integrating the very best tiers of software program-primarily based totally intelligence with hardware optimization and any-to-any connectivity. Xilinx serves the aerospace and protection enterprise with commercial, industrial, military, and area grade products. The line among software program and hardware engineering is blurrier than it would seem. Devices known as field-programmable gate arrays (FPGA), whose bodily attributes may be manipulated via the usage of hardware description languages (HDLs), bridge the distance among programming software program and programming hardware.

#### IV. ADVANTAGES

UART stands for Universal Asynchronous Receiver/Transmitter

- 1) It makes use of traces viz. TxD and Rx D for transmit and obtain functions.

- 2) It is asynchronous verbal exchange. Hence statistics charge need to be matched among gadgets trying to communicate.

- 3) It helps statistics charge of approximately 230 to 460 Kbps (most).

- 4) It helps distance of approximately 50 feet.

- 5) No not unusual place clock is being used. Moreover gadgets use their personal unbiased clock signals.

- 6) Hardware complexity is low. As that is one to at least one connection among gadgets, software program addressing isn't always required. Due to its simplicity, its miles broadly used with inside the gadgets having nine pin connector.

#### V. DISADVANTAGES

- 1) The statistics body length is limited.

- 2) Speed of statistics switch is much less whilst as compared to the parallel verbal exchange.

- 3) Proper baud charge need to be selected.

#### VI. RESULT

The timing diagram of an instance transmission. That the baud\_tb sign proven is inner to the UART and is covered right here simplest for functions of explanation.

The consumer does now no longer want to do not forget this sign to apply the UART. Centre 635 A obtain transaction is initiated through the UART's correspondent through a common sense low begin bit on the rx enter port.

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue VI June 2022- Available at www.ijraset.com

#### VII. CONCLUSION

UART with configurable baud quotes and the excessive oversampling charge on the receiver is proposed. The transmitter and the receiver module of the UART the use of the structural technique is designed and correctly synthesized the identical the use of Xilinx ISE 14.5. The UART with variable baud quotes is correctly simulated and the layout has been established on Xilinx Spartan-3E FPGA. The layout is well matched for excessive pace because of one-of-a-kind baud quotes and the excessive oversampling charge on the receiver. A most pace of 250Mbps is feasible the use of this UART layout eight.

#### VIII. ACKNOWLEDGMENT

We thank Dr. Y. Sreenivasulu, Associate professor, Electronics and communication engineering, Sreenidhi Institute Of science and technology who has been supporting us throughout the project and lending us help when needed. He has helped us accomplish our project and make it a better one. He helped us come with many innovative and creative ideas that have been helpful for us.

#### REFERENCES

- [1] Adam Osborne, An Introduction to Microcomputers Volume 1: Basic Concepts, Osborne-McGowan Hill Berkeley California USA, 1980 ISBN0-931988-34-9 pp. 116–126.

- [2] "Determining Clock Accuracy Requirements for UART Communications" (pd f). An2141. Maxim Integrated. 2003-08-07. Retrieved 1 November 2021.

- [3] Jump up to:a b "Universal asynchronous receiver/transmitter (UART)" (PDF). SCC2691. Philips NXP. 2006-08-04. p.14. Retrieved 1 November 2021.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)