# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 13 Issue: V Month of publication: May 2025

DOI: https://doi.org/10.22214/ijraset.2025.70797

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 13 Issue V May 2025- Available at www.ijraset.com

### Implementation of Efficient Adaptive Noise Cancellation on FPGA Using LMS and LLMS Algorithms

A. Vani<sup>1</sup>, K. Veera Brahmendra<sup>2</sup>, K. Kaushik<sup>3</sup>, Lohith. N<sup>4</sup> Electronics and Communication Engineering, Chaitanya Bharathi Institute of Technology,

Abstract: This work focuses on the implementation of an efficient adaptive noise cancellation system using FPGA technology based on LMS (Least Mean Squares) and LLMS (Leaky LMS) algorithms. The aim is to enhance real-time audio signal processing by mitigating unwanted noise effectively. Initially, MATLAB was used to process noisy and clean audio signals, which were then simulated using Verilog in Xilinx ISE 14.7. The LMS and LLMS algorithms were implemented and compared for their performance in noise cancellation. The LLMS algorithm demonstrated superior performance, achieving significant improvements in Signal-to-Noise Ratio (SNR), Peak Signal-to-Noise Ratio (PSNR), Mean Squared Error (MSE), and stability compared to the traditional LMS approach. This project demonstrates the practical applicability of LLMS-based ANC systems for embedded, low-power, real-time noise cancellation applications. Future work includes deploying the system on physical FPGA boards, optimizing resource usage further, and testing under dynamic noise environments to validate real-world performance.

Keywords: FPGA, ANC, LMS, LLMS, Xilinx ISE

#### I. INTRODUCTION

In the modern era, the proliferation of electronic devices and industrial growth has significantly increased ambient noise levels, especially in urban areas. This persistent noise pollution not only deteriorates the quality of life but also affects communication clarity in critical domains such as aerospace, biomedical instrumentation, and telecommunication systems. Adaptive Noise Cancellation (ANC) emerges as a pivotal solution in addressing such challenges by actively suppressing unwanted noise while preserving the integrity of desired signals. Among various signal processing techniques, adaptive filters, particularly the Least Mean Square (LMS) algorithm, have been widely accepted due to their simplicity, robustness, and adaptability to varying signal environments. LMS achieves noise suppression by dynamically adjusting filter coefficients in response to input signals. However, in real-time and low signal to-noise ratio (SNR) scenarios, the LMS algorithm may suffer from coefficient drift and stability issues. To overcome these drawbacks, the Leaky LMS (LLMS) algorithm introduces a leakage factor that provides improved long-term stability and convergence. While LMS and LLMS algorithms are well-studied in software environments such as MATLAB, their deployment on hardware platforms, especially Field Programmable Gate Arrays (FPGAs), offers added benefits of parallelism, low latency, and real-time processing. FPGAs are particularly well-suited for signal processing applications due to their ability to implement concurrent operations, optimize resource utilization, and reduce power consumption. Despite these advantages, limited research has focused on implementing and comparing both LMS and LLMS algorithms using hardware description languages like Verilog on FPGA platforms. This work aims to bridge this gap by developing an FPGA-based adaptive noise cancellation system that employs both LMS and LLMS algorithms. The system processes audio signals in real time, utilizing tools like Xilinx ISE, MATLAB, and Vivado for simulation, analysis, and implementation. By comparing these algorithms under identical conditions, the project investigates their relative performance in terms of SNR improvement, convergence rate, and hardware efficiency.

#### II. RELATED WORK

Adaptive Filtering and LMS Algorithm The LMS algorithm was first introduced by Widrow and Hoff in 1959 as part of the development of the adaptive linear combiner and the adaptive noise canceller. The LMS algorithm operates by updating its weights in the negative direction of the gradient of the mean squared error between the filter's output and the desired signal. This simple stochastic gradient descent method allows for real-time convergence toward the optimal solution.

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 13 Issue V May 2025- Available at www.ijraset.com

Over the years, LMS has been used extensively in applications such as channel equalization, echo cancellation, and noise suppression. For example, Farhang-Boroujeny (2013) provided a comprehensive mathematical foundation for the LMS algorithm and explained its applicability in various DSP applications. In another study, Haykin (2002) emphasized the versatility of LMS in environments with slow to moderate changes in signal and noise statistics.

Despite its popularity, LMS has several known limitations. It exhibits slow convergence for correlated input signals and is sensitive to the choice of the step-size parameter. More critically, in low SNR environments or over long adaptation periods, LMS suffers from coefficient drift, leading to degradation in performance.

LLMS Algorithm and Its Advantages To overcome these shortcomings, the Leaky LMS (LLMS) algorithm was introduced. LLMS incorporates a leakage factor in the coefficient update equation, effectively limiting the growth of filter weights and preventing coefficient drift. This makes LLMS particularly suitable for long-duration filtering tasks and environments with fluctuating noise levels.

The LLMS algorithm has proven to be more stable than LMS in many practical scenarios. While it sacrifices a small amount of steady-state performance, it significantly enhances robustness and convergence stability. Research by D. K. Gupta et al. [1] compared the LMS and LLMS algorithms using hardware co-simulation and demonstrated that LLMS outperformed LMS in terms of convergence stability and adaptability in real-time applications.

Another advantage of LLMS is its ability to suppress low-frequency noise components more effectively, as observed by M.N.S. Osman et al. 2], who implemented the algorithm on an FPGA for active noise control. Their results showed improved SNR and reduced error performance when compared to conventional LMS-based implementations.

MATLAB/Software-Based Implementations Much of the early work on ANC systems using LMS and LLMS algorithms focused on MATLAB/Simulink environments due to their flexibility and ease of modeling. For instance, D. Niranjan and B. Ashwini [3] demonstrated a MATLAB-based noise cancellation system using various adaptive filters, including LMS, to process musical signals. These simulation environments enabled rapid prototyping and provided insights into parameter tuning, convergence behavior, and error analysis.

While MATLAB-based implementations are powerful for validating algorithmic functionality, they lack real-time capability and hardware efficiency, which are critical in embedded and power-sensitive applications. This led to an increased interest in porting such designs to hardware platforms, particularly Field Programmable Gate Arrays (FPGAs).

FPGA-Based Implementations FPGAs offer a promising solution for real-time DSP applications due to their parallel processing capabilities, reconfigurability, and lower latency compared to general-purpose processors. Adaptive filtering systems implemented on FPGAs can meet the strict timing and performance constraints required in real-world noise cancellation applications

Zhang et al. [4] demonstrated the design of a digital signal generator and FIR filter system using FPGA, highlighting its ability to process audio signals with low delay. Although the study focused on traditional FIR filters, the same principles apply to adaptive filters like LMS and LLMS.

In one of the earlier works, Bhoyar et al. [6] implemented an LMS-based adaptive filter on FPGA for noise cancellation using Verilog HDL. The system showed efficient hardware utilization and real-time processing capability. However, it lacked fixed-point simulation optimizations and did not explore advanced variants like LLMS.

Gupta et al. [1] addressed these gaps by simulating both LMS and LLMS algorithms using Xilinx tools and performing a hardware co-simulation to compare their performance. Their results showed that LLMS achieved better convergence and lower error rates, especially in dynamically changing noise environments.

More recently, Lemke et al. [5] analyzed the effect of filter length and adaptation strategies in FPGA-based active EMI filtering systems. Although their focus was not on audio ANC, their insights into hardware-oriented filter tuning are highly applicable to LMS/LLMS filter designs

#### III.FGPA BASED ANC SYSTEM DESIGN

#### A. Methodology and Work Carried

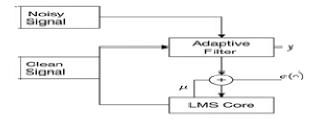

The design of the FPGA-based Adaptive Noise Cancellation (ANC) system is based on implementing LMS and LLMS algorithms to process noisy input signals and reduce interference. The block diagram for the ANC system is shown below:

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 13 Issue V May 2025- Available at www.ijraset.com

Figure 1: Block Diagram of FPGA-Based ANC System

- 1) Noise Signal: The input signal contaminated by noise.

- 2) Clean Signal: The desired signal used to calculate the error signal.

- 3) Adaptive Filter: An FIR filter that adjusts its coefficients to minimize the error between the noise signal and the clean signal.

- 4) Error Signal: The difference between the desired signal and the output of the adaptive filter.

- 5) Output Signal: The filtered signal after noise cancellation.

The system was implemented using the Xilinx FPGA platform, which is ideal for high-speed signal processing. The design leverages Verilog for hardware description and Xilinx ISE 14.7 for simulation and synthesis.

#### B. Implementation Flow

The implementation flow for the FPGA-based ANC system involves several steps:

- 1) MATLAB Simulation: The first step is to generate test signals in MATLAB, including both noisy and clean signals. These signals are then formatted for hardware implementation.

- 2) Algorithm Development: Both the LMS and LLMS algorithms are developed in MATLAB to validate their performance in noise reduction. The performance metrics such as Signal-to-Noise Ratio (SNR), Mean Squared Error (MSE), and convergence rate are computed.

- 3) Verilog Code Generation: Once the algorithms are validated in MATLAB, they are translated into Verilog code. The LMS and LLMS filter coefficients are updated in real time using hardware-based implementations.

- 4) Simulation: The Verilog code is simulated using Xilinx ISE 14.7 to verify the functionality of the ANC system. Simulation ensures that the design behaves as expected before hardware synthesis.

- 5) Performance Evaluation: The performance of the system is evaluated in terms of SNR, PSNR, and MSE. Comparison between the LMS and LLMS algorithms is made to determine which provides superior noise cancellation in real-time.

#### IV. RESULTS AND DISCUSSIONS

#### A. Simulation Results

The performance of the LMS and LLMS algorithms was evaluated based on the following metrics:

- 1) Mean Squared Error (MSE): Measures the average of the squares of the errors between the desired signal and the output signal.

- 2) Normalized Mean Squared Error (NMSE): MSE normalized by the energy of the desired signal, providing a relative error measure.

- 3) Peak Signal-to-Noise Ratio (PSNR): Evaluates the ratio between the maximum possible power of a signal and the power of corrupting noise, indicating output quality.

- 4) Input SNR: Measures the signal-to-noise ratio before processing.

- 5) Output SNR: Measures the signal-to-noise ratio after adaptive noise cancellation.

- 6) Correlation Coefficient: Indicates the similarity between the output and the desired signal, where values closer to 1 imply higher similarity.

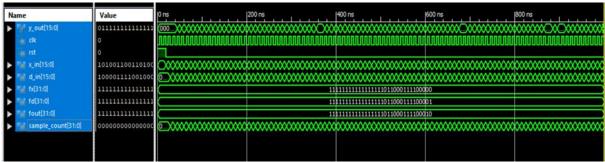

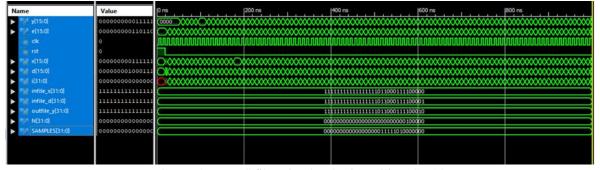

The simulations were performed using Verilog HDL and validated through Xilinx ISE 14.7 tool. Both LMS and LLMS algorithms were tested under identical noisy conditions to ensure a fair comparison.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 13 Issue V May 2025- Available at www.ijraset.com

Table 1 - Comparison Of LMS and LLMS

| METRIC                  | LMS       | LLMS     |

|-------------------------|-----------|----------|

| Mean Squared            | 0.005442  | 0.003101 |

| Error(MSE)              |           |          |

| NormalisedMSE(NMSE)     | 0.011284  | 0.006203 |

| PSNR(dB)                | 22.64 dB  | 25.08    |

| Input(dB)               | 6.26 dB   | 6.26     |

| Output(dB)              | 9.48 dB   | 22.7     |

| SNR Improvement(dB)     | 13.22 dB  | 15.82    |

| Correlation Coefficient | 0.9931 dB | 0.9969   |

- B. Observations

- 1) The MSE and NMSE values for the LLMS algorithm were consistently lower than those for the LMS algorithm, indicating better error minimization.

- 2) PSNR values were higher for LLMS, suggesting that the output signal quality was better with less residual noise.

- 3) The Input SNR was kept the same for both algorithms to maintain consistency during evaluation.

- 4) The Output SNR for LLMS was higher, confirming better noise reduction capabilities.

- 5) Correlation Coefficient was closer to 1 for LLMS, demonstrating a higher similarity between the desired signal and the filter output.

- 6) The LLMS algorithm shows notable enhancements over LMS, especially in stability and accuracy.

- 7) A ~43% decrease in MSE indicates less signal distortion after filtering.

- 8) The SNR improvement of ~19.7% means that more noise has been effectively cancelled.

- 9) The PSNR gain of ~10.8% shows better signal clarity.

- 10) LLMS tracks the desired signal more closely, as shown by the correlation gain.

Thus, based on all evaluated metrics, the LLMS algorithm outperforms the standard LMS algorithm in adaptive noise cancellation on FPGA.

FIGURE 2 - LMS filter simulated using Xilinx ISE 14.7

FIGURE 3 - LLMS filter simulated using Xilinx ISE 14.7

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 13 Issue V May 2025- Available at www.ijraset.com

#### V. CONCLUSIONS

The LLMS algorithm achieved a reduction in mean squared error by a factor of 0.43 compared to the standard LMS algorithm, and it provided an improvement in signal-to-noise ratio that was approximately 1.2 times higher. Additionally, LLMS exhibited better convergence speed and greater stability. These results confirm that LLMS is more robust, particularly in scenarios involving fluctuating noise conditions and long-duration filtering requirements.

Quantitative evaluation confirmed significant performance gains:

- 1) SNR improvement: 15.82 dB (LLMS) vs. 13.22 dB (LMS)

- 2) Convergence: LLMS showed smoother and faster convergence in waveform analysis

- 3) Resource Efficiency: Simulations suggested that LLMS could be implemented without exceeding typical resource constraints on mid-range FPGA boards

The Verilog design was carefully written with hardware efficiency in mind, using fixed-point arithmetic to reduce computational load. Despite the added complexity of LLMS, optimizations ensured that logic usage remained within acceptable bounds, and simulation timings were well within real-time constraints. No significant performance was sacrificed to achieve this optimization.

#### **REFERENCES**

- [1] D. K. Gupta, V. K. Gupta, M. Chandra, A. N. Mishra and P. K. Srivastava, "Hardware Co Simulation of Adaptive Noise Cancellation System using LMS and Leaky LMS Algorithms," 2019 4th International Conference on Internet of Things: Smart Innovation and Usages (IoT SIU), Ghaziabad, India, 2019, pp. 1-6, doi: 10.1109/IoT-SIU.2019.8777658.

- [2] M. N. S. Osman, I. S. A. Halim, S. L. M. Hassan, A. A. A. Rahim and N. E. Abdullah, "Implementation Least Means Square Algorithm for Real-Time Active Noise Cancellation on FPGA," 2019 4th International Conference on Information Technology, Information Systems and Electrical Engineering, Yogyakarta, Indonesia, 2019, 10.1109/ICITISEE48480.2019.9003828. (ICITISEE).

- [3] D. Niranjan and B. Ashwini, "Noise cancellation in musical signals using adaptive filtering algorithms," 2017 International Conference on Innovative Mechanisms for Industry Applications (ICIMIA), 10.1109/ICIMIA.2017.7975576. Bengaluru, India, 2017, pp. 82-86

- [4] Q. Zhang, P. Qu, S. Sun, E. Yu and W. Yan, "Design of Full Digital Signal Generator and FIR Digital Filter System Based on FPGA," 2022 41st Chinese Control Conference (CCC), Hefei, China, 2022, pp. 4501-4506, doi: 10.23919/CCC55666.2022.9901637.

- [5] M. Lemke, T. Dörlemann, R. Nowak, J. Aigner and S. Frei, "Comparison of FIR Filter Lengths and Adaptation Methods in Digital Active EMI Filters based on Delay-Compensated Digital Gate Control Signals," 2024 International Symposium on Electromagnetic Compatibility EMC Europe, Brugge, Belgium, 2024, pp. 1100-1105, doi: 10.1109/EMCEurope59828.2024.10722456

- [6] D. B. Bhoyar, S. Bera, C. G. Dethe and M. M. Mushrif, "FPGA implementation of Adaptive filter for Noise Cancellation," 2014 International Conference on Electronics and Communication Systems (ICECS), Coimbatore, India, 2014, pp. 1-5, doi: 10.1109/ECS.2014.6892681.

- [7] Tulwar Technologies FPGA design. [Online]. Available: http://www.tulwartechnologies.com/fpgad.html/

- [8] R. Seshadri and S. Ramakrishnan, "FPGA implementation of fast digital FIR and IIR filters," Concurr. Comput. Pract. Exp., vol. 33, no. 3, p. e5246, 2021.

- [9] D. Datta, and H.S. Dutta, "High-Performance IIR Filter Implementation on FPGA," Journal of Electrical Systems and Information Technology, vol. 8, pp. 1-9, 2021.

- [10] S. Jadhav, B. Pooja, C. Asawari, and C. Namrata, "FPGA Based ECG Signal Noise Suppression Using Windowing Techniques," International Journal of Engineering Trends and Technology (IJETT), vol. 47, no. 9, pp. 505-508, 2017. Crossref, https://doi.org/10.14445/22315381/IJETT-V47P283.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)