# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 10 Issue: VII Month of publication: July 2022

DOI: https://doi.org/10.22214/ijraset.2022.45257

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 10 Issue VII July 2022- Available at www.ijraset.com

### Low Power, High Performance PMOS Biased Sense Amplifier

Amulya. S<sup>1</sup>, Mr. Manohar B. S<sup>2</sup>, Dr. PM Shivakumara Swamy<sup>3</sup>

<sup>1</sup>M. Tech Student, Department of Electronics and communication Engineering, JSS Academy of Technical Education Bengaluru

<sup>3</sup>Assistant professor Department of Electronics and communication Engineering, JSS Academy of Technical Education Bengaluru

<sup>2</sup>Professor and Head Department of Electronics and communication Engineering, JSS Academy of Technical Education

Bengaluru

Abstract: The capacity, functionality, dependability, and durability of the memory sense circuits in the basic cell are all significantly impacted by sense amplifiers in the proposed experiment. We will create two novel circuits that have been suggested in this presentation.

This project's suggested circuit is a PMOS biassed sense amplifier with a basic cell that has a high output impedance and reduces the circuit's sensing latency as well as its power dissipation. As a result, the developed circuit executes operations similarly to those of parallel circuits, reducing the sense latency and circuit power consumption. The performance of one of the recommended sense amplifiers may then be verified by simulation utilizing Tanner EDA and CTSA and 180nm technology, leading to a sense decoder employing advanced technology in the technique.

Keywords: sense amplifier, sense decoder, micro-controller, CTSA, power dissipiation, PMOS.

#### I. INTRODUCTION

In computers, in DSP, in micro processors, and micro controllers although through microprocessors the main important digital system design is logic design memories. Thus as all we know about Audio players with the frequency, digital cameras with image pixel which have to include in the system. The stored data which have improved quality of increased higher capacities and lower the delay which is required for low sensing delay. By having the sensing timings which have continuous difference voltage with very less customarily decoders with sense amplifier to enhance the staging of towering. Therefore the difference voltage which shows accurately the amplifying signal is enabled to the enrichment of the circuit. Hereby in the SRAM cell which has the more intensive speed with the limited timing.

The sense amplifier memory which have the recognized memory chip which needs the most of the time. Therefore memories chip are the important one in the sense amplifier. Hereby we can know in this paper that the stores memory data which is amplified the signals need the bit lines dor the changes to be done in the circuit. we all know that in the new generation of the CMOS technology the world of advanced area which mainly concentrate on the system designer to develop with fast, low power which have the sense amplifier. Now, in recent days,the main quality of power is more important in the memory bit lines which as the signal delays. There by the problem is that the current signal is replaced by the voltage signal, where the problem decreases by the above given solution with the replacement, there by here the small voltage changes in the circuit decreases the power of technology.

The sense amplifier which is all needed to voltage fluctuation which will decreases the bitline senseing power. Therefore here we have the more speed with total big memories, which holds with the low voltage by correctly analyzing the problem with the given solution.

On the basis of operation modes, a sense amplifier may be classified as:

- 1) Voltage Sense Amplifier

- 2) Current Sense Amplifier

- 3) Charge Transfer Sense Amplifier (CTSA)

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue VII July 2022- Available at www.ijraset.com

Following are the performance metrics to be considered during the design of sense amplifier:

- a) Minimum sensing delay,

- b) Maximum voltage swing,

- c) Minimum power consumption,

- d) Optimized layout area,

- e) High reliability,

- f) Specified environmental tolerance.

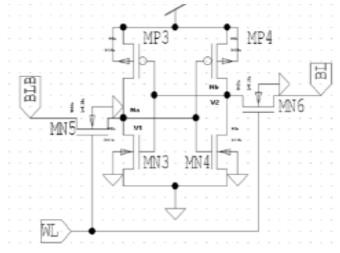

There we know how to construct the Sense amplifier, which includes the parts of transistor. The transistor consists of the three important parts and which are named by acess transistor, driver transistor and load transistor. In the below diagram, which are MN5 transistor to MN6 transistor is called the access transistor, MN3 transistor and MN4 transistor is called the driver transistor, and MP3transistor and MP4 transistor called the load transistor. Thus from the diagram of sense amplifier we can understand the working procedure of basic sense amplifier in the circuit cell. For the better understanding of the circuit we have to know the before state of the cell in the amplifier, let us consider which has the sense amplifier has already have the big data which have with the result of node Na and have the big status at the node Nb, where the both node Na, and node Nb has low status, which results in the output. The transistor MP4 & MN3 transistor which turn on, and transistor MP3 & transistor MN4 turn off. Hereby we know that the each data from the bit line comes to the circuit cell which is intimated to become zero.

Fig: sense amplifier circuit.

#### II. LITERATURE SURVEY

In this edition, a thorough analysis of the many amplifiers with power mode, suggested in the open literature have been done in this paper. Therefore, 0.25 pm CMOS technology sense amplifiers were constructed for the cell, and ST Microelectronics and simulation results were supplied nearly the bad case, progress and heat, sense time below various power voltages V& and busline capacitance values. From there, it has been shown that a memory sense amplifier's sensing latency is completely decreased dynamically and that its output are isolated from the busline or isolated from dataline, as appropriate, capacitances. Which is possible for sense amplifiers of the differential latch and clamped bit-line types. When compared to the others in this research, we all know that those sense amplifiers gives good sense time. Two sense amplifiers are so distinguished in this from their resistance to comforting process and operating temperature variations. The making of a virtual path between the sense using circuits and the busline prevents this from being more sensitive to the busline capacitances, which explains why the very straightforward we know that having four transistor in sense amplifier which gives better behaviour than the less transistor part and the biased PMOS type sense amplifiers. Under reduced power supply circumstances in the cell, the sense amplifiers of the differential latch type, which as well as the PMOS bias type, practically never function. The other two functions of the four transistor and the less number of transistors sense amplifiers in the cell or severely impacted at less voltage procedure, which the amplifier being the more sensitive in the sense amplifier cell. The vision busline, which gives valuable protection, keeps reducing to 1.5V power supply voltage.

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 10 Issue VII July 2022- Available at www.ijraset.com

#### III. METHODOLOGY

From above existing methodology which is most important parts is, the sense amplifier is the memory of the chip in the circuit. Completely which can Access time with restfully of memory is can be identified through the sense amplifier in the circuit. Anyhow from any conversion in the whole bus-lines identified, which can get with the complete signals are amplified with the equal of the time of the developers and supplies within the enhance memory data. The developer to develop the quick output, when the sense amplifier has low power—in the area of important CMOS technologies.

Recent days, the memory bus lines thus can be mainly which the main cause of extra delay of the signal which has its own, earlier in capacitance and dependence. When length of the channel which demodulates low, with when the gain of signal voltage decreases, the problems which has complete are diluted by signal sensing. With all the overcome of instead of voltage signals in the circuit. Here we having low voltage, more speed with more larger memory the sensing of current from the amplifier will be better approach. Hereby we know that there there is no voltage.

#### A. PMOS Bias Sense Amplifier

#### 1) Sense Amplifier Circuit-1

As we know the procedure of the sense amplifiers, which has two parts: before charging and sensing signal which amplifies from of the circuit. From before charging phase to each signals which have to stress to complete sensing quantity of equal dimension of certain voltages are applied through the signal. Having the same time we can have sensing operation with difference is done between the current signal amplifier edges. Thus from the observation of the enhanced memory cell in the complete circuit is validate as a result of this replication can be evolved.

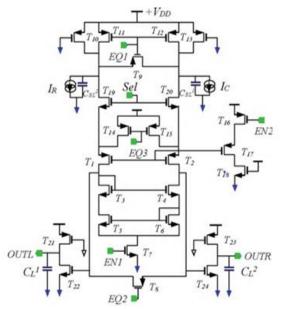

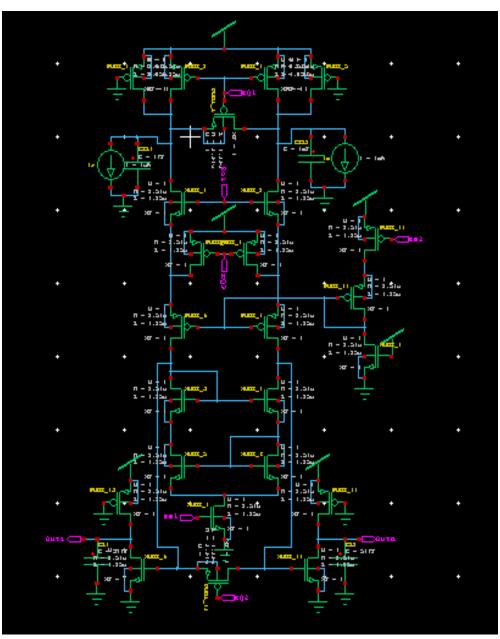

The below proposed circuit-1 shows impedance with high output, and with no error of static. From this implemented project of these, circuit includes terminals of gate in the transistor T1, transistor T2 and transistor T7 are short connected in the below figure. From here the output impedence increases, Ir is more from Ic . The Ir will flows through the busline BL1,the IL2 flows by the busline BL2.

Fig: proposed circuit 1

The proposed circuit-1 provides high output impedance, no static error. In this proposed circuit the gate terminals of T1, T2 and T17 are short circuited and Ir is greater than Ic then there is a slight difference of current flowing through both bit lines. So the current Ii-Id will flows through the bit-line BL2 and current II will flows through the bit-line BL1

Transistor pairs T3-T4 and T5-T6 are exactly coincided. So, input and output potentials are approximately the same, then in principle the input and output currents are equal. Number of transistors is reduced and compared to the conventional type of sense amplifiers. Therefore, sense delay and power dissipation gets reduced.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 10 Issue VII July 2022- Available at www.ijraset.com

The conventional PMOS bias type sense amplifier has more number of transistors and power consumed is also higher side. In the proposed circuit OUTL is taken across T1 and T3 and OUTR across T2 and T4. The modified sense amplifier reduces the power consumption and sense delay.

Now here we pair transistor T3 and transistor T4, and transistor T5 and transistor T6 which are exactly parrellely connected. Hence from output energies and input energies are equally same, by then in where the principle of output currents and input currents are almost similar. By this we can know that Number of transistors get decreases which is compared with the different type of amplifiers with sensors. Hence ,we have and power dissipation and delay of sense amplifier from circuit which have reduced from the proposed project.

The sense amplifier of differential biased PMOS type sense amplifier have more number of transistors with the high power consumption. Here we have the proposed method output OUTL is taken between transistorT1 and transistorT3 and output OUTR across transistorT2 and transistorT4. Therefore we have identified sense amplifier which reduces the power consumption of the circuit and sense delay of circuit.

#### 2) Sense Amplifier Circuit-2

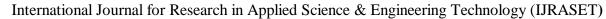

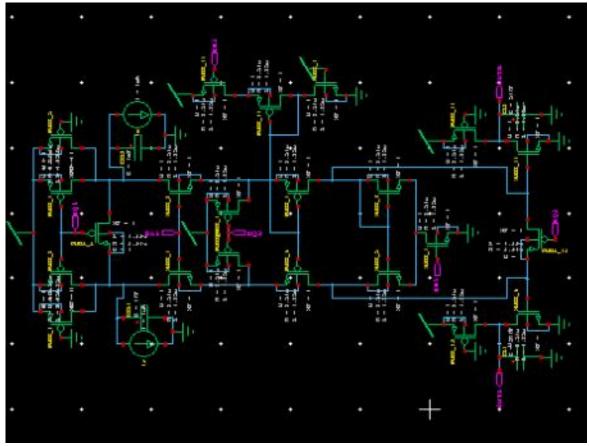

Fig: proposed circuit 2

The working principles which has of the implement of two sense amplifier having circuit has the input development.

The part of the circuit contains the transistors T7 to transistor T11 which are used to charge the bit lines in the phase of pre cahrging amplifier. The selection process of input is given to provide the differential currents with voltage to the circuits. Here we have there are two constant current sources of voltages having the bit-line capacitance across it in this project. In this project we have three equalizer inputs which are used to bring the bit lines at equal potential of the system. Furthermore, the notation EQ1 is normally on equalizer1. The outputs out L and output out R are taken between the inverters which are connected across load capacitance in circuit. Thus the gate signal form the third equalizer EQ3 input is given from the voltage bias generator from the circuit. The determination of the circuit, here exists only one current mirror circuit of the base cell.

By this project, we have implemented of PMOS sense amplifier which is biased and given from the output of the circuit. As early as procedure time and with low power dissipation are gained, which have early implemented circuits of sense amplifier for the low voltage power supply of the project. In the implemented project circuit1, where the sense amplifiers are changed by interacting for the a current parallel circuit, having another connecting amplifier parallel to the up connected amplifier. From this project we can conclude the high performance of the system.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 10 Issue VII July 2022- Available at www.ijraset.com

#### IV. ADVANTAGES & APPLICATIONS

- A. Advantages

- 1) Area is reduced by minimizing of transistors

- 2) Sense delay is also reduced.

- B. Applications

- 1) Memory Units

- 2) Microprocessors

- 3) Micro controllers

- 4) Computers

#### V. RESULTS AND ANALYSIS

Fig: Schematic of proposed cicuit\_1 of Sense Amplifier

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue VII July 2022- Available at www.ijraset.com

Fig: Schematic of proposed circuit-2 of Sense Amplifier

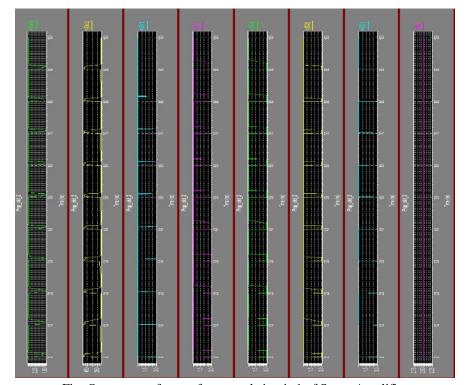

Fig: Output waveforms of proposed circuit-1 of Sense Amplifier

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue VII July 2022- Available at www.ijraset.com

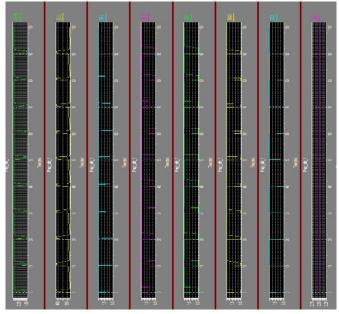

Fig: Output waveforms of proposed circuit-2 of Sense Amplifier

#### VI. CONCLUSION & FUTURE SCOPE

Two new sense amplifiers were designed using Tanner EDA by employing 180nm CMOS Technology and the transient results of the proposed sense amplifiers were congruent with the theoretical analysis. Also, the graph is drawn for a simulated sensing delay at different supply voltages. The proposed circuits have less number of transistors, so that sensing delay and power dissipation are also reduced.

Since power consumption plays crucial role in DSP application where SRAMS (sense amplifier is an essential part in SRAM)s are widely used, by using Low Power techniques we can further reduce the power consumption and transistor count.

#### REFERENCES

- [1] Chrisanthopoulos, Y. Moisiadis, Y. Tsiatouhas and A. Arapoyanni, "Comparative study of different current mode sense amplifiers in submicron CMOS technology", IEE Proc.-Circuits Syst., Vol. 149, No. 3, June 2002, pp.154-158.

- [2] S. Yang, W. Wang, N. Vijayakrishnan, and Y. Xie, "Low-leakage robust SRAM cell design for sub-100 nm technologies", in Proc. ASPDAC, 2005, pp.539-544

- [3] Mahendranath. B and Avireni Srinivasulu, "Performance analysis of a new CMOS output buffer", in proc. of IEEE International Conference on Circuit, Power and Computing Technologies, Kumaracoil, India, Mar 21-22, 2013, pp. 752-755. Dol: 10.1109/ICCPCT.2013.6529041.

- [4] T. Srivyshnavi, and A. Srinivasulu, "A current mode Schmitt trigger based on Current Differencing Transconductance Amplifier: without any passive components", in proc. of IEEE International Conference on Signal Processing, Communications and Networking, Chennai, India, March 26-28, 2015, pp. 1-4. DOI: 10.1109/ICSCN.2015.7219884.

- [5] Madira Suma, V. Venkata Reddy and Avireni Srinivasulu, "Current mode Schmitt trigger based on ZC-current differencing transconductance amplifier", in proc. of IEEE International Conference on Inventive Computation Technologies, pp. 439-443, Aug 26-27, India.

,

10.22214/IJRASET

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)