# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 10 Issue: IV Month of publication: April 2022

DOI: https://doi.org/10.22214/ijraset.2022.41617

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 10 Issue IV Apr 2022- Available at www.ijraset.com

### A Low Power High Speed Accuracy Controllable Approximate Multiplier Design

Lakshmi Thirumala Kosuri<sup>1</sup>, M. Deepika Krishna<sup>2</sup>, Adilakshmi Karapati<sup>3</sup>, B.S.B Ayyappa Swamy<sup>4</sup>, Dinesh Nayak S<sup>5</sup>

<sup>2</sup>Assistant Professor, Department of Electronics and Communication Engineering, S. R. Gudlavalleru Engineering College,

Gudlavalleru, India

<sup>1, 3, 4, 5</sup>Department of Electronics and Communication Engineering, S. R. Gudlavalleru Engineering College, Gudlavalleru, India

Abstract: For energy effective and high performance design, the low power VLSI circuit is used. Multiplier is an essential part of low power VLSI design, since the effectiveness of the digital signal processor depends upon the multiplier. In multiplier circuit, utmost of the power is dissipated across in full adder circuits. Multiplication is one of the important process in microprocessor and there will be a lot of delay because of array multiplier, which can be compressed with the help of the column compressor approach. It uses a selection of half adders, full adders and compressors to sum the partial products in stages until two numbers are left. An 8 \* 8 and 16 \* 16 bit multiplier design is executed by assigning the adder and compressor. Partial product totality is the speed limiting operation in multiplication due to the propagation detention in adder networks. In order to reduce the propagation detention, compressors are introduced. Compressors calculate the sum and carry at each position concurrently. The attendant carry is added with a advanced significant sum bit in the coming stage. This is continued until the final product is generated. The partial product tree of the multiplier is estimated by the proposed tree compressor (High Speed Compressor, Dual Stage Compressor, Exact Compressor).

Keywords: Partial Products, Half Adder, Full Adder, High Speed Compressor, Dual Stage Compressor, Exact Compressor.

#### I. INTRODUCTION

Multiplication is the crucial computation operation which is extensively used in numerous microprocessors and digital signal processing operations. Microprocessors use multipliers within their computation reasoning units, and digital signal processing systems take multipliers to apply DSP algorithms similar as filtering.

Since the multiplier falsehoods directly within the critical path in utmost systems, the demand for high speed multiplier is continuously accelerating. Nevertheless, with the fast growing of movable computing tendency, the power consumption of the multiplier has come similarly important.

All this has responded in the pursuit of high speed low power multiplier design approaches. Previous to exploring the colorful multiplication algorithms, and the uses of each, it's imperative to present the essentiality of digital multiplication, and the standard title. Just as in the paper and pencil methodology of carrying a multiplication of two values, digital multiplication entails a sequence of additions carried out on partial products.

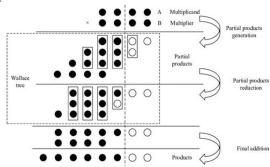

The means by which this partial product array is added to yield the final product is the crucial identifying factor amongst multiplication scheme.

#### II. LITERATURE SURVEY

K. C. Bickerstaff, E. E. Swartzlander, and M. J. Schulte [1] proposed a method on Analysis of column compression multipliers. The column compression technique reduces the delay in the circuit. Column compression multipliers are faster than array multipliers. The paper studies the area, delay and power characteristics of Dadda and Wallace multipliers and found that the ratios of power to area increases with operand word length due to longer interconnect lines and may also increase the chances of occurrence of fault.

C. Liu, J. Han, and F. Lombardi[7] published A Low-Power, High-Performance approximate multiplier with configurable partial error recovery. This multiplier uses a new type of approximate adder that limits the carry propogation to the nearest neighbor for quick partial product accumulation, because of this the power consumption reduces as the critical path is shorter. The proposed multiplier has high accuracy and low error, lower power consumption as compared to traditional Wallace multiplier.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue IV Apr 2022- Available at www.ijraset.com

#### III. EXISTING SYSTEM

$\begin{array}{c} 0\ 0\ 1\ 0\ 1\ 1\\ \underline{0\ 1\ 0\ 0\ 1\ 1}\\ 0\ 0\ 1\ 0\ 1\ 1\\ 0\ 0\ 0\ 0\ 0\ 0\\ 0\ 0\ 0\ 0\ 0\ 0\\ \underline{0\ 0\ 1\ 0\ 1\ 1}\\ 0\ 0\ 1\ 1\ 0\ 1\ 0\ 0\ 0\ 1\end{array}$

Fig:1 Basic Multliplier Process

The multiplier multiplicates multiplicand therefore the paritial products are obtained. So the partial products are given to full adders to get the final result. By using full adder area and power will be more with high delay.

#### IV. PROPOSED SYSTEM

The column compacting approach reduces the detention in the circuit. Column compacting multipliers are briskly in nature than array multipliers. This paper studies Column compressor techniques for 8 \* 8 bir and 16 \* 16 bit multiplier. In 8 \* 8 bit multiplier Exact Compressor is Used.

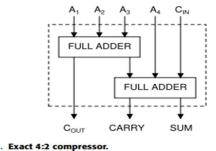

Fig :2 Exact Compressor

The general block diagram of an exact 4:2 compressor comprises of five inputs, three outputs and two cascaded full adders. A1, A2, A3, A4 and CIN are are the inputs and COUT, CARRY and SUM are the outputs of the exact 4:2 compressor.

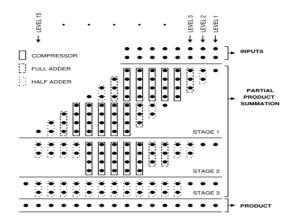

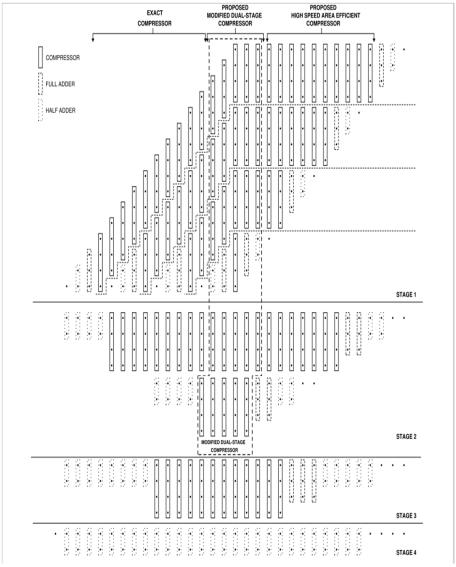

Fig: 3 Structure of 8\*8 bit Multiplier

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue IV Apr 2022- Available at www.ijraset.com

A. Flow Charts

Fig:4 Flow chart for 8\*8 bit multiplier

- 1) Multiply each bit of input1 by each bit of input2, yielding results, grouped by weight in columns

- 2) Reduce the number of partial products by stages of full and half adders and compressors until we are left with at most two bits of each weight.

- 3) Add the final result with a conventional adder.

For 16\*16 bit multiplier further two more compressors are used .Ther are High Speed Compressor and Dual stage Compressor

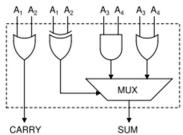

Proposed area-efficient 4:2 compressor.

Fig:5 High Speed Compressor

The proposed high speed area-efficient 4:2 approximate compressor. The compressor inputs are A1, A2, A3 and A4, outputs are CARRY and SUM. In the high speed area-efficient compressor architecture apart from the MUX, one XOR, one AND & two OR gates are required. OR and gates each need 6 transistors in CMOS logic implementation.

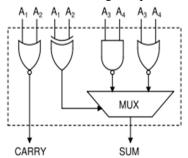

Fig:6 Dual Stage Compressor

In order to reduce the transistor count, this paper proposes an architecture with NAND and NOR gates (dual stage). The modified dual-stage 4: 2 compressor reduces area, delay and power dissipation compared to the proposed high speed area-efficient 4: 2 compressor and other compressors in the literature due to the reduction in transistor count.

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue IV Apr 2022- Available at www.ijraset.com

Fig:7 Flow chart for 16 \* 16 multiplier

In the  $16 \times 16$  bit multiplier, position 18 to position 32 employ exact compressors. The proposed modified dual- stage compressors are used where there are two stages of extended partial products for totality. For all other partial product positions lower than 17, proposed high speed area-effective 4 2 compressors, full adders .

Multiplication involves mainly 3 steps

- Partial product generation

- Partial product reduction

- Final addition

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 10 Issue IV Apr 2022- Available at www.ijraset.com

#### V. SIMULATION RESULTS

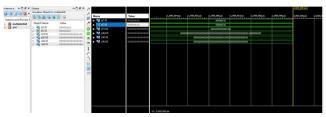

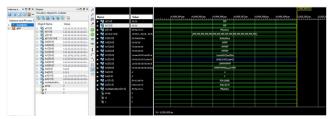

The 8 \* 8 bit multiplier design and 16 \* 16 bit multiplier design is simulated by using the tool Xilinx ISE(Integrated Synthesis Environment) and the results are shown in the below

#### A. Results

Fig:8 Outputs for 8 \* 8 bit Multiplier

Fig:9 Outputs for 16 \* 16 bit Multiplier

Fig:10 Output for sub module High speed 4 to 2 compressor

Fig:11 Output for sub module Dual stage compressor

Fig 12 Output for exact compressor

#### VI. CONCLUSION

In this paper 8 \* 8 bit and 16 \* 16 bit multiplier is proposed .The 8 \* 8 bit and 16 \* 16 bit multiplier is simulated with the tool Xilinx ISE 14.7 and results are verified. Array multiplier produces more delay and this delay is reduced in column compressor technique due to Compressors Used.

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue IV Apr 2022- Available at www.ijraset.com

#### REFERENCES

- [1] K. C. Bickerstaff, E. E. Swartzlander, and M. J. Schulte, "Analysis of column compression multipliers," 15th IEEE Symposium on Computer Arithmetic, pp. 33-39, Jun. 2001.

- [2] R. W. Brodersen, A. Chandrakasan, S. Sheng, Technologies for personal communications," 1991 Symp. on VLSI circuits, Tokyo, Japan, pp. 5-9, 1991.

- [3] A. P. Chandrakasan, S. Sheng, and R. W.Brodersen, "Low-power CMOS digital design," IEEE Journal of Solid-State Circuits, vol. 27, no. 4, pp. 473-484, April 1992.

- [4] WorkshopWorking Group Reports, Semiconductor Industry Association, pp. 22-23, Nov. 17-19, 1992, Irving, Texas.

- [5] S. Chowdhury and J. S. Barkatullah, "Estimation of maximum currents in MOS IC logic circuits," IEEE Tansactions on Computer-Aided Design, vol. 9, no. 6, pp. 642-654, June 1990.

- [6] A.D. Booth, "A signed binary multiplication technique," Quart. J. Math., vol. IV, pp. 236-240, 1952.

- [7] Momeni, J. Han, P. Montuschi, and F. Lombardi, "Design and analysis of approximate compressors for multiplication," IEEE Transactions on Computers, vol. 64, no. 4, pp. 984-994, Apr. 2015.

- [8] N. R. Shanbag and P. Juneja, "Parallel implementation of a 4x4-bit multiplier using modified Booth"s algorithm," IEEE J. Solid-State Circuits, vol. 23, no. 4, pp. 1010–1013, Aug. 1988.

- [9] A. R. Cooper, "Parallel architecture modified Booth multiplier," Proc. Inst. Electr. Eng. G, vol. 135, pp. 125–128, 1988.

- [10] K.H.Chen and Y.S.Chu, "A low power multiplier with spurious power suppression technique",IEEE Trans. Very Large Scale sIntegr.(VLSI)Syst., Vol.15, no-7,pp846-850, July 2007.

- [11] J. Choi, J. Jeon, and K. Choi, "Power minimization of functional units by partially guarded computation," in proc. IEEE Int. Symp. Low Power Electron. des., 2000, pp. 131–136.

- [12] O. Chen, S.Wang, and Y. W.Wu, "Minimization of switching activities of partial products for designing low-power multipliers," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 11, no. 3, pp. 418–433, Jun. 2003.

- [13] S. Chowdhury and J. S. Barkatullah, "Estimation of maximum currents in MOS IC logic circuits," IEEE Transactions on Computer-Aided Design, vol. 9, no. 6, pp. 642-654, June 1990.

- [14] S. Devadas, K. Keutzer, and J. White, "Estimation of power dissipation in CMOS combinational circuits using Boolean function manipulation," IEEE Transactions on Computer-Aided Design, vol. 11, no. 3, pp. 373-383, March 1992.

- [15] H. Kriplani, F. Najm, and I. Hajj, "Maximum current estimation in CMOS circuits," 29th ACM/IEEE Design Automation Conference, Anaheim, CA, pp. 2-7, June 8-12, 1992.

- [16] www.wikipedia.com for Booth multiplication algorithm

- [17] "A Novel Parallel Multiply and Accumulate (V-MAC) Architecture Based On Ancient Indian Vedic Mathematics" Himanshu Thapliyal and Hamid RArbania.

- [18] Morris Mano, "Computer System Architecture", PP. 346-347, 3rd edition, PHI. 1993.

- [19] Jorn Stohmann Erich Barke, "A Universal Pezaris ArrayMultiplier Generator for SRAM-Based FPGAs" IMS-Institute of Microelectronics System, University of Hanover Callinstr, 34,D-30167 Hanover,Germany.

- [20] Moises E. Robinson and Ear Swartzlander, Jr."A Reduction Scheme to Optimize the Wallace Multiplier" Department of Electrical and Computer Engineering, University of Texas at Austin, USA

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)