# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 13 Issue: XII Month of publication: December 2025

DOI: https://doi.org/10.22214/ijraset.2025.76592

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 13 Issue XII Dec 2025- Available at www.ijraset.com

# Physical-Only Cells in ASIC Physical Design: Types, Functions and Challenges at Advanced Technology Nodes

Muskan Singh<sup>1</sup>, Mukul Anand<sup>2</sup> STMicroelectronics, Greater Noida

Abstract: Physical-only cells are non-functional layout constructs essential for manufacturability, reliability, and signoff closure in advanced ASIC designs. As technology scales to deep-submicron and advanced FinFET/GAA nodes, physical effects such as well integrity, antenna violations, IR drop, and layout-dependent effects increasingly dominate silicon behavior. This paper presents a comprehensive taxonomy of physical-only cells, explains their device-physics motivation, discusses insertion methodologies across the physical design flow, and highlights challenges and best practices at advanced technology nodes. Index Terms: Physical-only cells, well tap cells, filler cells, endcap cells, decap cells, antenna diodes, ASIC physical design, signoff closure.

#### I. INTRODUCTION

In modern ASIC physical design, logic correctness alone does not guarantee manufacturable silicon. Layout-level con- straints, well bias stability, power-grid continuity, and plasma- induced damage during fabrication require dedicated layout constructs that do not implement Boolean logic.

These constructs, known as physical-only cells, are inserted during floorplanning, placement, routing, and signoff stages using commercial EDA tools from vendors such as Synopsys and Cadence Design Systems. Incorrect insertion or omission of these cells is a leading cause of DRC, LVS, antenna, and reliability failures at advanced nodes.

#### II. CLASSIFICATION OF PHYSICAL-ONLY CELLS

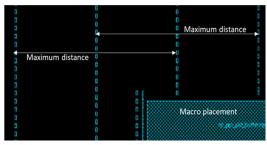

#### A. Well Tap Cells

Well tap cells connect transistor wells (N-well / P-well) to the appropriate power rails (VDD or VSS). Functions

- Prevent floating wells

- Suppress latch-up

- Stabilize body bias under IR drop and EM stress

#### Advanced-node impact

- Increased tap density requirements

- · Reduced well spacing margins

- Strong interaction with multi-height standard cells

Fig. 1 Tap Cell Distance Constraints

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 13 Issue XII Dec 2025- Available at www.ijraset.com

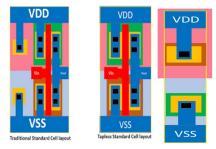

Fig. 2 Layout and Connections

#### B. Endcap Cells

Endcap cells are placed at the left and right edges of standard-cell rows.

### Functions

- Terminate diffusion and well regions correctly

- Avoid DRC violations at row boundaries

- Preserve continuity of power rails

Endcap cells are mandatory at all nodes and are technology- specific.

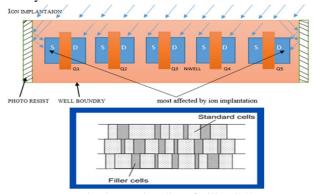

#### C. Filler Cells

Filler cells occupy unused whitespace between functional standard cells. Functions

- Maintain continuous VDD/VSS rails

- Preserve well and substrate uniformity

- Avoid lithography and CMP issues

#### Advanced-node challenges

- Multiple filler widths

- Double-patterning and EUV compatibility

- Impact on parasitic extraction accuracy

Fig. 3 Functionality of Filler Cells

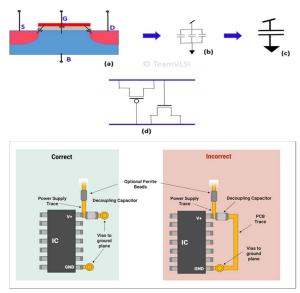

#### D. Decoupling Capacitor (Decap) Cells

Decap cells introduce intentional capacitance between VDD and VSS.

#### **Functions**

- Reduce dynamic IR drop

- Suppress simultaneous switching noise

- Improve power-grid stability

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 13 Issue XII Dec 2025- Available at www.ijraset.com

#### Trade-offs

- · Area overhead

- Leakage increases at advanced nodes

- Overuse can degrade timing

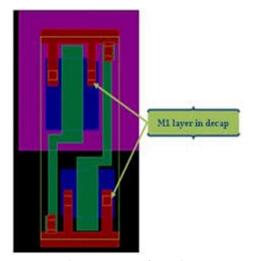

Fig. 4 Basic Circuit and Function of Decap Cells

Fig. 5 Layout Information

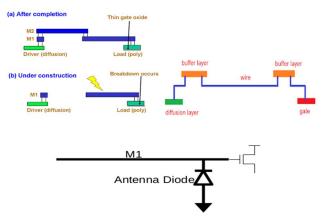

#### E. Antenna Diode Cells

Antenna diode cells protect thin gate oxides during metal etching.

#### **Functions**

- Discharge accumulated plasma charge

- Prevent gate oxide breakdown

### Advanced-node issues

- Very strict antenna ratios

- Post-route legalization complexity

- Leakage and timing impact

# International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 13 Issue XII Dec 2025- Available at www.ijraset.com

Fig. 6 Theory and Application of Antenna Diode

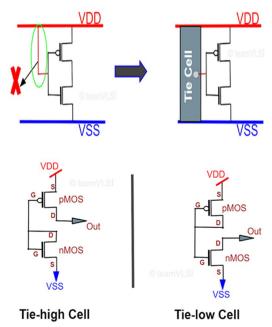

#### F. Tie-High and Tie-Low Cells

Tie cells provide constant logic '1' or '0' connections.

Why tie cells instead of direct VDD/GND?

- Lower leakage

- Controlled drive strength

- Improved reliability

#### Constraints

- Limited fanout

- Placement proximity requirements

Fig. 7 Tie Cell Theory and Circuit

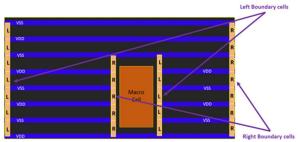

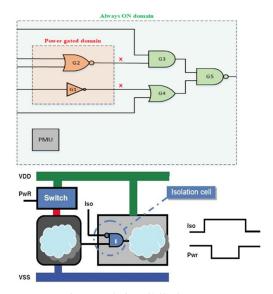

#### G. Boundary and Isolation Cells

Boundary and isolation cells are used at:

- Block boundaries

- Voltage-domain crossings

- Hierarchical SoC assembly

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 13 Issue XII Dec 2025- Available at www.ijraset.com

They prevent well interference and latch-up across domains

Fig. 8 Boundary Cell Placement

Fig. 9 Isolation Cell Placement

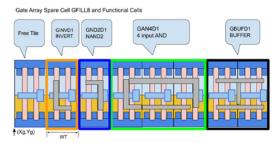

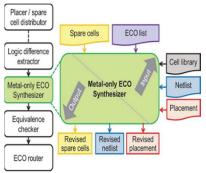

#### H. Metal-Only ECO Cells

Metal-only ECO cells enable late-stage fixes without changing diffusion layers. Applications

- Timing fixes at signoff

- Functional ECOs

- Risk reduction after tapeout freeze

### Limitations

- Routing congestion

- Limited drive options

Fig. 10 Spare Cell Functionality

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 13 Issue XII Dec 2025- Available at www.ijraset.com

Fig. 11 ECO Implementation Flow

#### III. PHYSICAL-ONLY CELL INSERTION ACROSS THE PD FLOW

### TABLE I PHYSICAL-ONLY CELL USAGE ACROSS PHYSICAL DESIGN FLOW

| Physical Design | Physical Cells         |

|-----------------|------------------------|

| Stage           | Inserted               |

| Floorplanning   | Endcap, well tap       |

| Placement       | Filler, tap, tie cells |

| CTS             | Decap, filler          |

| Routing         | Antenna diodes         |

| Signoff / ECO   | Metal-only ECO         |

|                 | cells                  |

#### IV. CHALLENGES AT ADVANCED TECHNOLOGY NODES

#### At ≤5 nm nodes:

- 1) Extremely tight layout rules

- 2) Fin quantization effects

- 3) EUV stochastic variability

- 4) Physical cells directly affect timing, power, and yield Physical-only cells are no longer passive fillers; they are signoffcritical structures.

#### V. **BEST-PRACTICE GUIDELINES**

- 1) Insert well taps early and uniformly

- 2) Avoid excessive decap clustering near clock spines

- Perform antenna checks incrementally

- 4) Validate filler and power continuity after ECOs

- Use foundry-qualified physical-only cell libraries.

#### VI. **FUTURE TRENDS**

- 1) AI-driven physical cell insertion

- Context-aware decap optimization 2)

- Unified logical and physical ECO strategies

- Foundry-aware rule-adaptive cell deployment

#### VII. CONCLUSION

Physical-only cells form the backbone of manufacturable ASIC layouts. As physical effects dominate advanced-node designs, careful understanding and disciplined deployment of these cells are mandatory for first-pass silicon success.

# International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 13 Issue XII Dec 2025- Available at www.ijraset.com

#### **REFERENCES**

- [1] S. Nassif, "Design for variability in DSM technologies," IEEE Micro, vol. 20, no. 6, pp. 62-71, 2000.

- [2] A. B. Kahng et al., VLSI Physical Design: From Graph Partitioning to Timing Closure, Springer, 2011.

- [3] Synopsys Inc., ICC2 User Guide: Physical-Only Cell Handling, 2022.

- [4] Cadence Design Systems, Innovus Implementation System User Guide, 2023.

- [5] J. Cong and M. Xie, "Physical design challenges in nanometer tech- nologies," IEEE Trans. VLSI Syst., 2005.

- [6] D. Boning and S. Nassif, "Process variation modeling," IEEE Design & Test, 2010.

- [7] ITRS, International Technology Roadmap for Semiconductors, 2015.

- [8] M. Li et al., "Antenna effect mitigation," Proc. ICCAD, 2017.

- [9] S. R. Nassif, "Power grid analysis benchmarks," Proc. DAC, 2008.

10.22214/IJRASET

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)