IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 13 Issue: V Month of publication: May 2025 DOI: https://doi.org/10.22214/ijraset.2025.70352

www.ijraset.com

Call: 🕥 08813907089 🔰 E-mail ID: ijraset@gmail.com

# Realisation of Digital Memory Unit Using VHDL And FPGA

Soumen Pal<sup>1</sup>, Srabani Roy<sup>2</sup>, Jaga Bandhu Saha<sup>3</sup>, Rajaasree Naskar<sup>4</sup>, Surjo Saha<sup>5</sup>, Moumi Saha<sup>6</sup>

<sup>1</sup>AssistantProfessor, <sup>2</sup>Technica1Assistant, <sup>3, 4, 5, 6</sup>Student, Department of Electronics & Communication Engineering, NaruIa Insfitute of Technology, Kolkata, India

Abstract: The design process involves defining the RAM's architecture using VHDL, which includes address decoding, data input/output mechanisms, and clock synchronization. The functionality is validated through simulation using VHDL simulation tools, ensuring accurate read and write operations. The synthesized design is then implemented on an FPGA kit, leveraging itsreconfigurabilitytorealizetheRAM'shardware.Testingisperformed toverifythefunctionality inareal-time environment, examining parameters such as read/write latency and data integrity. This project demonstrates the practical application of digitaldesignprinciples, VHDL programming,andFPGAimplementationtechniques. The 128•8 RAM module serves asafoundational component forlarger digital systems,offering scalable memory solutions forembedded and computational applications.

Index terms—Single-PortRAM,VHDL, FPGA, Memory Design, 128•8 Memory, Hardware, Description Language (HDL), FPGA Kit, Reconfigurable Logic.

# I. INTRODUCTION

Inmoderndigitalsystems, memoryplaysacrucial role instoring and retrieving data efficiently. Amongvarious memory types, RAM (Random Access Memory) is widely used due to its fast read and write operations. A Single-Port RAM (SPR) is a memory configuration where both read and write operations cannot occur simultaneously but can be performed independently at different times. This makes single-port RAM an ideal solution for systems that require simple memory architectures with low resource consumption, such as embedded systems, microcontrollers, and digital signal processing applications.

RAM allows your computer to perform many of its everyday tasks, such as loading applications, browsing the internet, editing a spreadsheet, or experiencing the latest game. Memory also allows you to switch quickly among these tasks, remembering where you are inone task when you switch to another task. In the context of FPGA (Field-Programmable GateArray) design, VHDL (VHSIC Hardware Description Language) is a popular language used to describe and implement digital circuits. This design aims to implementa Single-PortRAM memory unit using VHDL for an FPGA-based system. The Single-PortRAM will have a single access portfor both reading and writing data, controlled by a write enable signal. FPGAs are programmable siliconchips with a collection of programmable logic blocks surrounded by Input/Output blocks that are put of the other through programmable interconnect resources

tobecomeanykindofdigital circuitorsystem. The FPGA will be used to store data at specific memory locations, allowing read and write operations to occur based on control signals and the system clock. The objective of this design is to create a simple, efficient memory block that can be easily incorporated into FPGA systems requiring non-simultaneous read/write operations. The design will feature key components such as the address bus, data bus, clock signal, and write enables ignal, which will be managed in the VHDL code to implement the desired functionality. [4]

# **II. LITERATURE SURVEY**

# A. Key concepts and Terminology

# VHDL(VHSICHardwareDescriptionLanguage):-

VHDLisahardwaredescription language usedtomodelanddesigndigitalsystems.Itallowsengineerstodescribe thebehaviorand strucmre of electronic systems at various levels of abstraction. VHDL is widely used in the design, simulation, and synthesis of digital circuits for FPGAs and ASICs.

#### B. Key Features of VHDL:

• Concurrency: VHDLinherentlysupportsconcurrent execution, making its uitable for modeling parallel digital circuits.

# International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 13 Issue V May 2025- Available at www.ijraset.com

- Modularity: Supportsmodulardesign, makingcomplexdesignseasiertomanage.

- SimulationandSynthesis:Allowsfunctionalsimulationtoverifydesigncorrectnessandsynthesistoimplementthedesignon hardware.

- PlatformIndependence:PortableacrossvarioussimulationtoolsandFPGA/ASICplatforms.

- RichDataTypes:Supportsuser-defineddatatypes,arrays,andenumerations.[1]

#### C. DigitalMemoryUnit:-Single-PortRAM Digital Memory:

Adigitalmemoryunitstoresbinarydatathatcanberead orwritten. Asingle-portRAM isatype of memory where asingleaccess point is used for both reading and writing operations.

Single-PortRAMFeatures:

- 1) .Size:Fora128Xconfiguration,thememoryhas128locations,eachstoring8-bitdata.

- 2) Addressing: 128 locations require a 7-bit address ( $2^7 = 128$ ).

- 3) DataBusWidth:8bitsfordatainanddataout.

- 4) .ControlSignals:

- WriteEnable (WE):Specifieswhethertowriteorreaddata.

- Clock(CLK):Synchronizesoperations.

- ChipEnable(CE):Activatesthememoryunit.

#### D. SynthesisofDigitalCircuits

Synthesis:

Synthesisistheprocessofconvertingahigh-level hardwaredescription(e.g., VHDLcode)intoalow-levelimplementationsuitable for FPGA or ASIC hardware.

StepsinSynthesis:

- 1) RTL(RegisterTransferLevel)Description:High-leveldesigndescriptionusingVHDLorVerilog.

- 2) LogicOptimization: Optimizes Booleanexpressions and minimizes logicgates.

- *3)* TechnologyMapping:MapsthedesigntothetargetFPGAorASICtechnology.

- 4) PlacementandRouting: Allocatesphysicalresources(LUTs,flip-flops)andconnectsthemontheFPGA.[7]

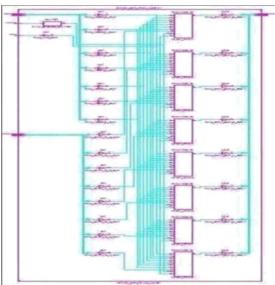

Fig1:TechnologySchematic

# III. RAM DESIGN USING YHDL

#### A. Basic Memory Structures

Earlystudies focused on the fundamental design of memory units such as ROM and RAM, out lining the architecture and operational principles (Wakerly, 2000; Mano, 1993). [9][10]

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 13 Issue V May 2025- Available at www.ijraset.com

# B. VHDLin Digital Design

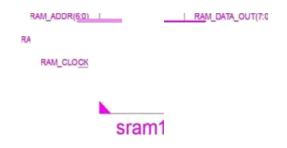

Perry(2002) and Ashenden (2008) provided comprehensive guides on using VHDL for digital design, highlighting its syntax, semantics, and application in designing various digital components, including memory units. [11][12] sram1

Fig. 2 shows the RTLS chematic of Single PortRAM memory.

# **IV. DESIGN SPECIFICATIONS**

Fortheimplementationofthe128x8single-portRAMin VHDL,thefollowingdesignspecifications are considered:

- 1) RAM\_CLOCK: the clocksignal for sequentially writing data to the single-port RAM.

- $2) {\rm RAM\_DATA\_IN:8-bit in put data to be written to RAM at the provided in put address RAM\_ADDR when it is enabled.}$

- *3)* RAM\_WR:WriteenablesignalforwritingtoRAM,onlyifRAM\_WR=1,RAM\_DATA\_INiswrittentotheRAMattherisingedgeof the clock signal.

- 4) RAM\_ADDR: 6-bitAddresswhere8-bitinputdataare written to anddata are read out. 5.RAM\_DATA\_OUT:8-bitoutput data read out fromtheprovided inputaddressRAM\_ADDR.[12]

Fig3:SimulationresultofsingleportRAMinVHDL.

#### V. FPG ARE ALIZATION

In this design, we have implemented the 1288 Single-Port RAM on a generic FPGA platform using VHDL. Below are the steps involved in the design and implementation process:

- VHDLDesign: Thememory unitwasdesignedusingVHDLcode, which defines the behavior of the RAM. The design involves specifying thememory size (128 locations, each with 8 bits), address bus width, databus width, and control signals such as read/write enable.

- EntityDeclaration:Thedesignstarts with the entity declaration, which defines the input and output ports. The inputs include the clock, reset, address, data input (for writing), and control signals.

- Architecture: Thearchitecture sectiondescribestheinternallogic. Aprocess block is used to handle theread/write operations, triggered by the clock and control signals.

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 13 Issue V May 2025- Available at www.ijraset.com

- 2) Synthesis and Simulation: After writing the VHDL code, the design is synthesized using FPGA synthesis tools (e.g., Xilinx Vivado or IntelQuartus). The simulation of the design is carried outusing tools like ModelSim toverify the functionality of the RAM.

- Testbench Creation: Atestbench iscreatedtosimulatethebehavioroftheRAM.Thistestbenchappliesvariousaddress, data,andcontrolsignals totestthereadandwriteoperations under different conditions.

- *3)* FPGA Implementation: Once the design passes simulation, the synthesized bitstream isloaded onto an FPGA board (e.g., Xilinx or IntelFPGA). The FPGA kitisconnected to a testing setup where input values are applied, and the output is verified.[6]

# VI. APPLICATIONS OF SINGLE PORTRAM

Single-portRAMis essentialinmanyembeddedsystemdesigns, especiallywheresimplememory solutions are required. The applications include:

- 1) EmbeddedSystems:Single-portRAMis oftenusedin microcontrollers, where simple data storage and retrievalare needed for operations lilce data buffering and stack management.

- 2) DataStorage:Thel28•8memorycan beused inapplicationslikedatalogging, caching,ortemporarystorageforprocessingina varietyofelectronicdevices, includingIoTdevices.

- 3) ControlSystems: Incontrolsystems, where fast access to memory is required to store and retrieves ensord at a, a single-port RAM can efficiently handle these tasks.

- 4) SignalProcessing:InFPGA-based signalprocessingsystems, a single-port RAM can be used to store intermediate results, such as in digital filters or Fourier transforms.

- 5) Prototyping:FPGA implementationsofRAM modules allowdesigners toquickly prototype systems, makingsingle-portRAM a valuable resource in early-stage product development.

#### VII.CONCLUSION

In this paper, we have successfully designed and implemented al 28•8Single-Port RAM using VHDL and an FPGAkit. The design leverages VHDL's ability to describe hardware behavior, while the FPGA provides the hardware platform to validate the design. The system performs read and write operations correctly, and the design can be expanded or integrated into more complex systems. This implementation serves as a useful memory solution for embedded systems, prototyping, and applications requiring efficient data storage.

#### VIII. FUTURE ENHANCMENTS

The current design of a single-port RAM can be enhanced in several ways to meet evolving demands indigital systems. One of the most promising enhancements is the development of a dual-port RAM, enabling simultaneous read and write operations, which is critical for applications requiring high-speed data processing, such as video processing or real-time analytics. Additionally, the design can be made more flexible by introducing parameterization, allowing users to dynamically configure memory size during synthesis to suit specific application requirements.

Incorporatingerrordetectionandcorrection(ECC)mechanisms,suchasHammingCode,wouldsignificantlyenhancethereliability of the RAM, ensuring data integrity in critical systems. Furthermore, power optimization techniques, like clock gating, could be implemented to reduce energy consumption, making the design moresuitable for energy-sensitive applications. To improve data transfer efficiency, support for burst read and write operations could be added, which is particularly advantageous in high-speed communicationsystems.

Anotherareaofenhancement liesin memory initialization, where the RAM could be preloaded with specific data from an external file, improving itsutilityin simulations and practical applications. Advanced integration could also be achieved by adding support forwidely used communication protocols like AXI or Avalon, allowing seamless connectivity with modem SoCarchitectures. Built- inself-test (BIST) mechanisms could furtherenhance the design by enabling automated testing and debugging, ensuring reliability during deployment.

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 13 Issue V May 2025- Available at www.ijraset.com

Formore complex systems, the RAM couldbe integrated with soft-core processors, such asXilinx MicroBlaze orIntel NiosII, to provide embedded processing capabilities. Finally, performance can be optimized by leveraging FPGA-specific features, such as usingblockRAMs(BRAMs) or distributed RAMs, to improve speed and resource utilization. These enhancements not only expand the scope of applications but also improve the performance and reliability of the RAM design. [2][5]

#### REFERENCES

- [1] Bhaskar, D. (2009). VHDLPrimer (3rded.). Pearson Education.

- [2] Xilinx.(2023).VivadoDesignSuiteUserGuide. Retrieved from https://www.xilinx.com

- [3] .Patel, P., & Shah, S. (2015). FPGAPrototyping ByVHDLE xamples: XilinxSpartan-3Version. Wiley.

- [4] IEEEStd1076-2008(VHDL).VHDLLanguage ReferenceManual.

- [5] Rabaey, J., Chandrakasan, A., & Nikolic, B. (2009). Digital Integrated Circuits: A Design Perspective (2nd ed.). Pearson Prentice Hall.

- [6] Z.Ullah,M.K.Jaiswal,Y.C.ChanandR.C.C.Cheung, "FPGAImplementationofSRAM-basedTernaryContentAddressable Memory," IEEE26th Int. Parallel and Distributed Symposium Workshops&PhdForum, pp.383-388, 2012.

- [7] M.M.Soni, P.K.Dakhole, "FPGAImplementation of Content Addressable Memory Based Information detection System," IEEE Xplore, 2014.

- [8] L.M.lonescu, A.G.Mazare and G.Serban, "FPGAImplementationofanAssociative ContentAddressable Memory," Int. Conference on Applied Electronics, September, 2011.

- [9] Wakerly, J.F. (2000). Digital Design. Principles and Practices. 3rded. Prentice Hall.

- [10] Mano, M. M. (1993). Digital Design. 2nd ed. Prentice Hall.

- [11] Perry, D. (2002). VHDL.' Piogiamming by Example. 4 thed. McGraw-Hill.

- $\label{eq:constraint} \end{tabular} \end{tabular} \end{tabular} \end{tabular} \end{tabular} \end{tabular} \end{tabular} A shenden, \end{tabular} P.J. (2008). The Designer's Guideto VHDL. 2nded. Morgan Kaufmann.$

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)