# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 10 Issue: IX Month of publication: September 2022

DOI: https://doi.org/10.22214/ijraset.2022.46823

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue IX Sep 2022- Available at www.ijraset.com

### Smart Implementation of SS Hybrid Single Electron Model and its Simulation using MATLAB

Sanjay Bhadra<sup>1</sup>, Soumyendu Banerjee<sup>2</sup>, Sougata Das<sup>3</sup>, Harshadeep Mukherjee<sup>4</sup> Shrestha Mukherjee<sup>5</sup> <sup>1, 2, 3, 4, 5</sup>Department of Electrical Engineering, University of Engineering and Management Kolkata, India

Abstract: The authors present a novel simulation technique for simulating nanodevices. Single Electronics (SE) is a blessing for both business and academia in the post-CMOS age. Due to SE's inherent drawbacks, including its low gain, unpredictable back ground charge creation, and demand for a very low room temperature during manufacturing, it hasn't yet been decided whether it will be the only mode to replace CMOS. This SE-CMOS hybridization is anticipated to bring about great satisfaction in the development of practical and more dependable nanodevice constructions. The delicate part is that this hybridization necessitates the use of two unique simulators in order to replicate a single model. Unfortunately, this causes hybrid model simulation to be quite difficult. On the other hand, the idea of macro-modeling the hybrid models for the purpose of simulation is in fact beneficial. In this instance, the authors utilized one such macro-model to improvise the hybrid SE model, and a very new SS hybrid SE model is subsequently produced. The majority of the research on hybrid SE that has been published so far supports the use of two different simulators, such as SPICE and SIMON; both are sequentially utilized to simulate one particular model, which ultimately takes a lot of time. The authors take a step ahead in this section by simulating the proposed SS hybrid SE model in MATLAB. They predict that this model may eventually be added to SIMULINK's SIMSCAPE since it is more accurate, less time-consuming, and easier to understand.

Keywords: Single Electronics; Hybrid Single Electronics; SS (Sanjay Soumyendu) Model; Macro Modelling; SIMSCAPE.

#### I. INTRODUCTION

Downsizing MOSFETs and scaling them in nm span imperiled unwanted short-channel effects, stochastic quantum effects, high power consumption tenacity, high power leakage factor, increased thermal noise. Beyond all, the technological limitations augmented the Red Brick Wall of CMOS technology [1]. This led to deepened research inquisitiveness in reliability analysis, transitive fan-in attributes of new nm devices. Hypothesizing the prompt dissolution of CMOS technology Researchers coxed new device stimulating principle and in accord novel post CMOS technologies were empirically demonstrated. SE made transistors in this category possess an excellent candidature in obtaining triumph over other successor technologies such as Carbon Nano Tubes (CNT), Resonant Tunneling Devices (RTD), Rapid Single Flux Quantum (RSFQ) and Quantum Dots (QD) [2] like devices. Single Electron Transistor (SET) [3] is a highly charge sensitive device that mimics all physiognomies of MOSFET and is capable of transporting information using one or merely few electrons. Thus it is a promising future-ready nano electronic device having mobility of a speed almost equal to electron speed. Besides, charge sensitivity and low power consumption are considered added virtue of SET. Structurally SET is a quantum device that sways upon electron tunneling phenomena and involves oxidation for switching transition. The power consumption and the heat dissipation reasonably diminish along with the tunneling of electrons in Coulomb Blockade. Persuaded by such tremendous competency SETs now are molded to fabricate logic circuits and even more they are applicable in charge sensor, detection of infrared radiation, ultrasensitive microwave detector, supersensitive electrometer, single-electron Spectroscopy and so on [4]. Meanwhile the proficiency in fundamental fabrication oriented SET revealed intrinsic short comings of SET such as low gain, high output impedance, random background charge and extreme low room temperature operational requirements. But to sustain with the tidal growth of electronic industry SET is to be made omnipresent in future ICs. In view of such prerogative of SETs, researchers initiated amalgamating SET with conventional CMOS and this is considered as a bench-mark research that can postulate novel heuristic reinforcement both for SET and CMOS technology. Hereby the notion of Hybrid CMOS SET (HCS) [5] was administrated and it catered firm pursuit in device research vicinity. Simulation of such prototypes is the key to success for future implementation of HCS modeling. However, simulation of hybrid models pre-requisite two solely distinctive simulating tools and subsequently such simulations are quite painstaking and accuracy of such simulation is linked to larger simulation time. Hence macro modeling of SE is well thought-out as a cognitive remedial to such lingering simulations. The authors here protruded a HCS macro modeling metaphor and has categorically deliberated its testimonials using SIMSCAPE of MATLAB. It is further manifested that offerings of the newly proposed model tunes up in rhythm with physical models proposed by Sarkar et.al [6].

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 10 Issue IX Sep 2022- Available at www.ijraset.com

#### II. MACRO MODELLING OF SINGLE ELECTRON

The SE system is mounted on tunneling effect and the Coulomb Blockade phenomena. Logically the fabrication of SE circuits tolerate high cost and large processing time alike complications. To overcome such glitches, several attempts has been opted. Efforts are on to make flexible computerized designs with concise simulation time. In this aspects different models are developed continually based on tunneling and quantum mechanics. A number of these simulators are SENECA by Fonseca et al. [7], MOSES by Chen et al. [8], SIMON by Wasshuber et al. [9]. Essentially all of them exploit Monte-Carlo methods for probability calculation of the Coulomb Island in the circuit and thus it takes a large simulation time. In this regard 'Macro Modeling was conceived by Yu e al. [10] which can be simulated in SPICE and also consumes less time compared to its predecessors. Customizing this approximation of macro-modelling the SEs the authors incorporated the macro model of SE in HCS. Eventually, the simulation exhaustion is lessened and accuracy of such designs tender maximized throughput. The authors here in-situ with similar macro models conceived a new hybridized SET-MOS switching device with its macro model namely SS (Sanjay Soumyendu) model.

#### III. FRAME WORK OF THE SS MODELING

The same cited Yu model while simulated by SPICE diverged from its SIMON based simulation results. The variety of Yu et al., model lies in the Drain current  $I_{ds}$  that increases linearly with the Drain to Source voltage  $V_{ds}$  whereas in pragmatically  $I_{ds}$  increases exponentially with the  $V_{ds}$  in Coulomb Blockade region. Besides empirically it has been revealed that base line of  $I_{ds}$  increases as Gate to Source voltage  $V_{gs}$  increases in Coulomb Oscillation properties. To overcome this problem Wu and Lin [11] amended a new model namely 'Wu Lin SET macro model' where two diodes are connected face to face to block the current flow from the gate to source terminal, thereby mimicking the SE occurrences. It includes the orthodox theory of SE to analyze the circuits. The value of R1 and R2 can be recorded from

R1 = CR1 + CR2 \* cos(CF1 \* VG) (1)

R2 = CVp/(CI2-(2CVP/RI(VG))) (2)

where CR<sub>1</sub>, CR<sub>2</sub>, CV<sub>P</sub>, CI<sub>2</sub>, CF<sub>1</sub> are atypical parameters to fit the input (voltage) and output (current) characteristics at various gate voltages.

A deep insight in all across models the tunneling time is simulated to be 'zero' i.e. expediently the calculation was not viable. To exclude such hindrances Reza Karinian et al. [12] implied another advanced macro-model in which, quantizer blocks were used to calculate the tunneling time; this certainly makes the macro-model more legitimate.

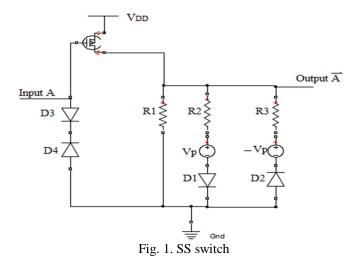

Authors truly motivated by such conceptions improvised SS switching circuit alike Fig. 1; the PMOS is connected in series with the SET macro-model. This particular switch is to be compared with other post CMOS HCS models. Here one significant partial difference is that the SETMOS switch attempted by Sarkar et al., [13] are connected in parallel and thereby the propagation delay in the circuit cannot be ruled out completely. The same said factor is considerably eliminated in SS switch. Moreover, SS switch is merely simulated in one platform (software).

In the subsequent section the authors emphasis upon the reliability of the proposed SS model and chronologically testifies the mobility criterion using SIMSCAPE of MATLAB.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 10 Issue IX Sep 2022- Available at www.ijraset.com

#### IV. ORIENTATION OF SS MODEL USING MATLAB

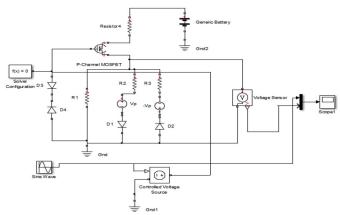

The authors largely counted on SIMSCAPE for modeling the SS model as depicted in figure below (Fig.2). For simplicity and straight forwardness in this inverter model a PMOS is connected just on top of the macro-model of a SET. The input is obtained from the connecting point of the gate of PMOS and SET. The output is taken from the midpoint of drain end and it is add-on to the 'Scope' of the MATLAB [14-20] to avail the desired output as revealed in Fig 2.

Fig. 2. MATLAB based SS switch made Inverter

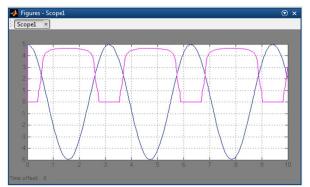

Fig. 3. SS switch made inverter output w.r.t given input

Stringent analysis of the resultant waveform in Fig. 3 reveals that the threshold voltage is 2.2V i.e. when the input voltage is below the 2.2V then output is 'high' and when input voltage is above 2.2V then output is 'low' which substantiates the inverter operation.

#### V. CONCLUSION

The macro modeling of SE transverse nano device engineering in to a lucrative symphony in future-ready IC topology. The galaxy of single SE is taken forward here to substantiate the SS model. Undoubtedly such modeling is pivotal and forms the basis of advance computing in SE topology as well as it ushers promising ventures in post CMOS era. Subsequently MATLAB has been pondered over to substantiate the simulation in one platform and making it quite straight forward and easy for the Researchers. The results obtained justifies the aspects of HCS likewise low power consumption, high speed of response, low power dissipation. Last but not least the authors here advocate for inclusion of such model in SIMSCAPE of MATLAB so that logical synthesizing can be achieved with linearity.

#### REFERENCES

- [1] H.-S.P. Wong, D.J. Frank, P.M. Solomon, "Nanoscale CMOS", IEEE Proceedings, vol. 87, August 2002, pp. 537-570.

- [2] Dr. J. Gope (MIEEE, CE) & Snigdha Chowdhury (Kolay), "Exploration of single spin logic (SSL) based expandable hardware design", International Journal of Scientific & Engineering Research, vol. 7, March 2016, pp. 146-148.

- [3] Vinay Pratap Singh, Arun Agrawal, Shyam Babu Singh, "Analytical discussion of single electron transistor (SET)," International Journal of Soft Computing and Engineering (IJSCE). vol. 2, 2012.

- [4] Anil Kumar and Dharmender Dubey, "Single electron transistor: applications and limitations", Advance in Electronic and Electric Engineering, vol. 3, 2013, pp. 57-62.

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue IX Sep 2022- Available at www.ijraset.com

- [5] S. Mahapatra, V.Vaish, W. Wasshuber, "Analytical modelling of single electron transistor for hybrid CMOS SET analog IC design," IEEE Transaction On Electron Device, vol. 51, pp. 1772-1782, October 2004.

- [6] Arpita Ghosh, Amit Jain, N. Basanta Singh, Subir Kumar Sarkar, "A new SPICE macro model of single electron transistor for efficient simulation of single-electronics circuits", Springer Science+Business Media, New York, 2015, pp. 653-662.

- [7] L. R. C. Fonseca, A. N. Korotkov, and K. K. Likharev, "SENECA: a new program for the analysis of single-electron devices," VLSI vol. 6, 1998, pp. 57-60.

- [8] Andreas Eiselel, Christian Federmann, Herve Saint-Amand, Michael Jellinghaus, Teresa Herrmann, Yu Chen, "Using moses to integrate multiple rule-based machine translation engines into a hybrid system", Proceedings of the Third Workshop on Statistical Machine Translation, June 2008, pp. 179–182.

- [9] Christoph Wasshuber, Hans Kosina, and Siegfried Selberherr, "A simulator for single-electron tunnel devices and circuits", IEEE Transactions On Computer-Aided Design of Integrated Circuits and Systems, vol. 16, September 1997, pp. 937-944.

- [10] Y. S. Yu, H. S. Lee, and S. W. Hwang, "SPICE macro-modelling for the compact simulation of single electron circuits", Journal of the Korean Physical Society, vol. 33, November 1998, pp. S269-S271.

- [11] You-Lin Wu, Shi-Tin Lin, "An improved single electron transistor model for spice application", Nanotech, Nov 2003.pp 321-324

- [12] Mohammad Reza Karimian and Massoud Dousti, "A new SPICE macro-model for the simulation of single electron circuits", Journal of the Korean Physical Society, vol. 56, April 2010, pp. 1202-1207.

- [13] Anindya Jana, Rajatsuvra Halder, J.K.Singh, Subir Kumar Sarkar, "Design and implementation of a hybrid SET-CMOS based sequential circuits", Journal of Nano- and Electronic Physics, vol. 4, 2012, pp. 02004-1 -02004-5.

- [14] S. Banerjee and G. K. Singh, "Quality Aware Compression of Multilead Electrocardiogram Signal using 2-mode Tucker Decomposition and Steganography," Biomed. Sig. Proc. Cont., vol. 64, 102230, 2020.

- [15] S. Banerjee and G. K. Singh, "Monte Carlo Filter based Motion Artifact Removal from Electrocardiogram Signal for Real-time Telecardiology System," IEEE Trans. Instrum. Meas., vol. 70, 4006110, 2021.

- [16] S. Banerjee and G. K. Singh, "A new approach of ECG steganography and prediction using deep learning," Biomed. Sig. Proc. Cont., vol. 64, 102151, 2021.

- [17] S. Banerjee and G. K. Singh, "A Robust Bio-signal Steganography with Lost-data Recovery Architecture using Deep Learning," IEEE Trans. Instrum. Meas., vol. 71, pp. 1-10, 2022, 4007410, 2022.

- [18] S. Banerjee and G. K. Singh, "A new approach of ECG steganography and prediction using deep learning," Biomed. Sig. Proc. Cont., vol. 64, 102151, 2021.

- [19] S. Banerjee and G. K. Singh, "Quality Guaranteed ECG Signal Compression using Tunable-Q Wavelet Transform and Möbius Transform based AFD," IEEE Trans. Instrum. Meas., vol. 70, 4008211, 2021.

- [20] S. Banerjee and G. K. Singh, "A new real-time lossless data compression algorithm for ECG and PPG signals," Biomed. Sig. Proc. Cont., vol 79, Part 1, 104127, 2023.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)