# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 10 Issue: I Month of publication: January 2022

DOI: https://doi.org/10.22214/ijraset.2022.39759

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 10 Issue I Jan 2022- Available at www.ijraset.com

### Design, Implementation & Performance of Vedic Multiplier Based on Look Ahead Carry Adder for Different Bit Lengths

Vaishali Sharma<sup>1</sup>, R. P. Agarwal<sup>2</sup>

<sup>1</sup>Research Scholar, Dept.of Electronics & Communication Engineering, Shobhit Deemed University, Meerut, U.P., India <sup>2</sup>Professor, Dept.of Electronics & Communication Engineering, Shobhit Deemed University, Meerut, U.P., India.

Abstract: This paper proposed the layout of Vedic Multiplier based totally on Urdhva Trigbhyam approach of multiplication. It is most effective Vedic sutras for multiplication. Urdhva triyagbhyam is a vertical and crosswise approach to discover product of two numbers. Multiplication is an essential quintessential feature in arithmetic logic operation. Computational overall performance of a DSP device is limited via its multiplication overall performance and since, multiplication dominates the execution time of most DSP algorithms. Multiplication is one of the simple arithmetic operations and it requires extensively extra hardware assets and processing time than addition and subtraction. Our work is to compare different bit Vedic multiplier structure using carry look ahead adder technique.

Keywords: Carry Look Ahead Adder, Urdhva Trigbhyam, DSP algorithms, Vedic Multiplier

#### I. INTRODUCTION

Multipliers play an vital role in today's digital signal processing and various other applocations. In excessive overall performance structures such as microprocessor, DSP and many others addition and multiplication of two binary numbers is necessary and most regularly used arithmetic operations. Statics suggests that greater than 70% instructions in microprocessor and most of DSP algorithms operate addition and multiplication. So, these operation dominates the execution time. That's why, there is need of excessive pace multiplier. The demand of excessive pace processing has been growing as a end result of increasing computer and signal processing applications. A standard technique of array multiplication shown below:

|    |         |         |         | A3      | A2      | Al      | A0      | Inputs           |

|----|---------|---------|---------|---------|---------|---------|---------|------------------|

|    |         |         | X       | B3      | B2      | Bl      | B0      | Inputs           |

|    |         |         | C       | B0 x A3 | B0 x A2 | B0 x A1 | B0 x A0 |                  |

|    |         | +       | B1 x A3 | B1 x A2 | Bl x Al | B1 x A0 |         |                  |

|    |         | C       | sum     | sum     | sum     | sum     |         |                  |

|    | +       | B2 x A3 | B2 x A2 | B2 x A1 | B2 x A0 |         |         | Internal Signals |

|    | C       | sum     | sum     | sum     | sum     |         |         |                  |

| +  | B3 x A3 | B3 x A2 | B3 x A1 | B3 x A0 |         |         |         |                  |

| C  | sum     | sum     | sum     | sum     |         |         |         |                  |

| Y7 | Y6      | Y5      | Y4      | Y3      | Y2      | Y1      | Y0      | Outputs          |

Fig.1 Array Multiplication

#### II. PROPOSED SYSTEM

The proposed gadget is used to limit the raise propagation time and to optimize the hardware complexity degree for Vedic multiplier operation. The proposed device is to put in force vertical and cross-wise equation primarily based logical distinct bits multiplier operation.

Vedic Mathematics Swami Bharati Krishna Tirtha, known as a set of sixteen Sutras (aphorisms) and thirteen Sub-Sutras (Corollaries) from the Atharva Veda. He developed approach and strategies for amplifying the ideas contained in the aphorisms and their corollaries, and referred to as it Vedic Mathematics. In Vedic Mathematics partial products are generated in parallel, which will increase the pace of operation. In this paper we are proposing a format for accumulation of these intermediate products, with minimal delay Multiplication if an operation much needed in Digital Signal Processing for more than a few applications. This paper places ahead a excessive pace Vedic multiplier which is efficient in phrases of speed, making use of Urdhva Tiryakbhyam, a sutra from Vedic Math for multiplication.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue I Jan 2022- Available at www.ijraset.com

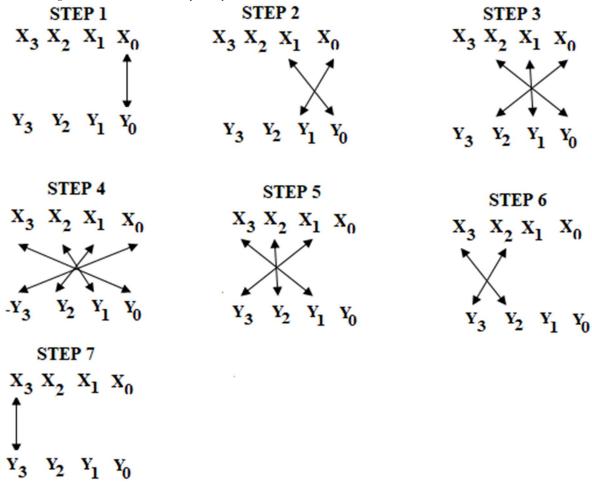

#### A. Multiplication Algorithim For Urdhva Tiryakbhyam Sutra

Fig2: Algorithm of UT sutra

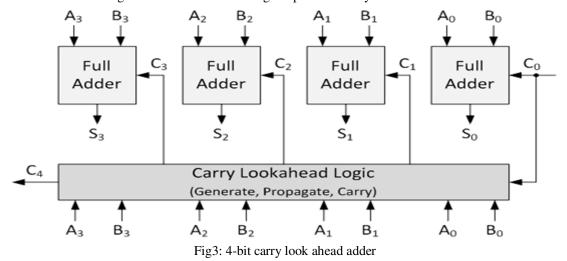

#### B. Carry Look Ahead Adder

"A carry-look ahead adder(CLA) is a type of fast parallel adder used in digital logic to calculate the carry signals in advance from the input signals." They reduce carry propogation time and implement addition of binary numbers. It is also known as: carry look ahead generator or fast adder or carry predictor. It is an improvement over 'Ripple carry adder circuit'.

CLA is used to eliminate the wastage of time occur at each stage of parallel binary adder.

25

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 10 Issue I Jan 2022- Available at www.ijraset.com

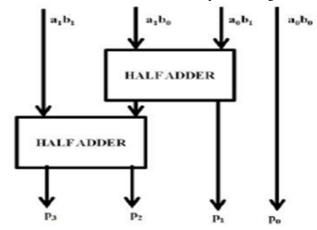

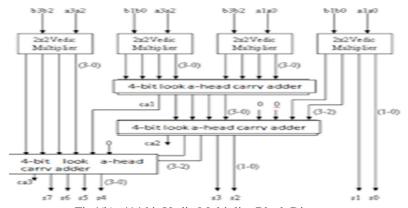

#### C. Vedic Multiplier

Multiplication strategies that many of processors are using nowadays has stimulated by way of Vedic multiplier delivered in Indian Vedas with distinctive sixteen sutras. Vedic multiplier makes use of bit-wise multiplication with simultaneous product term finding and it's column-wise addition. It is one of the fine benchmark for fast multiplication algorithm.

Fig4(a): 2\*2 bit Vedic Multiplier Block Diagram

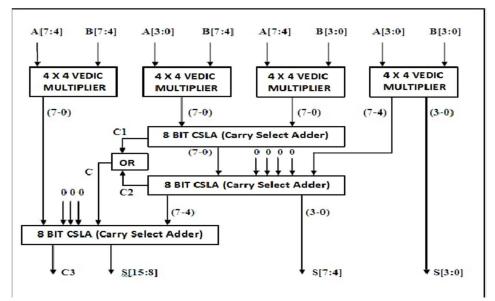

Fig4(b): 4\*4 bit Vedic Multiplier Block Diagram

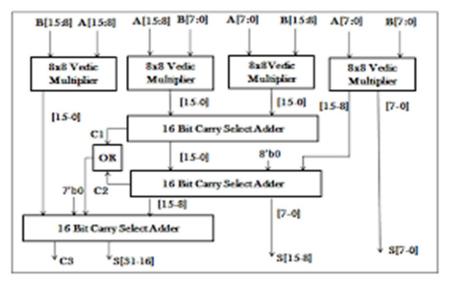

Fig4(c): 8\*8 bit Vedic Multiplier Block Diagram

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue I Jan 2022- Available at www.ijraset.com

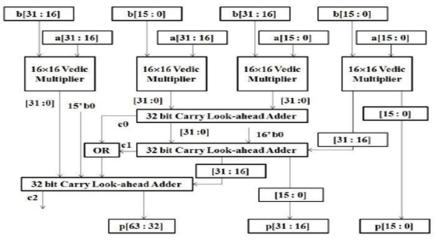

Fig4(d): 16\*16 bit Vedic Multiplier Block Diagram

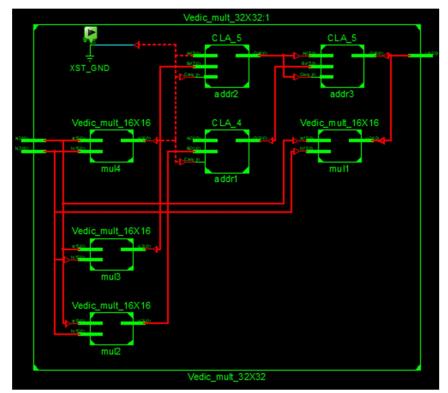

Fig4(e): 32\*32 bit Vedic Multiplier Block Diagram

#### III. SYNTHESIS & SIMULATION

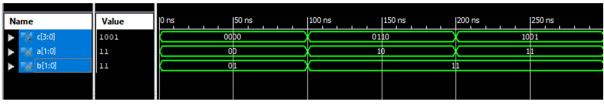

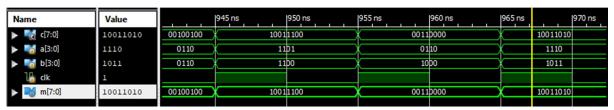

Fig. 5 Simulation Result of 2-bit Vedic Multiplier

Fig. 6 Simulation Result of 4-bit Vedic Multiplier

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 10 Issue I Jan 2022- Available at www.ijraset.com

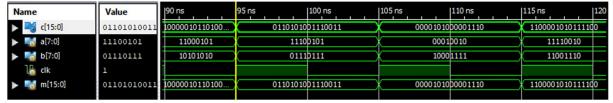

Fig. 7 Simulation Result of 8-bit Vedic Multiplier

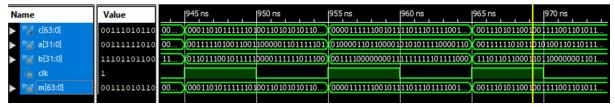

Fig. 8 Simulation Result of 16-bit Vedic Multiplier

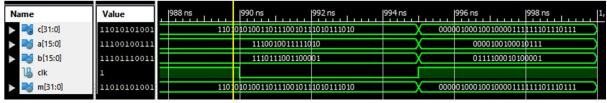

Fig. 9 Simulation Result of 32-bit Vedic Multiplier

#### IV. IMPLEMENTATION

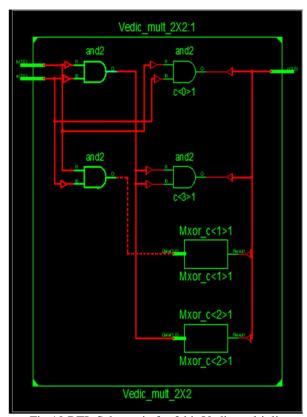

Fig. 10 RTL Schematic for 2 bit Vedic multiplier

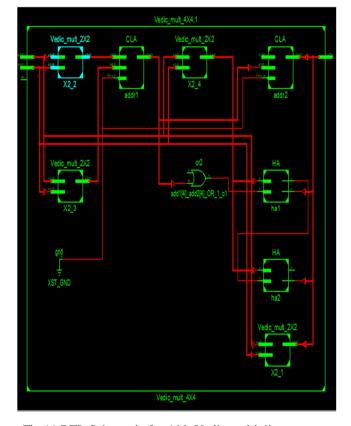

Fig.11 RTL Schematic for 4 bit Vedic multiplie

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue I Jan 2022- Available at www.ijraset.com

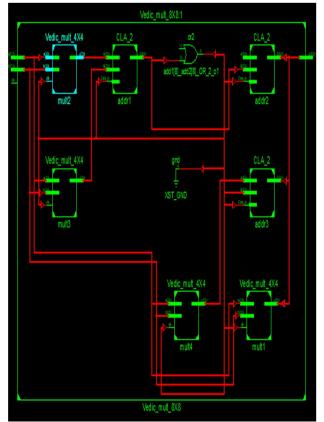

Fig.12RTL Schematic for 8 bit Vedic multiplier

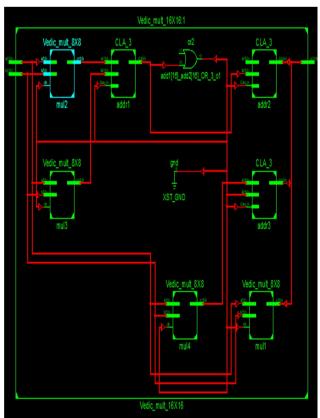

Fig.13 RTL Schematic for 16 bit Vedic multiplier

Fig.14 RTL Schematic for 32 bit Vedic multiplier

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 10 Issue I Jan 2022- Available at www.ijraset.com

| Device-Spartan6<br>XC6SLX45-CSG324 |            |                  |                   |             |

|------------------------------------|------------|------------------|-------------------|-------------|

| Vedic Multiplier                   | Delay (ns) | Levels of Logics | No. of slice LUTs | Memory (KB) |

| 2-Bit                              | 0.948      | 3                | 4                 | 4617500     |

| 4-Bit                              | 3.976      | 8                | 25                | 4617456     |

| 8-Bit                              | 7.965      | 14               | 129               | 4617516     |

| 16-Bit                             | 17.752     | 32               | 603               | 4617444     |

| 32-Bit                             | 44.652     | 88               | 2618              | 4618656     |

Table 1. Using Look Ahead Carry Adder

#### V. CONCLUSION

This paper presents a highly efficient approach of multiplication— "Urdhva Tiryakbhyam Sutra" primarily based on Vedic mathematics. It offers us approach for modular multiplier design and certainly shows the computational advantages provided by means of Vedic methods. The computational route delay for proposed new Vedic multiplier is observed to be much less as contrast to different multiplier. Hence motivation to minimize delay is finely fulfilled. Therefore, the new Vedic multiplier is much more efficient than Array and traditional multiplier in phrases of execution time (speed).

#### REFERENCES

- [1] P. Ram Sirisha, A.M. Prasad, "Design and Performance Analysis of 32 bit Array Multiplier using optimized Carry Select Adder". IEEE JOURNAL ,2015.

- [2] S.Vijayakumar, J.Sundararajan, P.Kumar and S.Rajkumar, "Low power multiplier using vedic carry look ahead adder". International Conference on Engineering and Technology, pp. 1-4, 2015.

- [3] Suganthi Venkatachalam and Seok Burn Ko,"Design of Power and Area Effcient Approximate Multiplier". IEEE Transactions on Very Large Scale Integration Systems, pp. 1-5, 2016.

- [4] Samiksha Dhole, Sayali Shembalkar, Tirupati Yadav and Prasheel Thakre, "Design and FPGA Implementation of 4x4 Vedic Multiplier using Different Architectures".International Journal of Engineering Research & Technology, Vol. 6, pp. 812-816, 2017.

- [5] C. Durgadevi, M. Renugadevi, C. Sathyasree, et al.," Design of High Speed Vedic Multiplier Using Carry Select Adder".International Journal of Engineering Research & Technology, Vol.5, pp. 1-5, 2017.

- [6] K. Nehru and T.T.Linju," Design of 16 Bit Vedic Multiplier Using Semi-Custom and Full Custom Approach". Journal of Engineering Science and Technology Review, pp. 221-232, 2017.

- [7] Divya, K Surya, K Uma Narayani, et al., "Design of 32 Bit Vedic Multiplier using Carry Look Ahead Adder". Global Research and Development Journal for Engineering, pp. 95-99, 2018.

- [8] L Z Shinga,R Hussin, A Kamarudin, S N Mohyar, S Taking, M H A Aziz and N Ahmad, "16X16 Fast Signed Multiplier Using Booth and Vedic Architecture". Electronic and Green Materials International Conference, pp. 020085(1)-020085(8), 2018.

- [9] V.Naresh and G.Kalpana, "Design of 64 bit vedic multiplier using carry look ahead adder". Journal of Emerging Technologies and Innovative Research, Vol.7, pp. 91-95, 2020.

- [10] K. Keshav Sai Chowdary, K. Mourya, S. Ravi Teja, et al., "Design of Efficient 16-bit Vedic Multiplier". International Conference on Signal Processing and Communication, pp. 214-218, 2021.

10.22214/IJRASET

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)