IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: XI Month of publication: November 2017

DOI: http://doi.org/10.22214/ijraset.2017.11060

www.ijraset.com

Call: 🕥 08813907089 🔰 E-mail ID: ijraset@gmail.com

# Design and Implementation of Zynq-Based Reconfigurable System for Jpeg 2000 Compression

M. Anil kumar<sup>1</sup>, Mr. Y. Amar babu<sup>2</sup>, Mr. Rakesh kumar<sup>3</sup>

<sup>1</sup>M.Tech student, ECE dept, LBRCE, Mylavaram, Andhra Pradesh, India <sup>2</sup>Professor,ECE dept, LBRCE, Mylavaram, Andhra Pradesh, India <sup>3</sup>Asst.prof, ECE dept, LBRCE, Mylavaram, Andhra Pradesh, India

ABSTRACT: This paper proposes design and implementation of area efficient Zynq-based self-reconfigurable system to perform jpeg 2000 compression, due to more complexity of jpeg 2000, hardware implementation on reconfigurable hardware fabric is needed. Here, we are proposed an embedded system named as zynq system which utilizes the filter bit streams for image compression. In the zynq there are two major parts processing system and programmable logic. The programmable logic means FPGA. FPGA is the reconfigurable system in which the compression filter bit streams are designed to perform jpeg 2000 compression. Here we used zynq-7010 ARM cortex- A9 series processor system, using Xilinx platform. The partial bit stream of 2-D DWT is created in SDK tool and then the FPGA is programmed for our required image compression. The results of accuracy and hardware components used are calculated.

#### I. INTRODUCTION

To implement the functionality of entire application on a system it requires several physical components, so SoC means system on chip which enables all the physical parts in one chip. The components like digital analogy and mixed signals applications are performed. The SoC is capable of high volume marketing. So, there is a need of flexibility and this gives the system on programmable chip. The So C is of ASIC Application Specific Integrated Circuit based and FPGA based. In ASIC designs must be sent for expensive and time consuming fabrication in semiconductor foundry and designed all the way from behavioural description to physical layout in fpga the design bought off the shelf and reconfigured by designers themselves and no physical layout design in this the design ends with a bit stream used to configure a device. The disadvantage of ASIC is Manufacturing cycle for ASIC is very costly, lengthy and engages lots of manpower. Mistakes not detected at design time have large impact on development time and cost and FPGAs are perfect for rapid prototyping of digital circuits Easy upgrades like in case of software Unique applications reconfigurable computing Here we are selected zynq-7010 FPGA board using Xilinx platform studio, because field programmable gate array have reconfigurable hard ware architecture hence the JPEG2000 image with high speed and reduced size can be obtained low risk and low power consumption The proposed SOC for image compression is evaluated up to1GHz on Xilinx Zynq based ARM cortex- A9 processor

#### II. LITERATURE SURVEY.

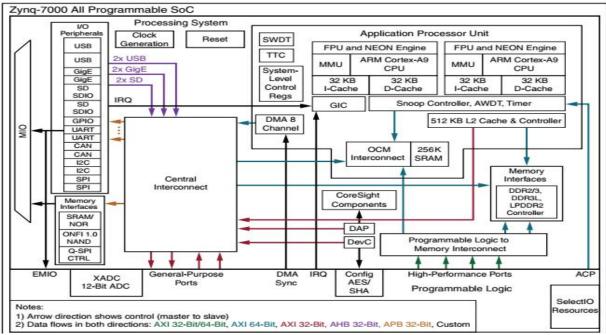

#### A. Zynq platform

As we said earlier it mainly consists of two parts Processing system: PS consists of dual core ARM cortex A9 processor. It is the hard core processor. It consists of caches, DMA controller, and peripherals like USB, SPI, UART etc. Advanced Microcontroller Bus Architecture is used for connection of blocks in system It consists of Application processing unit in which dual core processor and Media processing engine and floating point are there. It has level 1, level 2, and on chip memory of 256 kb. It has snoop control unit which forms a path to level 1 &2 and on chip memory of processing system and it also has memory management unit. Neon Engine can accept SIMD and it is applied to image and video processing which are operate in large no of samples

Fig-1: Architecture of zynq

# B. Programmable logic

PL is fabricated by hybrid FPGA. It consists of soft core processor (Micro blaze). It consists of configurable logic blocks which are built by logic slices, logic slice is a subunit of CLB, contain resources for implementing combinational and sequential logics. Zynq slices consists of 4 look up tables, 8 flip flops

LUT is a flexible resource cable of implementing logic function up to 6 inputs and a small ROM. LUT can combined together to form larger logic functional blocks, memories

In the CLB there is switch matrix which provides routing for connection between elements within CLB and from one CLB to another resource Special resources

PL consists of special like DSP48EI and Block RAMS

DSP48EI is for high speed arithmetic and Block RAM for base memory management

Designing with zynq: In the vivado design suite the zynq is designed for our application

Vivado simulator simulator environment for testing the hardware component within system

Vivado logic analyzer: In system verification of design

C. System analyser

it is used for creating and simulating the DSP designs

D. Vivado HSL

for hardware synthesis from c-level description

E. ZED Board: zynq evaluation board

The board consists of general purpose i/o and 9 LED,8 Switches and 7 push buttons. It has audio codec and video HDMI and VGA port USB cables like OTG, JTAG, UART and sd card.

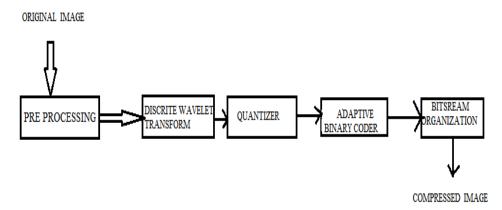

#### III. JPEG2000 COMPRESSION

In the real time the usage of digital images are increasing greater and greater today we are using digital images in many different applications but before 15 years the usage is very rare. Today we are using at medical imaging, digital photography, image archiving, multimedia technology and Internet viewing .in order to transmit or store images requires more memory size so he image size should be reduced. For that compression is needed, the steps involved in the JPEG compression is shown below. *Pre-processing*: In the pre-processing the pixels are partitioned into equal parts that means into equal tiles

#### A. Discrete wavelet transforms

This is the main block for the entire JPEG compression. Where the basic compression is take placeDiscrete Wavelet Transform (DWT) is used to decompose each tile component into different sub-bands. The transform is in the form of dyadic decomposition and use bi-orthogonal wavelets.

#### B. Quantize

It is the baseline block. In which the uniform quantization and inverse quantization. After transformation, all coefficients are quantized using scalar quatization. Quantization reduces coefficients in precision. The operation is lossy unless the quantization step is 1 and the coefficients integers (e.g. reversible integer 5/3 wavelet)

#### C. Adaptive binary encoder

In each sub bands of the binary coding entropy encoded to create the compressed bit-stream.

#### D. JPEG 2000 bit-stream organization:

#### There are some steps involved in this organisation

Canvas coordinate system, Resolution grid, recinct and code block partitioning, Layers and packet , Packet header, Progression order

Fig-2: Block diagram of JPEG2000 compression

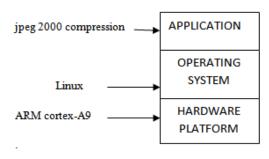

#### IV. ZYNQ SYSTEM FOR JPEG200 COMPRESSION

In this section we discussed about the proposed Hardware and Software platform for JPEG compression. System on chip implementation for jpeg compression involves three layers in it. The three layers are hardware platform followed by operating system (OS) and the required application that is to be carried out. Pictorially it is shown below

Fig-3 Layers of hardware

The above figure shows the layers of the project carried out. In the first layer it is about our application that is image compression and the second layer about operating system. Here we used Linux operating system and the third layer about the hardware design of *A. zynq system processor*

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue XI November 2017- Available at www.ijraset.com

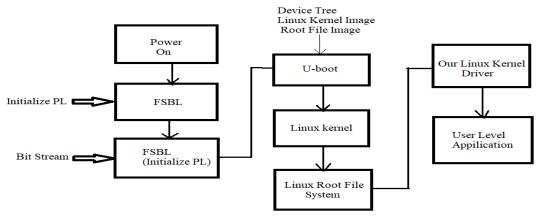

1) Booting Sequence:: When power on the ZED board, a piece of programme is require initialize the memory FSBL is the first stage boot loader is created in SDK and it configures the PS

Fig-4: Booting sequence of zynq system

The hardware design is implemented usingvivado design suite and generate bit stream fileand in the SDK executable (.elf) file is created for our application that means for 2-D DWT iscreated and then boot image created and loadedinto SD card which is connected to zed board. FPGA will be programmed and the required compression of JPEG 2000 is carried out.

| Resources | available | used        |

|-----------|-----------|-------------|

| LUT       | 17600     | 2821( 16 %) |

| SLICE     | 10000     | 5010 (50%)  |

| RAM BOCKS | 80        | 6 (7%)      |

| DSPs      | 80        | 0 (0%)      |

Table: comparison of available and usedresources

#### V. RESULTS

The results of BMP image is shown below in the figure. Which are compressed by zynq fpga system the outputs of JPEG 2000 compressions are obtained

Fig-5:.BMP image-1 (2505KB)

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue XI November 2017- Available at www.ijraset.com

Fig-6: JPEG 2000 compressed image-1 (700 KB)

Fig-7BMP image-2 (2042 KB)

Fig-8 JPEG 2000 compressed image-2 (842 KB)

# **VI.CONCLUSION**

In this paper, we propose partial reconfigurable zynq system to JPEG compression filter. Hardware implementation of filter engine onto the FPGA fabric provides computing capability of jpeg 2000compression.Only a small amount of resources are used in this project

# VII.FUTURE SCOPE

In this project we used only 5% of resources. in future can reduce the noise of the compressed image. so the remaining 95% of resources can be used to another application at a time in the zynq system

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue XI November 2017- Available at www.ijraset.com

#### REFERENCES

- Zynq-Based Reconfigurable System for Real-Time Edge Detection of Noisy Video SequencesIljung Yoon, Heewon Joung, and Jooheung Hongik University, Seoul 04066, Republic of KoreaCorrespondence should be addressed to Jooheung Received 25 December 2015; Accepted 10 July 20

- J. Silva, V. Sklyarov, and I. Skliarova, "Comparison of on-chipCommunications in Zynq-7000 all programmable systems-on chip," IEEE Embedded Systems Letters, vol. 7, no. 1, pp. 31–34,2015.

- [3] ] UG1165 (v2015.3), Zynq-7000 All Programmable SoC: EmbeddedDesign Tutorial, Xilinx, November 2015.

- [4] D. Crookes, K. Benkrid, A. Bouridane, K. Aiotaibi, and A.Benkrid, "Design and implementation of a high level programmingEnvironment for FPGA-based image processing," IEEProceedings: Vision, Image and Signal Processing, vol. 147, no. 4, pp. 377–384, 2000.

- [5] P. Greisen, M. Runo, P. Guillet et al., "Evaluation and FPGAImplementation of sparse linear solvers for video processingbapplications," IEEE Transactions on Circuits and Systems for Video Technology, vol. 23, no. 8, pp. 1402–1407, 2013.

- [6] A. M. Mahmood, H. H. Maras, and E. Elbas, "MeasurementOf edge detection algorithms in clean and noisy environment," InProceedings of the 8th IEEE International Conference on Application of Information and Communication Technologies (AICT '14), pp. 1–6, Astana, Kazakhstan, October 2014.

- [7] Xilinx, Zynq-7000 All Programmable SoC Overview, DS190(v1.8), Xilinx, 2015.

- [8] UG585 (v1.10), Zynq-7000 All Programmable SoC Technical ReferenceManual, Xilinx, February 2015.

- [9] A. Majumdar, S. Cadambi, and S. T. Chakradhar, energy efficientHeterogeneous system for embedded learning andClassification," IEEE Embedded Systems Letters, vol. 3, no. 1, pp.42–45, 2011

- [10] Xilinx, Vivado Design Suite User Guide Partial Reconfiguration, (v2014.4), Xilinx, 2014.

- [11] E. Stott, P. Sedcole, and P. Y. K. Cheung, "Fault tolerant methodsfor reliability in FPGAs," in Proceedings of the

- [12] M. G. Parris, C. A. Sharma, and R. F. Demara, "ProgressIn autonomous fault recovery of Field Programmable GateArrays," ACM Computing Surveys, vol. 43, no. 4, article 31, 2011.[13] M. Liu, W. Kuehn, Z. Lu, and A. Jantsch, "Run—time partial

- [13] Reconfiguration speed investigation and architectural designSpace exploration," in Proceedings of the International Conference Field Programmable Logic and Application, pp. 498–502, Prague, Czech Republic, September 2009.

- [14] R. Bonamy, H.-M. Pham, S. Pillement, and D. Chillet,"UPaRC—Ultra-fast power-aware reconfiguration controller,"InProceedings of the Design, Automation & Test in EuropeConference & Exhibition (DATE '12), pp. 1373–1378, IEEE, Dresden, Germany, March 2012.

- [15] M. H"ubner, D. G"ohringer, J. Noguera, and J. Becker, "FastDynamic and partial reconfiguration data path with low hardwareoverhead on Xilinx FPGAs," in Proceedings of the IEEEInternational Symposium on Parallel & Distributed Processing, pp. 1–8, April 2010.

- [16] K. Vipin and S. A. Fahmy, "Zycap: efficient partial reconfiguration the xilinx zynq," IEEE Embedded SystemsLetters, vol. 6, no. 3, pp. 41–44, 2014.

- [17] XAPP1159(v1.0) and C. Kohn, Partial Reconfiguration of aHardware Accelerator on Zynq-7000 All Programmable SoCDevices, Xilinx, January 2013.

- [18] S. Jin, W. Kim, and J. Jeong, "Fine directional de-interlacingalgorithm using modified Sobel operation," IEEE Transactionson Consumer Electronics, vol. 54, no. 2, pp. 857–862, 2008.

- [19] P.-Y.Chen, C.-Y. Lien, and Y.-M. Lin, "A real-time image denoising Chip," in Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS '08), pp. 3390–3393, Seattle, Wash,

- [20] USA, May 2008.[20] C.Chen, J.Ni, and J.Huang, "Blinddetectionofmedianfilteringin digital images: a difference domain based approach," IEEETransactions on Image Processing, vol. 22, no. 12, pp 4699–4710,2013

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)