IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: XI Month of publication: November 2017 DOI:

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

# High Efficient Sign Detection for Residue Number System

Dr. M. Shyam sundar<sup>1</sup>

<sup>1</sup>Associate professor Kamala Institute of technology & science, karimnagar

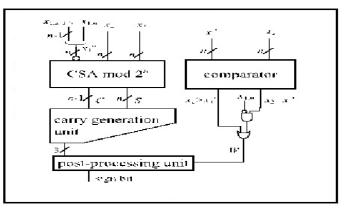

Abstract: The sign recognition problem continues to be investigated by many people scientists. An over-all theorem comes by creating the required conditions for sign recognition. First, an indication recognition formula for that restricted moduli set is described. The sign recognition unit is concurrent and appropriate for VLSI implementation in line with the suggested sign recognition formula. This brief presents a quick sign recognition formula for that residue number system moduli set. The brand new formula enables for parallel implementation and consists solely of modulo 2n additions. Then, an indication recognition unit for that moduli set is suggested in line with the new sign recognition formula. A typical RNS is determined solely for positive integers within the range (, M). To support negative integers, an implicit signed number system might be regarded as split up into an optimistic 1 / 2 of the number along with a negative 1 / 2 of the number. The system could be implemented one carry save adder, one comparator and something prefix adder. The experimental results show the suggested circuit unit offers 63.8%, 44.9%, and 67.6% savings typically in area, delay and power, correspondingly, in comparison having a unit according to among the best sign recognition calculations. For any more realistic comparison, the 3 sign recognition models for those moduli set were implemented using static CMOS VLSI technology.

Keywords: Computer arithmetic, residue number system (RNS), restricted moduli set, sign detection.

## I. INTRODUCTION

In addition, sign recognition within an RNS isn't as efficient as modular procedures, for example addition, subtraction, and multiplication, due to its complexity. A higher-efficiency sign recognition unit for that moduli set is presented. The sign recognition unit is concurrent and appropriate for VLSI implementation in line with the suggested sign recognition formula. Sign recognition plays an important role in branching procedures, magnitude evaluations, and overflow recognition. Since the sign details are hidden in every residue digit inside a residue number system (RNS), sign recognition within an RNS is much more difficult than that within the weighted number system, where the sign is easily the most significant bit (MSB) [1]. The sign recognition problem continues to be investigated by many people scientists. An over-all theorem comes by creating the required conditions for sign recognition. The sign recognition for any selected type of RNS is transported out like a sum modulo 2 of numbers within the connected mixed radix system (MRS). Inside sign recognition technique according to fractional representation is suggested to lessen the sum modulo M within the conversion formula to some sum modulo 2. Inside sign recognition formula in line with the new Chinese remainder theorem (CRT) II is presented. The modulo procedures within the sign recognition formula are bounded by size vM. Inside sign recognition formula uses the nth mixed radix digit in mixed-radix conversion (MRC) to identify the sign function. Up to now, may be the only brief to make use of the combinational logic to apply an indication recognition formula according to. However, the technique can't be extended with other moduli sets. The moduli set, only including the kinds of 2n and 2n-1, continues to be researched extensively recently due to its efficiency for modulo procedures and reverse conversion. Within this brief, an indication recognition formula is presented for that moduli set. The dynamic power is as stated by the synopsis power compiler, which models the switching activity using static probability and toggle rate. The experimental results indicate the suggested sign recognition unit offers significant savings in delay, area and power in comparison using the sign recognition models. First, an indication recognition formula is presented for that restricted moduli set including modulo 2n within the RNS. The suggested sign recognition formula requires only adding the modulo2n. Then, a brand new sign recognition unit is produced for the moduli set in line with the suggested sign recognition formula. The Kodak play touch camcorder only includes a carry save adder (CSA), a comparator, along with a carry generation unit. The suggested formula may be the first suggested for that moduli set [2]. The accomplished efficiency is preferable to those of other techniques, for example calculations according to ROM technology and specialized calculations based. This brief is organized the following. The suggested sign recognition formula for that restricted moduli set. Is definitely the sign recognition unit for that moduli set. The particulars the implementation from the suggested unit with evaluations of area, time, and power after which is definitely the comparison results.

# International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue XI November 2017- Available at www.ijraset.com

Fig.1.Sign detection unit

## **II. METHODOLOGY**

The sign recognition problem continues to be investigated by many people scientists. An over-all theorem comes by creating the required conditions for sign recognition [3]. A typical RNS is determined solely for positive integers within the range (, M). To support negative integers, an implicit signed number system might be regarded as split up into an optimistic 1 / 2 of the number along with a negative 1 / 2 of the number. The dynamic range M from the moduli set is even. After conversion in the residue number towards the weighted number, the resulting no integer X within the interval (, M/2) carries an implicit representation from the sign of the particular result Y, which may be acquired in the range [-M/2, M/2 - 1) Theorem 1 offers the mixed radix type of the CRT that converts residue figures to weighted figures it takes modulo mi procedures only. The calculation process for every mixed radix at in Theorem 1 is in addition to the others, and therefore, the mixed radix coefficients could be calculated inside a fully parallel manner. With Theorem 1, we are able to deduce Theorem 2 Theorem 3 offers an efficient sign recognition formula for moduli set since it consists solely of modulo 2n addition and also the residue numbers could be calculated inside a fully parallel manner.

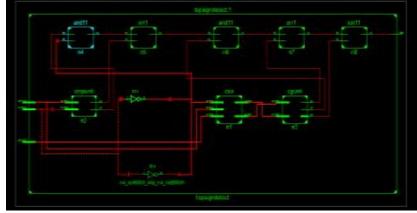

Fig2: RTL Schematic

A higher-efficiency sign recognition unit for that moduli set is presented. The sign recognition unit is concurrent and appropriate for VLSI implementation in line with the suggested sign recognition formula. The performance from the suggested sign recognition unit from the moduli set is evaluated. The sign recognition unit is in comparison with two models extended by two best sign recognition calculations to show our prime efficiency from the new sign recognition formula. The region and delay from the suggested unit are believed while using standard unit-gate model Based on the sign recognition formula, sign recognition could be acquired by knowing the nth little bit of the 3rd mixed-radix digit a3 from the residue representation. For any more realistic comparison, the 3 sign recognition models for those moduli set were implemented using static CMOS VLSI technology [4]. Initially, we used the Verilog language to create hardware models for that suggested unit and also the sign recognition models based, for that moduli set , n = 4, 8, 12, 16, 20, 24, 28, 32. Each design was synthesized utilizing a synopsis design compiler having a SMIC CMOS standard cell library (.18 µm, 1.98 V, °C). Two optimization options were examined during synthesis. First, each design was restricted to

# International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue XI November 2017- Available at <u>www.ijraset.com</u>

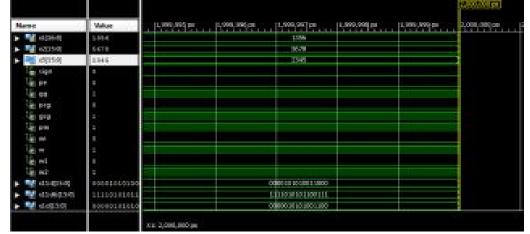

attain the absolute minimum area design. Second, more and more stringent timing constraints were put on each design before the verge of timing closure. Design constraints, for example output load and maximum fan out, were held constant for every design. The dynamic power is as stated by the synopsis power compiler, which models the switching activity using static probability and toggle rate. The experimental results indicate the suggested sign recognition unit offers significant savings in delay, area and power in comparison using the sign recognition models. The enhancements are reasonable. The brand new sign recognition formula are designed for the residue numbers inside a fully parallel manner, whereas the sign recognition calculations. Additionally, our new formula consists solely of modulo 2n addition with no other modulo operation.

Fig3: output waveform

## **III. CONCLUSION**

The sign recognition unit is concurrent and appropriate for VLSI implementation in line with the suggested sign recognition formula. Within this brief, a quick sign recognition formula is presented for restricted moduli set such as the modulo2n. A higherefficiency sign recognition unit for that moduli set is presented. The sign recognition unit is concurrent and appropriate for VLSI implementation in line with the suggested sign recognition formula. The suggested formula enables for parallel implementation and consists solely of modulo 2n additions. The sign recognition problem continues to be investigated by many people scientists. An over-all theorem comes by creating the required conditions for sign recognition. An indication recognition unit for those moduli set is suggested in line with the suggested sign recognition formula. The experimental results show the suggested circuit accomplishes significant enhancements when it comes to area, delay, and power.

#### REFERENCES

- [1] M. Akkal and P. Siy, "Optimum RNS sign detection algorithm using MRC-II with special moduli set," J. Syst. Arch., vol. 54, no. 10, pp. 911–918, Oct. 2008

- [2] R. Zimmermann, "Efficient VLSI implementation of modulo (2n ± 1) addition and multiplication, in Proc. 14th IEEE Symp. Comput. Arithmetic, 1999, pp. 158–167

- [3] P. Mohan, "RNS-to-binary converter for a new three-moduli set {2n+1 1, 2n, 2n 1}," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 54, no. 9, pp. 775–779, Sep. 2007

- [4] Z. Ulman, "Sign detection and implicit-explicit conversion of numbers in residue arithmetic," IEEE Trans. Comput., vol. 32, no. 6, pp. 590–594, Jun. 1983.

- [5] Minghe xu et all "Fast sign detection algoritm for RNS Moduli Set" IEEE Transactions vol.23, issue 2 ,Feb 2015.\

- [6] J.Raghu and B.Ashok "A Scheme for Flag Identification in a Restricted Set Expression" IJSR volume 5, issue 9,sep 2016.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)