# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 6 Issue: III Month of publication: March 2018

DOI: http://doi.org/10.22214/ijraset.2018.3583

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue III, March 2018- Available at www.ijraset.com

### Analysis Of Novel Comparator Design Using Quantum Dot Cellular Automata (QCA).

Abhisekh Banerjee<sup>1</sup>, Dipak Kumar Mahato<sup>2</sup>, Ratna Chakraborty<sup>3</sup>

<sup>1, 2</sup>Mtech student in Microelectronics and VLSI Department of Electronics and Communication

<sup>3</sup>Professor, Department of Electronics and Communication Institute of Engineering & Management Kolkata-700091, India

Abstract: Quantum Dot Cellular Automata is one of the new approach of nanotechnology that uses quantum dots to design various digital circuits as alternate of conventional transistor based CMOS technology. A QCA is projected as a emerging field in the area of nanotechnology for future IC's in near future .Quantum Dot Cellular Automata has incorporated both the features of quantum mechanics and cellular automata .This paper has demonstrated the design of novel comparator used in A/D converter with help of majority gate based on Quantum Dot Cellular Automata. The calculation of kink energy has determined the robustness of the circuit. The simulation results have been captured and verified using the CAD tool QCA Designer. Keywords: QCA, quantum dot, majority gate, QCA designer etc.

### I. INTRODUCTION

Due to the rapid development of technology, the conventional CMOS technology faces major physical limits of the technology like excessive power dissipation, short channel effects, tunnelling currents etc in the nano domain. Quantum Dot Cellular Automata is a new approach in the area of nanotechnology that uses quantum dots—to design various digital circuits to overcome the physical limitations of the conventional transistor based CMOS technology. A QCA is an array of structures known as quantum dots.[1] Dots are quantum particles confined in three dimensions. QCA—technology encodes information by changing the charge configuration instead of transferring information through current and voltage. The advantages of QCA technology include high device density, small circuit size, low power consumption etc[1][2][3].

### II. QCA PRELEMINARIES

### A. QCA Cell

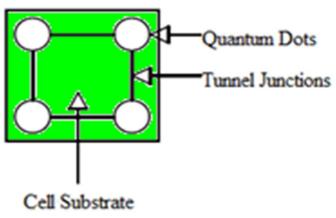

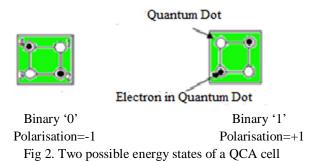

The fundamental unit of QCA is a cell. A cell looks like a square. Each cell contains four quantum dots at the four corners of a square shaped cell. The two mobile electrons can occupy any of the two quantum dots. The two electrons can quantum mechanically tunnel between the dots but cannot come out from the cell.[2]-[4] Dots are the places where electrons can sit. If a cell is charged with two excess electrons each free to tunnel to any site in the cell, these electrons will try to occupy the furthest possible site with respect to each other due to mutual columbic repulsion. Therefore, two different cell states exist. A cell state is called its polarisation. The polarisation P=+1 is used to represent logic '1' and polarisation P=-'1' is used to represent to logic '0'.[1]-[8][11]. The following fig 1 and fig 2 shows the structure of a QCA cell and two possible minimum energy states of a QCA cell respectively.

Fig 1. Structure of a QCA cell

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue III, March 2018- Available at www.ijraset.com

The polarisation P is defined by [1][2]-

$$P = \frac{(p_1 + p_3) - (p_2 + p_4)}{p_1 + p_2 + p_3 + p_4}$$

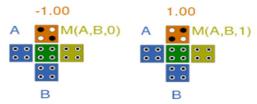

### B. Majority Gate

A majority gate is composed of five QCA cells. One of the five cells is set as a fixed polarisation and the other two act as two inputs and the remaining one serves as a driver cell. By changing the value of polarisation we can built an AND gate or OR gate. The generalised expression of majority gate is -

$$M(A, B, C) = AB + BC + CA$$

By assigning the value of C as 0, we can easily construct an AND gate

$$M(A, B, 0) = AB$$

By assigning the value of C as 1, we can easily construct an OR gate.

$$M(A, B, 1) = A+B$$

The following fig 3 shows the generalised structure of a 2 input AND & OR gate.

Fig3.Structure of 2 input AND & OR gate.

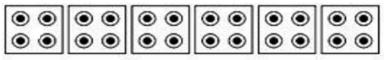

### C. OCA Wire

An array of QCA cells is called a QCA wire. In order to transmit the information from one point to another a QCA wire is used. In QCA wire the way of transfer of information from source end to destination occurs by electrostatic repulsion. The propagation in 90° and 45° QCA wire is shown in following fig 4 and fig 5.

Fig 4. 90° QCA wire

Fig 5. 45° QCA wire

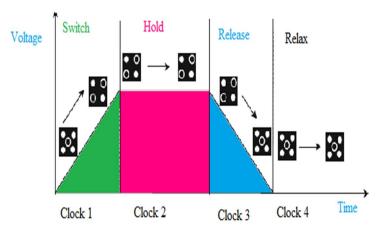

### D. QCA Clocking

The QCA circuit require clocking not only to control flow of information and synchronisation but actually provides power to run the circuit as there is no external power to drive the cells.[5] Clock is used to push the information from on cell to another. The

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue III, March 2018- Available at www.ijraset.com

adjustment of tunnelling barriers between quantum dots for transfer of electrons between dots occurs by the application of proper clocking. There are mainly four types of clocking namely, switch, hold, release and relax shown in fig 6.

Fig 6. Four stages of Clocking

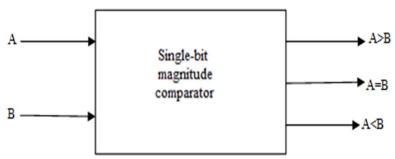

### III. PRESENTATION OF COMPARATOR

A magnitude comparator is a combinational circuit that compares the magnitude of two numbers (A and B) and generates one of the following outputs: A=B, A<B and A>B. The block diagram of a single-bit comparator is shown in fig 7.

Fig 7. Block diagram of comparator

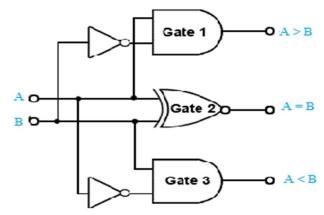

To implement the magnitude comparator, the EX-NOR gates and AND gates are used. The property of the EX-NOR gate can be used to find whether the two binary digits are equal or not, and the AND gates are used to find whether a binary digit is less than or greater than another bit. The following diagram shows two AND gates, one with A and B as inputs and another with A and B as their inputs. The first AND gate 1 output is 1 if A > B (i.e. A=1 and B=0) and 0 if A < B (i.e. A=0 and B=1). Similarly, the second AND gate 2 output is 1 if A < B (i.e. A=0 and B=1) and 0 if (i.e. A=1 and B=0)[14][15].

Fig 8. Logic diagram of comparator

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue III, March 2018- Available at www.ijraset.com

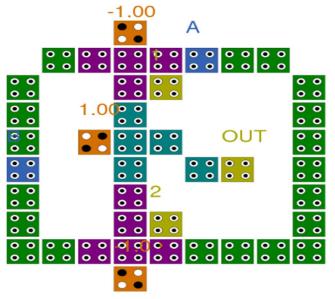

Fig 9. Layout of a comparator.

### IV. SIMULATION RESULTS

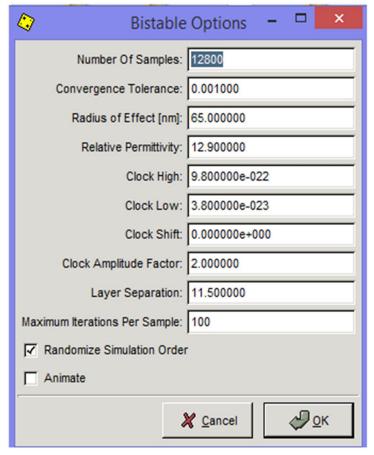

An optimized design of 1- bit comparator has been presented here. The comparator is built with 42 cells having a approximate area of 0.04 um<sup>2</sup>. The proposed circuit has been simulated using the CAD tool QCA Designer[16] with version 2.0.3. The default parameters have been considered for the bistable approximation shown in fig 10 below:-

Fig 10. Default parameters for bistable approximation

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue III, March 2018- Available at www.ijraset.com

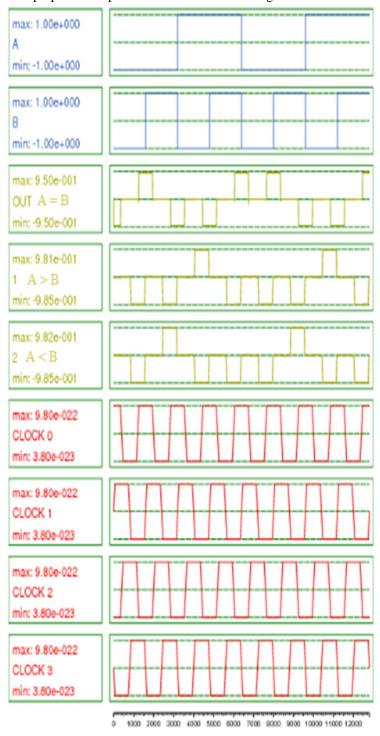

Comparator is a combinational circuit that determines whether the two inputs are greater, equal or less than each other. The simulation results have been verified and captured for the three conditions of a comparator when A = B, A > B, A < B taking A and B as inputs. The logic function of the comparator[13]-[15]-

$$\begin{aligned} F_{A>B} &= A.\overline{B} \\ F_{A=B} &= \overline{A}\overline{B} + \overline{A}B \\ F_{A$$

The input-output waveforms for the proposed comparator have been shown in figure 11 below:-

Fig 11. Simulation results of 1 -bit comparator

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue III, March 2018- Available at www.ijraset.com

### V. COMPLEXITY OF PROPOSED COMPARATOR

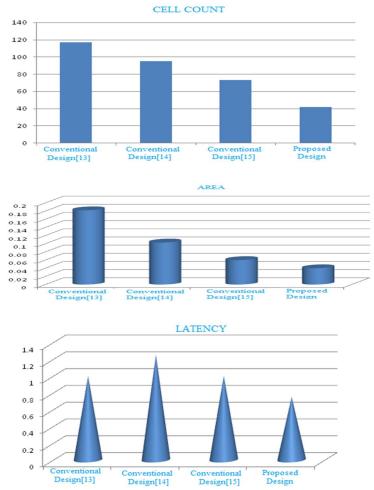

The proposed comparator has been built with 42 cells with area of about 0.04 um<sup>2</sup> and is compared with the previous designs described in table 1.

|                         | CELL COUNT | AREA(um <sup>2</sup> ) | LATENCY |

|-------------------------|------------|------------------------|---------|

| Conventional Design[13] | 117        | 0.182                  | 1       |

| Conventional Design[14] | 95         | 0.103                  | 1.25    |

| Conventional Design[15] | 73         | 0.06                   | 1       |

| Proposed Design         | 42         | 0.04                   | 0.75    |

Table 1. Comparisons in terms of cell count, area, latency

Fig 11. Graphically observation in terms of cell count, area &latency of proposed design with previous design described in [13],[14],[15].

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue III, March 2018- Available at www.ijraset.com

### VI. CALCULATION OF KINK ENERGY

The energy difference between two neighbouring or adjacent cells is known as kink energy. Kink energy depends on the spacing between two neighbouring cells but does not depend on the temperature. We have calculated the kink energy using the formula[12]-

$$U=K\frac{Q_1 \times Q_2}{r}$$

Where, U is the kink energy, K is a constant given by  $K=1/4\pi\epsilon_0\epsilon_r=9 \times 10^9$  and  $Q_1 \& Q_2$  are the electronic charges and r is the distance between them and r is the distance between them.

$$U = \frac{23.04 \times 10^{-29}}{r} J$$

We have assumed that all the cells are identical and square shaped with length of each side equal to 18 nm. Interspacing distance between the cells is 2 nm.

The kink energy of the output cells has been determined below when the condition of the logic function is A=B. Similarly the kink energy of the other two conditions i.e. A>B & A<B can be found out.

Fig 13: Output cells for calculation of kink energy

| Calculation of kink energy for electron 'x'                                                            | Calculation of kink energy for electron 'y'                                                            |  |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| $U_{1=}(23.04 \text{ X } 10^{-29}) / (20 \text{ X } 10^{-9}) = 1.152 \text{ X } 10^{-20} \text{ J}$    | $U_{1=}(23.04 \text{ X } 10^{-29}) / (26.90 \text{ X } 10^{-9}) = 0.856 \text{ X } 10^{-20} \text{ J}$ |  |

| $U_{2=}(23.04 \text{ X } 10^{-29}) / (42.04 \text{ X } 10^{-9}) = 0.548 \text{ X } 10^{-20} \text{ J}$ | $U_{2=}(23.04 \times 10^{-29}) / (38 \times 10^{-9}) = 0.606 \times 10^{-20} \text{ J}$                |  |

| $U_{3=}(23.04 \text{ X } 10^{-29}) / (61.35 \text{ X } 10^{-9}) = 0.375 \text{ X } 10^{-20} \text{ J}$ | $U_{3=}(23.04 \text{ X } 10^{-29}) / (69.33 \text{ X } 10^{-9}) = 0.332 \text{ X } 10^{-20} \text{ J}$ |  |

| U <sub>4=</sub> (23.04 X 10 <sup>-29</sup> ) /(40.04 X 10 <sup>-9</sup> )=0.575 X 10 <sup>-20</sup> J  | U <sub>4=</sub> (23.04 X 10 <sup>-29</sup> ) /(42.94 X 10 <sup>-9</sup> )=0.536 X 10 <sup>-20</sup> J  |  |

| U <sub>Total</sub> =2.65 x 10 <sup>-20</sup> J                                                         | U <sub>Total=</sub> 2.33 x 10 <sup>-20</sup> J                                                         |  |

Table 2. Calculation of kink energy

### VII. CONCLUSIONS

In this paper, we have designed our proposed comparator design using Quantum Dot Cellular Automata. The QCA circuit design provides a new functional platform for information transmission. In addition, QCA binary logic function and the associated new nanotechnology will provide high speed computing, high density application in comparisons to traditional transistor based CMOS technology. The proposed comparator is superior to previous designs in terms of cell count, area ,and latency. The simulation results have been captured and verified using the QCA Designer tool

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue III, March 2018- Available at www.ijraset.com

### REFERENCES

- [1] Lent, Craig S., and P. Douglas Tougaw. "Lines of interacting quantum- dot cells: A binary wire", Journal of applied Physics 74, no. 10:6227-6233,1993.

- [2] P. D. Tougaw, C. S. Lent, "Logical devices implemented using quantum cellular automata". Journal of Applied Physics 75(3):1818–1825, Year 1994.

- [3] C. S. Lent and P. D. Tougaw. A device architecture for computing with quantum dots. Proc. IEEE, 85(4):541-557, April 1997.

- [4] A. O. Orlov, et al., "Experimental demonstration of clocked single electron switching in quantum-dot cellular automata," Applied Physics Letters, vol. 77, pp. 295-297, 2000

- [5] Craig S. Lent and Beth Isaksen, "Clocked molecular quantum-dot cellular automata", IEEE Transaction on Electron Devices 50(9), 1890-1896, 2003

- [6] W. Wang, K. Walus, and G. A. Jullien, "Quantum-dot cellular automata adders," In Proc. Third IEEE Conf. Nanotechnology, pp. 461-464, 2003

- [7] K Walus, T. J. Dysart, G.A. Jullien and R. A. Budiman, "QCADesigner: a rapid design and Simulation tool for quantum-dot cellular automata", IEEE Transaction on Nanotechnology, 3, 26-31, 2004

- [8] V. Vankamamidi, M. Ottavi, and F. Lombardi, "A line-based parallel memory for qca implementation," IEEE Trans. Nanotechnology, vol. 4(6),pp. 690-698, November 2005.

- [9] T. Mohammad, "A New Architecture for T Flip Flop using Quantum Dot Cellular Automata", IEEE, 2011

- [10] MostafaRahimi, A, Kavehei, O, Navi, K: A novel design for quantum-dot cellular automata cells and full adders. J Appl Sci 7, 3460–3648 (2012).

- [11] Heumpil Cho, Earl E. Swartzlander, "Adder and Multiplier Design in Quantum Dot Cellular Automata", IEEE Transaction on Computers, 58, 721-727, 2009.

- [12] Razieh Farazkish, "A new quantum-dot cellular automata fault-tolerant full-adder", Journal of Computational Electronics, Springer-Verlag, DOI 10.1007/s10825-015-0668-

- [13] M. Abdullah-Al-Shafi, A.N. Bahar, Optimized design and performance analysis of novecomparator and full adder in nanoscale, Cogent Engineering. 3 (2016). doi:10.1080/23311916.2016.1237864.

- [14] Y.-S. Xia, K.-M. Qiu, Comparator Design Based on Quantum-Dot Cellular Automata, Journal of Electronics & Information Technology. 31 (2009) 1517–1520.

- [15] Bahniman Ghosh, Shoubhik Gupta, Smriti Kumari, Quantum Dot Cellular Automata Magnitude Comparators, 2012 ,IEEE International Conference of Electron Devices and Solid-State Circuits, 2012 73 cells

- [16] http://www.mina.ubc.ca/qcadesigner.

10.22214/IJRASET

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)