# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 6 Issue: III Month of publication: March 2018

DOI: http://doi.org/10.22214/ijraset.2018.3163

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue III, March 2018- Available at www.ijraset.com

### Single Ended 8T Subthreshold SRAM Cell for Dynamic Feedback Control Signal

Sonal Verma<sup>1</sup>, Ravi Tiwari<sup>2</sup>

<sup>1, 2,</sup> Department of Electronics and Telecomunication, SSGI Bhilai, CSVTU

Abstract: Aggressively scaling the supply voltage of SRAMs greatly minimizes their active and leakage power, a dominating portion of the whole power in modern ICs. Hence, energy constrained applications, wherever performance needs are secondary, benefit considerably from an SRAM that provides read and write functionality at the lowest possible voltage. However, bit-cells and architectures achieving very high density conventionally fail to operate at low voltages. This paper describes a high density SRAM in sixty five nm CMOS that uses associate degree 8T bit-cell to attain a minimum operational voltage of 350 mV. Buffered scan is employed to make sure read stability, and peripheral management of each the bit-cell offer voltage and also the read-buffer's foot voltage modify sub- write and read while not degrading the bitcell's density. The plaguing area-offset exchange in fashionable sense-amplifiers is alleviated using redundancy, that reduces scan errors by an element of 5 compared to device up-sizing. At its lowest operational voltage, the complete a pair of 56 K SRAM consumes 2.2 W in leakage power. Keywords: Cache memories, CMOS memory circuits, leakage currents, low-power electronics, redundancy, SRAM chips

#### I. INTRODUCTION

The convenient microchip controlled gadgets contain inserted memory, that speaks to a substantial a part of the framework on chip (SoC). These convenient frameworks need ultralow power disbursal circuits to use battery for additional term.

The force utilization may be reduced utilizing nonconventional contraption structures, new circuit topologies, and advancing the engineering. In spite of the very fact that, voltage scaling has prompted circuit operation in sub limit administration with least power utilization, but there's a disadvantage of exponential drop-off in execution [1].

The circuit operation within the sub threshold administration has cleared method toward ultralow power inserted recollections, essentially static RAMs (SRAMs) [1], [2]. Be that because it could, in sub threshold administration, the data steadiness of SRAM cell could be a serious issue and declines with the scaling of MOSFET to sub nanometre Technology. as a result of these impediments it gets to be onerous to figure the normal 6-transistor (6T) cell at ultralow voltage (ULV) power provide [1]–[6].

What's additional, 6T has AN extreme issue of scan irritate. The essential and a undefeated approach to lose this issue is that the decoupling of real golf stroke away hub from the bit lines amid the scan operation in [2].

This scan decoupling methodology is employed by standard 8-transistor [read decoupled 8- electronic transistor (RD-8T)] cell that offers scan static commotion edge (RSNM) equivalent with hold static clamor edge (HSNM) [2]–[4]. Be that because it could, RD8T experiences spillage given in scan method.

This spillage current increments with the scaling consequently, increasing the probability of fizzled read/compose operations. Comparative cells that sustain the cell current while not exacerbating the capability hub square measure to boot projected in [4]–[7].

#### II. PROPOSED 8T SRAM CELL DESIGN

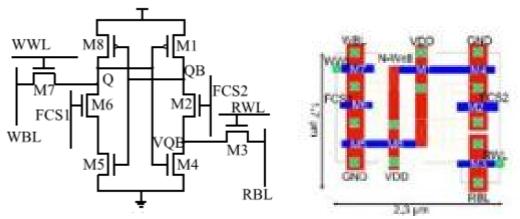

To form cell stable altogether operations, single-finished with component criticism management (SE-DFC) cell is displayed in Fig. 1(a). The single-finished configuration is employed to decrease the differential exchanging power amid read—write operation.

The force gone amid exchanging/flipping of data on single piece line is lesser than that on differential bit-line combine.

The SE-DFC empowers composing through single nMOS in 8T. It likewise isolates the scan and composes method and displays scan decoupling. The fundamental modification of cell is taken into account to upgrade the protection against the process–voltage–temperature (PVT) varieties.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue III, March 2018- Available at www.ijraset.com

Fig. 1. Proposed 8T. (a) Schematic. (b) Layout.

It enhances the static clamor edge (SNM) of 8T cell in sub threshold/close edge space. The projected 8T has one cross-coupled inverter pair, within which each inverter is comprised of 3 fell transistors. These 2 stacked cross-coupled inverters: M1–M2–M4 and M8–M6–M5 hold the information amid hold mode. The compose word line (WWL) controls one and solely nMOS transistor M7, used to exchange the knowledge from single compose bit line (WBL). a distinct read bit line (RBL) is employed to exchange the knowledge from cell to the yield once perused word line (RWL) is initiated. 2 segments one-sided criticism management signals: FCS1 and FCS2 lines are utilised to regulate the input cutting transistors: M6 and M2, separately

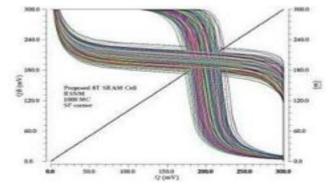

Fig. 2. Butterfly curve of HSNM for 8T

#### A. Cell Layout

For examination of region, format of 5T, 6T, RD-8T, and projected 8T area unit attracted UMC 90-nm CMOS innovation, as appeared in Table I. The sizes of MOSFETs utilised as a section of projected 8T cell are painted in Fig. 1(b). The RD-8T involves one.3× vary as contrasted which of 6T. as a result of the configuration limitations and speak to region between money supply, M3, M4, and M8 for projected 8T, there area unit two × zones overhead as contrasted and 6T cell. Despite the actual fact that it's  $2\times$  territory of 6T, but its higher implicit procedure resistance and component voltage pertinence empowers it to be utilised like cells with one.8 ×  $-2\times$  zone overhead [3]–[7].

#### Write Operation

The criticism slicing set up is used to compose into 8T. during this set up, amid compose one operation FCS1 is formed low that switches OFF M6. At the purpose once the RWL is formed low and FCS2 high, money supply conducts associating Complementary Q (QB) to the bottom. Presently, if the knowledge connected to word bit line (WBL) is one and WWL is motivated (Table II), then current streams from WBL to Q and makes a voltage trek on Q by suggests that of M7-composing one into the cell. More-over, once Q changes its state from zero to one, the inverter (M1–M2–M4) changes the state of QB from one to zero. To compose a 0at Q, WWL is formed high, FCS2 low and WBL is force to the bottom. The low goingFCS2 leaves QB sailplaning which might move to very little negative quality and later on the present from draw up pMOS M1 charges QB to one.

#### Read Operation

The read operation is performed by precharging the RBL and enacting RWL. On the off probability that one is place away at hub Q then, M4 activates and makes a low resistive way for the stream of cell current through RBL to ground. This releases RBL speedily

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue III, March 2018- Available at www.ijraset.com

to ground, which might be detected by the complete swing inverter sense modifier. Since WWL, FCS1, and FCS2 were created low amid the read operation (Table II), thusly, there's no immediate aggravation on real putting away hub QB amid perusal the cell. The low going FCS2 leaves QB sailing, which fits to a negative esteem then returns to its distinctive zero esteem once effective read operation, within the event that Q is high then, the scale proportion of money supply and M4 can superintend the browse current and also the voltage distinction on RBL. Amid read 0 operations, Q is zero and RBL holds energized high esteem and also the inverter sense foil offers zero at yield. Since M2 is OFF thus virtual QB (VQB) is confined from QB and this keeps the shot of aggravation in QB hub voltage that eventually lessens the read disappointment likelihood and enhances the RSNM.

#### III. COMPARISON SUMMARY

The WSNM of proposed 8T is that the most elevated among each alternative cell beneath thought (5T, 6T, RD-8T, and A-8T [11]). RSNM is analogous therewith of RD-8T, whereas the HSNM is somewhat increased contrasted and alternative (5T, 6T, and RD-8T) cells. The projected 8T cell has lower delay as contrasted and single-finished A-8T [11] amid compose operation and nearly same postponement as single-finished RD-8T amid browse operation. The force utilization amid browse operation of projected 8T is zero.49×, 0.48×, and 0.64× as contrasted which of 5T, 6T, and RD-8T, separately, at 300 mV. It may be watched that, the projected cell has higher force economical ability amid read/compose operations, over alternate cells beneath thought. Like projected 8T, 9T cell [16] likewise uses input cutting and dynamic browse decoupling. 9T has 23-mV RSNM ( Pfail= 1e-9) and since of differential compose operation with input cutting, it offers write trip purpose of a hundred and sixty mV. The projected 8T cell is likewise contrasted and 10T cells [6], [7] found within the writing and arranged in Table VI. It deserves seeing that; μ of WSNM of projected 8T is that the most astounding, whereas RSNM and HSNM area unit close to those of 10T cells

#### IV. CONCLUSION

A 8T SRAM cell with high data security (high  $\mu$  and low  $\sigma$ ) that works in ULV provides is exhibited. We tend to achieved improved SNM in sub threshold administration utilizing SE-DFC and browse decoupling plans. The projected cell's zone is doubly as that of 6T. Still, it's higher implicit procedure resistance and component voltage connectedness empowers it to be utilised like cells (8T, 9T, and 10T) on with  $1.8 \times -2 \times$  zone overhead. The projected 8T cell has high solidness and might be worked at ULV of 200–300 mV power provides. The face of lessened force utilization of the projected 8T cell empowers it to be utilised for battery worked SoC set up. Future and utilizations of the projected 8T cell will probably be in low/ULV and medium return operation like neural sign processor, sub threshold processor, wide-working extent IA-32 processor, fast Fourier modification center, and low voltage reserve operation.

#### V. STIMULATION RESULTS

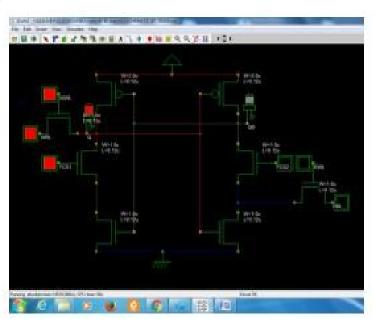

#### A. Proposed System Schematic

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue III, March 2018- Available at www.ijraset.com

#### B. Layout Design

#### C. Output Waveform And Power

#### **REFERENCES**

- [1] K. Roy and S. Prasad, Low-Power CMOS VLSI Circuit Design, 1st ed. New York, NY, USA: Wiley, 2000.

- [2] N. Verma and A. P. Chandrakasan, "A 256 kb 65 nm 8T subthreshold SRAM employing sense-amplifier redundancy," IEEE J. Solid-StateCircuits, vol. 43, no. 1, pp. 141–149, Jan. 2008.

- [3] C. Kushwah and S. K. Vishvakarma, "Ultra-low power sub-threshold SRAM cell design to improve read static noise margin," in Progress in VLSI Design and Test (Lecture Notes in Computer Science), vol. 7373.Berlin, Germany: Springer-Verlag, 2012, pp. 139–146.

- [4] B. H. Calhoun and A. P. Chandrakasan, "A 256-kb 65-nm sub-threshold SRAM design for ultra-lowvoltage operation," IEEE J. Solid-StateCircuits, vol. 42, no. 3, pp. 680–688, Mar. 2007.

- [5] C. B. Kushwah, D. Dwivedi, and N. Sathisha, "8T based SRAM cell and related method," U.S. Patent IN920 130 218 US1, May 30, 2013.

- [6] P. Kulkarni, K. Kim, and K. Roy, "A 160 mV robust Schmitt trigger based subthreshold SRAM," IEEE J. Solid-State Circuits, vol. 42, no. 10,pp. 2303–2313, Oct. 2007

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)