# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 6 Issue: V Month of publication: May 2018

DOI: http://doi.org/10.22214/ijraset.2018.5299

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue V, May 2018- Available at www.ijraset.com

### Design of 2-Bit ALU using CMOS & GDI Logic Architectures.

Sachin R<sup>1</sup>, Sachin R M<sup>2</sup>, Sanjay S Nayak<sup>3</sup>, Rajiv Gopal<sup>4</sup>

<sup>1, 2, 3</sup>UG Students, Dept. of ECE New Horizon College of Engineering, Bengaluru

<sup>4</sup>Asst. Professor, Dept. of ECE New Horizon College of Engineering, Bengaluru

Abstract: Nowadays technology plays an important role, where sizing of the device is a challenge. Various techniques are adopted to design the chip which consumes lesser area and lesser power. Fast processors are replacing the old, as a result of various new methodologies being adopted. In this paper, we use a technique called Gate Diffusion Input (GDI) whichhelps in reducing the number of transistors required to build a design. Here, we compare the designs of 2-bit ALU using standard CMOS and GDI logic. By using Tanner EDA, we were able to conclude that GDI has an upper hand over CMOS in terms of power consumption, delay and area.

Index Terms: Area, ALU, CMOS, GDI, Tanner EDA, power consumption.

### I. INTRODUCTION

Recently, the various industries are insisting for low power, less area and high speed for designing the various analog and digital circuits. With improvement in technology and the enhancement of embedded system used electronic devices such as mobile, desktops, television applications, power consumption, which is one of the disadvantage in both high & low performance system, has become a center of attention in VLSI digital design.

A processor is an important part of any digital system and an ALU is one of the prime components of any processor. CPU is the brain of a computer. It contains quick dynamic logical circuits and optimized structures. Considering total power consumption in any of the processors, the major contributions to it is from CPU.

This paper consist of design of ALU using both CMOS and GDI technique. Then we compare few performance characteristic such as average power ,area and then conclude that design of ALU using GDI is better than ALU using CMOS. Morgenshtein was the

### II. INTRODUCTION TO GDI TECHNIQUE

There are various low power techniques that are available nowadays in which GDI is one of them. These days a GDI is the most commonly used technique for the purpose of power reduction as it reduces the switching of output. Also GDI technique is used in order to reduce the number of transistors required for the design which helps in reducing the area of chip. The most basic cell in a GDI technique is an inverter cell which is formed by the combination of a PMOS and a NMOS.

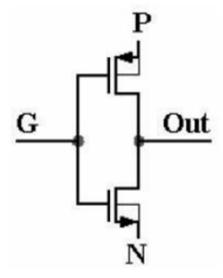

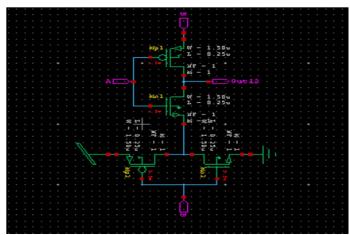

Figure 1. Basic cell of GDI

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue V, May 2018- Available at www.ijraset.com

The basic GDI cell fig 1 is shown above. The cell mainly consist of a pMOS and a nMOS. The basic cell of GDI looks similar to CMOS inverter, But the difference is that it has three inputs ping P,N and G.

- A. Input pin G is common gate of PMOS and NMOS.

- B. Input pin P is input to the source/drain of PMOS.

- C. Input pin N is input to the source/drain of NMOS.

GDI basic cell performs all the operations shown below in the form of a table

Input Sr.n P N Output Function 0 1 F1 A  $\mathbf{B}$ 0  $\overline{A}$ . B 2 A 1 B F2  $\overline{A} + B$ 3 В 1 A A+B OR 4 0 В A.B AND A 5 B C A  $\overline{A}$ . B + AC MUX 6 A 1 0 NOT  $\overline{\mathbf{A}}$

Table 1. Function Table of GDI

### III. ALU

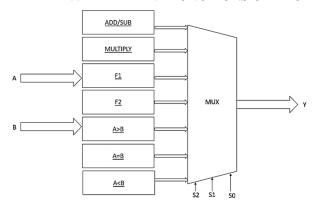

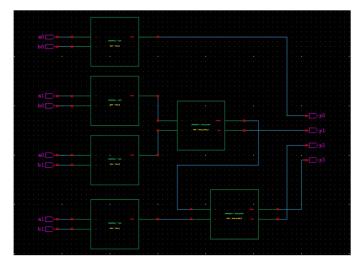

In the modern digital circuits, Processing speed of these circuit is the main requirement. A processor is considered to be the main part of any digital system and an ALU is one of the main components of a micro-processor. To give a simple analogy, CPU works as a brain to any system and ALU works as a brain to CPU. So it's a brain of computer's brain. The ALU is referred as the heart of any processor as all the operation performed by the processor is performed by the help of ALU only. It is also the extreme adaptable and useful part of processor as it consume most of the power of a processor. The block diagram of ALU is shown in figure. It consist of 2 input 'A' and 'B' in which both of them are of two bits. The above designed ALU can perform different operations such as addition, subtraction, multiplication, magnitude comparison and logical function such as f1 (a'b) and f2 (a'+b). The output from these different block may be up to four bits. All the output of the operations are given to a multiplexer (MUX). The MUX so design is 8:1 which means it can take 8 one bit inputs and give a single bit output. The MUX contain 2'n number of select lines in which n refers to number of inputs. Here, since there are 8 inputs, it contain 3 select lines namely S0,S1,S2. These select lines helps in selecting the different operations of ALU. For example, if the select lines are '000' then output of 2 bit addition is selected and if the select lines are '111', then comparator's output (A lesser than B) is selected.

### IV. DIFFERENT FUNCTIONS OF ALU

Figure 2.Block Diagram of ALU

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue V, May 2018- Available at www.ijraset.com

The circuit shown below performs the 2-bit addition/subtraction. It contains 2 input, each of two bits (A0, A1 and B0,B1). Initial carry is made zero and another input is provided which helps in selecting either of the above arithmetic operations ('0' for Addition and '1' for Subtraction). The outputs are Sum and Carry. This circuit performs the bitwise addition/subtraction. It is designed using Half-adders and logic gates such as and gate, or gate and xor gate.

### A. Multiplication

Multiplication is one of the arithmetic operation. Multiplication performed is bitwise and is similar to the multiplication performed in decimal numbers. The bitwise multiplication follows a procedure to produce result that is similar to that of decimal multiplication0\*0=0, 0\*1=0, 1\*1=1, and 1\*0=0). The bitwise multiplication is much simpler as it contains only bit '0' and bit '1'. The bitwise multiplication is performed with help of partial product addition and a shifting method.

### B. Function F1 And F2

By using these function we can express the any other function or implementation of complex function using the blocks of this function. The functions are given by F1=A'B, F2=A'+B.

### C. Comparator

Binary or Digital comparators are made up from standard AND, NOR and NOT gates that compare the digital signals present at their input terminals and produce an output depending upon the condition of those inputs. The purpose of a Digital Comparator is to compare a set of variables or unknown numbers, for example A (A1, A2, A3, .... An, etc.) against that of a constant or unknown value such as B (B1, B2, B3, .... Bn, etc.) and produce an output condition or flag depending upon the result of comparison.

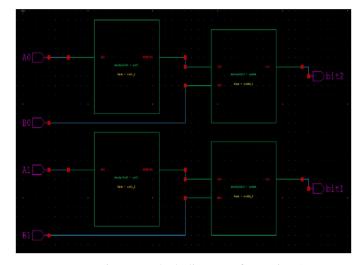

Figure 2. AND gate using CMOS

Figure 3. AND gate using GDI

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue V, May 2018- Available at www.ijraset.com

Figure 4. XOR gate using GDI

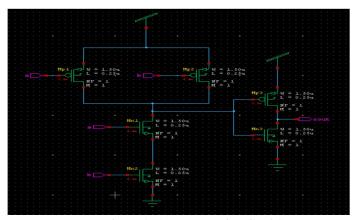

The figure 3, 4 and 5 shows the design of basic gates using CMOS and GDI techniques. Figure 5, 6 and 7 shows block diagram of few functions of ALU.

Figure 5. Block Diagram of Multiplier

Figure 6. Block diagram of Function 1

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue V, May 2018- Available at www.ijraset.com

### V. SIMULATIONS

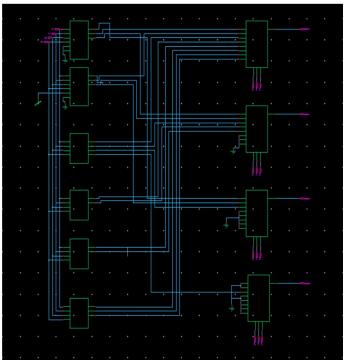

The figure 8 shows the integration of all the operations of ALU.

Figure 7. Combination of all Functional circuits

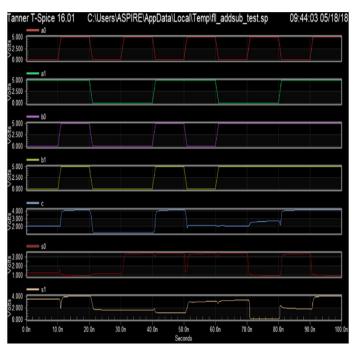

All the operations performed by ALU such as Arithmatic functions, Logical function and Comparison function blocks are combined and given to a MUX. The required operation have to select by giving the values to the select lines of MUX. The waveform of the ALU using GDI shown in figure 9.

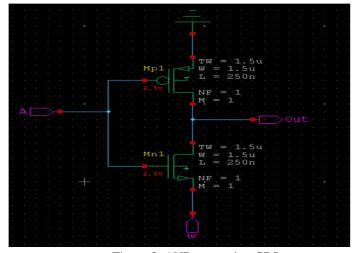

Figure 8. Simulation output of Adder using GDI

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue V, May 2018- Available at www.ijraset.com

### VI. RESULTS

Arithmetic and Logic Unit is implemented using both CMOS and GDI techniques. It is found that the power consumed by GDI circuit is more than that of CMOS circuit for 2.5 voltage input.

| COMPONENTS | CMOS    | GDI     | POWER  |

|------------|---------|---------|--------|

|            | (watts) | (watts) | SAVED  |

| AND GATE   | 1.19e-  | 6.19e-  | 98%    |

|            | 006     | 013     |        |

| OR GATE    | 6.74e-  | 1.07e-  | 84.12% |

|            | 007     | 007     |        |

| XOR GATE   | 2.83e-  | 7.01e-  | 75.22% |

|            | 006     | 007     |        |

| FUNCTION 1 | 1.13e-  | 6.193e- | 98%    |

| (A'B)      | 006     | 013     |        |

| FUNCTION 1 | 1.09e-  | 1.006e- | 90.77% |

| (A'+B)     | 006     | 007     |        |

Table 2. Comparison of Power Consumed by Basic gates

The number of transistor required to build an ALU tabulated.

| CMOS | GDI |

|------|-----|

| 1008 | 414 |

Table 3. Transistor count to build ALU

The transistor count to build ALU indicate that less number of transistors are required, if GDI technique is used. We can also observe that transistor count doubles if CMOS technique is used. This indicate that the area of the circuit reduces if GDI technique is used. Since the number of transistors required reduces, speed of the operation increases.

### VII. CONCLUSION

In this paper, First, We have examined about the design of ALU using CMOS. Later, we have designed the same circuit using low power technique named as GDI. These implementations been done using new Electronic Design Automation Tool called TANNER. Later we have compared few performance characteristics such as power consumption, area of both circuits. By the above result we concluded that, as the power consumption and number of transistor used is lesser in GDI circuits, GDI technology provides better performance than that of the traditional CMOS technology.

### **REFERENCES**

- [1] Arkadiy Morgenshtein, IdanShwartz and Alexander Fish, "Gate Diffusion Input (GDI) Logic in Standard CMOS Nanoscale Process", IEEE 26-th Convention of Electrical and Electronics Engineers, Israel, 2010.

- [2] Anand N George Joseph, Suwin Sam Oommen and K Sivasankaran,"ASIC Implementation of a High Speed Error Tolerant Adder". International Conference on Electronics and Communication Systems (ICECS), February 2014.

- [3] P. Yadav, G. Kumar, S. Gupta, Design and Implementation of 4-BitArithmetic and Logic Unit Chip with the Constraint of Power Consumption IOSR Journal of Electronics and CommunicationEngineering (IOSR-JECE). Volume 9, Issue 3, Ver. V (May Jun.2014).

- [4] A. K. Sharma, A. Jain Designing of Low Power Low Area Arithmetic and Logic Unit, International Journal of Innovative Research in Computer and Communication Engineering

- [5] A. Rahut, A.V.Nandi, S.S.Kerur, H.Kittur, Design and simulation of 4- bit ALU Design using GDI Technique for Low Power Application on Micro wind 2.6K, International Journal & Magazine of Engineering, Technology, Management and Research.

- [6] Tripti Sharma, K.G.Sharma and B.P.Singh, "High Performance Full Adder Cell: A Comparative Analysis", 2010 IEEE Students' Technology Symposium 3-4 April 2010, IITKharagpur, 2010.

- [7] Rajkumar Sarmal and Veerati Raju," Design and Performance Analysis of Hybrid Adders For High Speed Arithmetic Circuit", International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.3, June 2012.

- [8] M. Shoba, R. Nakkeeran, "GDI based full adders for energy efficientarithmetic applications", Engineering Science and Technology, anInternational Journal, vol. 19, no. 1, pp. 485–496, Mar. 2016.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)