# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 6 Issue: VI Month of publication: June 2018

DOI: http://doi.org/10.22214/ijraset.2018.6072

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue VI, June 2018- Available at www.ijraset.com

### VLSI Design of a Novel Architecture for Data Encoding with Golay codes

E.Odevi<sup>1</sup>, V. B. K. L. Aruna<sup>2</sup>

<sup>1</sup>Studying M.Tech. in VLSI & ES specialization, Velagapudi Ramakrishna Siddhartha Engineering College, Jawaharlal Nehru Technological University -Kakinada, Kanuru, Vijayawada-7, Andhra Pradesh)

<sup>2</sup>Assistant Professor, Electronics and Communication Engineering department, Velagapudi Ramakrishna Siddhartha Engineering College, Jawaharlal Nehru Technological University -Kakinada, Kanuru, Vijayawada-7, Andhra Pradesh)

Abstract: There is an expanding interest for productive and dependable transmission of computerized information. A noteworthy worry here is the control of blunders for dependable generation of information. By appropriate encoding of data to a codeword with the assistance of Error Correction Codes (ECC), errors induced can be reduced. The proposed architecture parallelizes the comparison of the data and that of the parity information. To further reduce the latency and complexity, in addition, a new butterfly-formed weight accumulator (BWA) is proposed for the proficient calculation of the Hamming separation. Grounded on the BWA, the proposed design analyzes whether the approaching information coordinates the put away information if a specific number of wrong bits are amended. The proposed engineering is actualized by utilizing xilinx14.7 form and the trial comes about demonstrate that the proposed design lessens the dormancy and the equipment multifaceted nature separately. In expansion we do Golay code for more decrease in the idleness. Golay code is a different mistake adjusting parallel code equipped for remedying a blend of three or couple of arbitrary blunders in a piece of 23 digits. The Comparison of Golay Code and BWA is due to Delay and Speed.

Keywords: Data Comparison, Hamming distance, Systematics codes, Tag matching, Error correcting codes (ECCs), Encoder, CRC, Golay code.

#### I. INTRODUCTION

Information examination is generally utilized as a part of processing frameworks to perform numerous activities, for example, the label coordinating in a store memory and the virtual-to-physical address interpretation in an interpretation look aside support (TLB). An interpretation look aside support (TLB) is a memory store that is utilized to diminish the time taken to get to a client memory area. It is a piece of the chip's memory-administration unit (MMU). The TLB stores the current interpretations of virtual memory to physical memory and can be called an address-interpretation reserve [1]. A TLB may dwell between the CPU and the CPU store, between CPU reserve and the fundamental memory or between the distinctive levels of the multi-level reserve [2]. The greater part of work area, workstation, and server processors incorporate at least one TLBs in the memory-administration equipment, and it is almost constantly exhibit in any processor that uses paged or divided virtual memory [3]. In view of such pervasiveness, it is critical to execute the correlation circuit with low equipment many-sided quality. Moreover, the information examination more often than not lives in the basic way of the segments that are contrived to build the framework execution, e.g., stores and TLBs, whose yields decide the stream of the succeeding tasks in a pipeline [4]. The circuit, in this way, must be intended to have as low inactivity as could reasonably be expected, or the segments will be excluded from filling in as quickening agents and the general execution of the entire framework would be seriously crumbled. As late PCs utilize blunder remedying codes (ECCs) to ensure information and enhance dependability [5]. In registering, media transmission, data hypothesis, and coding hypothesis, a blunder remedy code, once in a while mistake redressing code, (ECC) is utilized for controlling blunders in information over inconsistent or boisterous correspondence channels. The focal thought is the sender encodes the message with a repetitive as an ECC [6]. confounded interpreting system, which must go before the information examination, prolongs the basic way and fuels the multifaceted nature overhead. Accordingly, it turns out to be significantly harder to meet the above plan requirements. In spite of the requirement for complex outlines as depicted, the works that adapt to the issue are not generally known in the writing since it has been typically treated inside enterprises for their items. As of late, be that as it may, set off the fascination of an ever increasing number of considerations from the scholarly field [7]. The most recent solution for the matching problem is the direct compare method [8], which encodes the incoming data and then compares it with the retrieved data that has been encoded as well. Therefore, the method eliminates the complex decoding from the critical path.

#### II. EXISTING SYSTEM

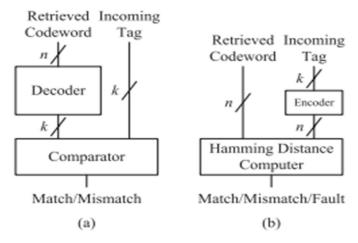

#### A. Decode-and-Compare Architecture

Give us a chance to consider a reserve memory where a k-bit tag is put away as a n-bit codeword subsequent to being encoded by a (n, k) code. In the unravel and-think about engineering delineated in Fig. 1(a), the n-bit recovered codeword should first be decoded to extricate the first k-bit tag. The extricated k-bit tag is then contrasted and the k-bit label field of an approaching location to decide if the labels are coordinated or not. As the recovered codeword ought to experience the decoder before being contrasted and the approaching tag, the basic way is too long to ever be utilized in a functional reserve framework intended for fast access. Since the decoder is a standout amongst the most entangled handling components, moreover, the multifaceted nature overhead isn't unimportant.

#### B. Encode-And-Compare Architecture

Note that translating is typically more perplexing and takes additional time than encoding as it includes a progression of mistake location or disorder count, and blunder adjustment [7]. The execution brings about help the claim. To determine the disadvantages of the unravel and-think about engineering, along these lines, the deciphering of a recovered codeword is supplanted with the encoding of an approaching tag in the encode-and-look at design More correctly, a k-bit approaching tag is first encoded to the relating n-bit codeword X and contrasted and a n-bit recovered codeword Y as appeared in Fig. 1(b). The examination is to analyze what number of bits the two code words vary, not to check if the two code words are precisely equivalent to each other. For this, we figure the Hamming separation d between the two code words and order the cases as per the scope of d. Let tmax and rmax signify the quantities of maximally correctable and discernible blunders, separately. The cases are outlined as takes after.

If d = 0, X matches Y exactly.

If  $0 < d \le t \max$ , X will match Y provided at most tmax errors in Y are corrected.

If  $tmax < d \le rmax$ , Y has detectable but uncorrectable errors. In this case, the cache may issue a system fault so as to make the central processing unit take a proper action.

Fig. 1.(a) Decode-and-compare architecture and (b) encode-and-compare architecture.

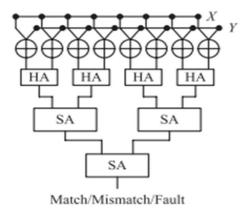

Since the above strategy needs to process the Hamming separation, exhibited a circuit devoted for the calculation. The circuit appeared in Fig. 2 initially performs XOR activities for each match of bits in X and Y in order to create a vector speaking to the bitwise contrast of the two code words. The accompanying half adders (HAs) are utilized to include the quantity of 1's two neighboring bits in the vector. The quantities of 1's are amassed by going through the accompanying SA tree. In the SA tree, the collected esteem z is soaked to rmax + 1 in the event that it surpasses rmax. All the more accurately, given data sources x and y, z can be communicated as takes after:

$$z = x + y$$

, if  $x + y \le rmax$

$rmax + 1$ , otherwise. (1)

The final accumulated value indicates the range of d. As the compulsory saturation necessitates additional logic circuitry, the complexity of a SA is higher than the conventional adder

Fig. 2. SA-based architecture supporting the direct compare method.

#### III. BWA ARCHITECTURE

This section presents a new architecture that can reduce the latency and complexity of the data comparison by using the characteristics of systematic codes. In addition, a new processing element is presented to reduce the latency and complexity further.

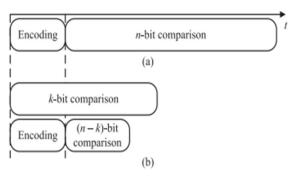

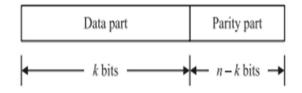

#### A. Datapath Design for Systematic Codes

In the SA-based architecture, the comparison of two code words is invoked after the incoming tag is encoded. Therefore, the critical path consists of a series of the encoding and the n-bit comparison as shown in Fig. 3(a). However, did not consider the fact that, in practice, the ECC codeword is of a systematic form in which the data and parity parts are completely separated as shown in Fig. 4. As the data part of a systematic codeword is exactly the same as the incoming tag field, it is immediately available for comparison while the parity part becomes available only after the encoding is completed. Grounded on this fact, the comparison of the k-bit tags can be started before the remaining (n–k)-bit comparison of the parity bits. In the proposed architecture, therefore, the encoding process to generate the parity bits from the incoming tag is performed in parallel with the tag comparison, reducing the overall latency as shown in Fig. 3(b).

Fig. 3. Timing diagram of the tag match in (a) direct compare method (b) proposed architecture.

Fig. 4. Systematic representation of an ECC codeword

#### B. Architecture for Computing the Hamming Distance

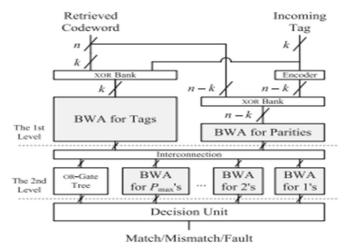

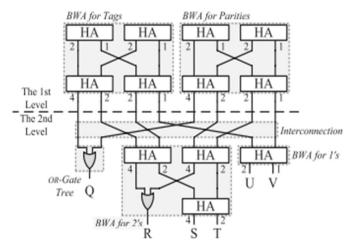

The proposed architecture grounded on the datapath design is shown in Fig. 5. It contains multiple butterfly-formed weight accumulators (BWAs) proposed to improve the latency and complexity of the Hamming distance computation.

Fig. 5. BWA architecture for systematic code words

The basic limit of the BWA is to count the amount of 1's among its information bits. It contains different periods of HAs as showed up in Fig. 6(a), where each yield bit of a HA is connected with a weight. The HAs in a stage are related in a butterfly shape with a specific end goal to accumulate the pass on bits and the total bits of the upper stage freely. All things considered, the two commitments of a HA in a stage, except for the primary stage, are either pass on bits or whole bits figured in the upper stage. This affiliation methodology prompts a property that if a yield bit of a HA is set, the amount of 1's among the bits in the ways accomplishing the HA is proportional to the largeness of the yield bit. In Fig. 6(a), for example, if the pass on bit of the diminish shaded HA is set, the amount of 1's among the related data bits, i.e., A, B, C, and D, is 2. At the last period of Fig. 6(a), the amount of 1's among the data bits, d, can be found out as

$$d = 8I + 4 (J + K + M) + 2 (L + N + O) + P. (2)$$

The corresponding first and second level circuits are shown in Fig. 7. Note that the encoder and XOR banks are not drawn in Fig. 7 for the sake of simplicity. Since rmax = 2, Pmax = 2 and there are only two BWAs dealing with weights 2 and 1 at the second level. As the bits of weight 4 fall in the fourth range, they are ORed. The remaining bits associated with weight 2 or 1 are connected to their corresponding BWAs. Note that the interconnection induces no hardware complexity, since it can be achieved by a bunch of hard wiring.

Fig. 6. First and second level circuits for a (8, 4) code.

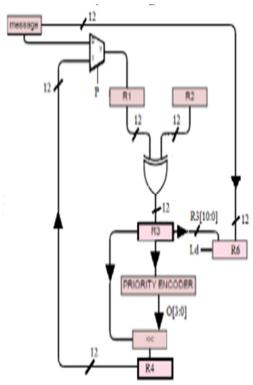

#### IV. EXTENSION

By proper encoding of information to a codeword with the help of Error Correction Codes (ECC), errors induced can be reduced [9] [10]. The (23, 12) Golay code is a multiple error correcting binary code capable of correcting an combination of three or few random errors in a block of 23 digits. For hardware implementation of encoding process, Linear Feedback Shift Register (LFSR) based cyclic redundancy check (CRC) generation method is preferred conventionally [11]. Due to drawbacks like high latency and less throughput, this technique is not a suitable solution for high-speed applications. Here, a technique based on CRC method, without using LFSR's, proposed in [12] is considered for the encoding of golay code. Golay code with minimum distance of seven is the only known multiple error correcting binary perfect code. The binary Golay code is represented as (23, 12, 7) that depicts that length of codeword is 23 bits, while message is of 12 bits and the minimum distance between two binary Golay codes is 7. This code can be in cyclic form, hence it can be decoded or encoded using its cyclic structure. The generation of coding sequence needs a generator polynomial. The possible generator polynomials over GF (2) for Golay (23, 12, 7) code are

$$G(x) = x11 + x10 + x6 + x5 + x4 + x2 + x1$$

$G(x) = x11 + x9 + x7 + x6 + x5 + x1 + 1.$

Encoding can be done by eleven stages Shift Register (SR) with feedback connections according to either of the above given G(x). The remainder of the long division gives the required check bits. Finally, appending the generated check bits with the message gives us the Golay codeword.

Fig.8 Architecture for generation of binary golay code

#### A. G23 Golay Code Generation

In each progression amid polynomial division, essentially twofold XOR activity happens for modulo-2 subtraction. The remaining outcome acquired at each progression amid the division procedure is circularly left moved by number of driving zeros present in the outcome. The leftover outcome acquired after twofold XOR activity is put away in R3 enroll. The estimation of the generator polynomial (here, 1010 1110 0011) with which the XOR activity happens is put away in the R2 enroll. A 12:4 need encoder productively distinguishes the quantity of driving zeros previously initial 1 bit in the lingering result in each progression and its yield is signified by o[3:0]. A round move enlist (<<) is utilized to move the transitional outcome by the quantity of driving zeros i.e. the yield of need encoder. The outcome acquired in the wake of moving task is put away in R4 enroll. A 2:1 multiplexer is utilized to choose either the underlying message or the circularly moved middle of the road result from the R4 enlist. The control flag utilized for the multiplexer is meant as p, which takes an esteem zero when the message comes and an esteem one after that.

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue VI, June 2018- Available at www.ijraset.com

#### A. Proposed

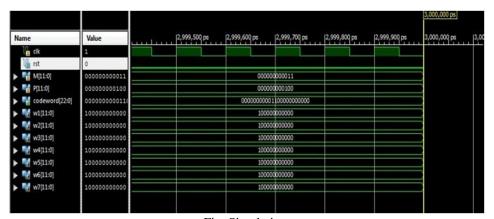

#### V. RESULTS

|                    |          |          | 2,003.320 ns |          |          |          |

|--------------------|----------|----------|--------------|----------|----------|----------|

| Name               | Value    | 1,500 ns | 2,000 ns     | 2,500 ns | 3,000 ns | 3,500 ns |

| ▶ 📑 rt[7:0]        | 00000011 | 0000000  | 0000         | 0011     | 1010101  |          |

| ▶ <b>I</b> it[3:0] | 1000     | 0000     | 10           | 00       | 0110     |          |

| 1 match            | 0        |          |              |          |          |          |

| 1 mismatch         | 1        |          |              |          |          |          |

| la fault           | 0        |          |              |          |          | 8        |

| ► <b>™</b> П[7:0]  | 10000111 | 00000000 | 1000         | 0111     | 0110011  |          |

| x[7:0]             | 10000100 | 0000000  | 1000         | 0100     | 1100110  |          |

| ▶ <b>₹</b> xt[3:0] | 1000     | 0000     | 10           | 00       | 1100     |          |

| ▶ 🦏 xp[3:0]        | 0100     | 0000     | 01           | 00       | 1100     |          |

| ▶ <b>d</b> [3:0]   | 0010     | 0000     | 00           | 10       | 0100     |          |

| ▶ ■ a[5:0]         | 100000   | 000000   | 100          | 000      | 010000   |          |

|                    |          |          |              |          |          |          |

Fig. Simulation.

#### B. Extension

Fig. Simulation.

#### Comparison Table

| Design    | Delay(ns) |  |  |

|-----------|-----------|--|--|

| Proposed  | 1.899     |  |  |

| Extension | 0.284     |  |  |

#### VI. CONCLUSION

To reduce the latency and hardware complexity, another engineering has been exhibited for coordinating the information secured with an ECC. The proposed design looks at whether the approaching information coordinates the put away information if a specific number of incorrect bits are redressed. To lessen the idleness, the examination of the information is parallelized with the encoding procedure that creates the equality data. The parallel activities are empowered in view of the way that the precise codeword has isolate fields for the information and equality. What's more, a productive preparing design has been displayed to additionally limit the inertness and multifaceted nature. As the proposed design is successful in diminishing the idleness and additionally the multifaceted nature impressively, it can be viewed as a promising answer for the correlation of ECC-secured information. In expansion to diminishing idleness, Golay code is an impeccable code that can redress up to 3 blunders in a square of 24bits. Different encoder models were produced to encode. Being a cyclic code, encoders for golay code were for the most part in light of LFSR's. The applications used in digital communication systems and high speed.

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue VI, June 2018- Available at www.ijraset.com

#### REFERENCES

- [1] J. Chang, M. Huang, J. Shoemaker, J. Benoit, S.-L. Chen, W. Chen, S. Chiu, R. Ganesan, G. Leong, V. Lukka, S. Rusu, and D. Srivastava, "The 65-nm 16-MB shared on-die L3 cache for the dual-core Intel xeon processor 7100 series," IEEE J. Solid-State Circuits, vol. 42, no. 4, pp. 846–852, Apr. 2007.

- [2] J. D. Warnock, Y.-H. Chan, S. M. Carey, H. Wen, P. J. Meaney, G. Gerwig, H. H. Smith, Y. H. Chan, J. Davis, P. Bunce, A. Pelella, D. Rodko, P. Patel, T. Strach, D. Malone, F. Malgioglio, J. Neves, D. L. Rude, and W. V. Huott "Circuit and physical design implementation of the microprocessor chip for the zEnterprise system," IEEE J. Solid-State Circuits, vol. 47, no. 1, pp. 151–163, Jan. 2012

- [3] H. Ando, Y. Yoshida, A. Inoue, I. Sugiyama, T. Asakawa, K. Morita, T. Muta, and T. Motokurumada, S. Okada, H. Yamashita, and Y. Satsukawa, "A 1.3 GHz fifth generation SPARC64 microprocessor," in IEEE ISSCC. Dig. Tech. Papers, Feb. 2003, pp. 246–247.

- [4] M. Tremblay and S. Chaudhry, "A third-generation 65nm 16-core 32-thread plus 32-scout-thread CMT SPARC processor," in ISSCC. Dig. Tech. Papers, Feb. 2008, pp. 82–83.

- [5] AMD Inc. (2010). Family 10h AMD Opteron Processor Product Data Sheet, Sunnyvale, CA, USA[Online].Available: http://support.amd.com/us/Processor\_TechDocs/40036.pdf

- [6] Byeong Yong Kong, Jihyuck Jo, Hyewon Jeong, Mina Hwang, Soyoung Cha, Bongjin Kim, and In-Cheol Park, "Low-Complexity Low-Latency Architecture for Matching of Data Encoded with Hard Systematic Error-Correcting Codes", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 22, No. 7, July 2014

- [7] S. Lin and D. J. Costello, Error Control Coding: Fundamentals and Applications, 2nd ed. Englewood Cliffs, NJ, USA: Prentice-Hall, 2004

- [8] W. Wu, D. Somasekhar, and S.-L. Lu, "Direct compare of information coded with error-correcting codes," IEEE Trans. Very Large Scale Integr.(VLSI) Syst., vol. 20, no. 11, pp. 2147–2151, Nov. 2012.

- [9] Sarangi, Satyabrata, and Swapna Banerjee. "Efficient Hardware Implementation of Encoder and Decoder for Golay Code." Very Large Scale Integration (VLSI) Systems, IEEE Transactions on 23.9 (2015): 1965-1968

- [10] Su, Shin-Yuan, and Pai\_Chi Li. "Photoacoustic signal generation with Golay coded excitation." Ultrasonic Symposium (IUS), 2010IEEE. IEEE, 2010

- [11] Nair, Rajesh, Gerry Ryan, and Farivar Farzaneh. "A symbol based algorithm for hardware implementation of cyclic redundancy check(CRC)."VHDL International Users' Forum, 1997. Proceedings. IEEE, 1997

- [12] Pless, Vera. Introduction to the theory of error-correcting codes. Vol. 48. John Wiley & Sons, 2011.

10.22214/IJRASET

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)