# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 7 Issue: V Month of publication: May 2019

DOI: https://doi.org/10.22214/ijraset.2019.5551

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177

Volume 7 Issue V, May 2019- Available at www.ijraset.com

### Delay and Power Analysis of Three Coupled through Silicon Vias in 3D ICs

Vishnu Vardhan Reddy<sup>1</sup>, Mekala Girish Kumar<sup>2</sup>, Sreenivasa Rao Gadela<sup>3</sup>

1, 2, 3 Dept. Of ECE (VLSISD), Vidya Jyothi Institute of Technology, Hyderabad, India

Abstract: 3D IC is developing as an incredible response for the next generation system packaging and integration technology to accomplish low power utilization, high channel transfer speed and high-density integration capability simultaneously. With respect to the vertical interconnect for a 3D IC, through-silicon via (TSV) is a key part which can produce a myriad performance improvement with the extraordinarily decreased length of interconnects among vertically stacked dies. In this paper, the electrical equivalent model of a TSV is proposed and the electrical behaviour of three coupled TSV with the variation of length, diameter, and pith parameters are analysed.

Keywords: Through Silicon Vias (TSVs), Three-Dimensional Integrated Circuits (3D ICs), Packaging

### I. INTRODUCTION

The legacy of planar scaling which has been satisfying the forecast in Moore's Law is at the edge of saturation. As technology advances in the nanometre era, the packaging density and system performance of individual chips improve. One of the primary reasons for the saturation is the physical size involved with semiconductor lithography that puts the limit to the dimension of transistors. The other significant issue related to scaling is the interconnect innovation. However, the scaling of the minimum feature size of the transistor slows due to the limitations of leakage power consumption, process variation, and cost issues. Since the finish of the last decade, the main pattern in the hardware industry is to increment the integration density in electronic gadgets utilizing three-dimensional (3D) integration. In addition, many electronic devices, such as tablets, laptops, and smartphones, have become more compact, and, they must achieve multi-function and high-throughput computing performance simultaneously. The production of integrated circuits (IC) is an important factor in the field of microelectronics. At higher levels of integration, the two-dimensional architecture results in numerous bottlenecks because of the area and routing congestion such as memory bottle neck in multimedia System on chips (SOCs). As the user demands are high regarding functionality of the system, the complexity of chip design increases and requires a large number of transistors which increases the size and delay of the circuit. As a new powerful paradigm for next-generation system integration and packaging technology, 3-dimensional integration emerges as a promising solution. With 3D integration, many chips can be integrated into a vertical axis, thus improving the system bandwidth by reducing the physical lengths of the channels among the integrated chips. At present, researchers are acknowledging 3D integration by stacking integrated circuit (IC) dies, where vertical interconnection is the fundamental way to communicate with other submodules. Thus, to accomplish the ideal execution in 3D framework, TSV interconnection is the key innovation.

In earlier days, the production of IC was designed using cable connections to the individual chips in the package. This leads to longer interconnection that lowers the performance of the device. To avoid such limitations, the chips can be connected together in place of each chip individually bound to the package substrate [1]. These interconnections are mostly implemented through the use of Through Silicon Vias (TSV). A TSV is a vertical metallic pillar surrounded by a dielectric material that passes through out the stacked plane matrices. By using TSVs the length of the interconnection has been lowered, this lowering significantly enhances device performance by decreasing power consumption and delay. The electrical property of a GSSG structure is analysed and implemented an accurate lumped model for the performance prediction of a TSV and studied about the bump radius, height and underfill material role in TSV performance and coupling factor [2]. The scalable and analytic electrical model is implemented for a TSV and the signalling performance and electrical behaviour at high frequencies are analysed in both frequency and time domains [3]. The Electromagnetic modelling for TSV interconnection is presented, that have an advantage of generating a model for large number of Through Silicon Vias using small number of basic functions that reduces the computational time [4]. However, few literatures are present on delay and power analysis it is very important to know the factors that are affecting these delay and power parameters. So, this paper mainly focused on these parameters.

The rest of this paper is composed of the following sections:

The architecture of TSV is discussed in Section II. The proposed TSV model is discussed in Section III. The simulations and results are discussed in Section IV. Some conclusions are offered in Section V.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177

Volume 7 Issue V, May 2019- Available at www.ijraset.com

### II. TSV ARCHITECTURE

A TSV consists of a cylindrical metallic pillar surrounded by a dielectric material that is used for connecting multiple devices in a chip. The top and bottom of this TSV is connected to bumps. The diameter of these bumps should be greater than the diameter of the TSV. The electromigration and scattering effects are lesser than the conventional wired interconnects and the transmission is uniform throughout the TSV. This helps in reducing the reliability issues and increases the device performance with low power consumption.

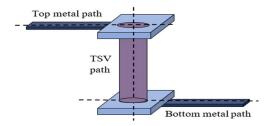

Fig. 1. TSV Structure

The above Fig. 1. Shows the structure of a single TSV connected to bumps on both top and bottom. The above figure is a 3D view of a TSV.

Fig. 2. TSV Top View

In Fig. 2. The total layers present in a TSV are clearly represented. The inner material is filled with the metal which is surrounded by a dielectric layer. These TSVs completely passes throughout the dies.

### III.PROPOSED TSV MODEL

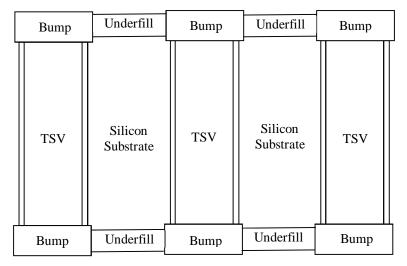

The proposed TSV model consists of three coupled interconnects that are connected parallelly which passes from top to bottom of 3D IC. The top and bottom of these TSVs are connected to bumps. These bumps are connected to underfill material that is used to form connectivity between chip and substrate.

Fig. 3. Proposed TSV Model

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue V, May 2019- Available at www.ijraset.com

The above Fig. 3 shows how the TSVs are located in the substrate. The bump diameter will be always greater than the diameter of TSV. Underfill is used to improve the reliability of a chip on a package, it is used to redistribute the thermomechanical stress created by the coefficient of thermal expansion (CTE) mismatch between organic substrate and silicon chip.

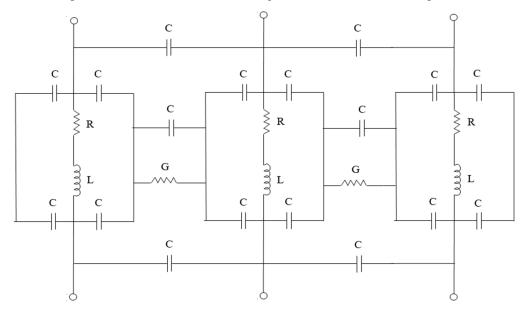

Fig. 4. RLCG Electrical Equivalent Model

The Fig. 4. Shows the RLCG components present in the circuit. Where R is the combination of TSV and Bump resistances, L is the combination of TSV and Bump Inductances, C is the combination of insulator and bump capacitances and G is the conductance of Silicon substrate. The top and bottom capacitors are the capacitances formed due to underfill material.

### IV. SIMULATIONS AND RESULTS

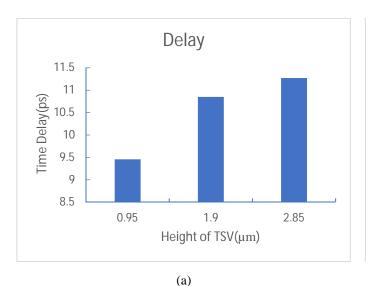

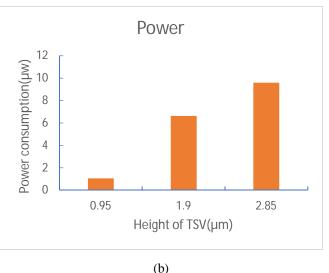

The Electrical behavior of the above TSV model is analyzed by varying the height, diameter and pitch of TSV individually. The delay and power consumption values are examined from the above analysis. The variation in speed and power consumption is observed when the height of TSV is varied. As the height increased the delay and the power consumed by TSV also increased which has a huge effect on the overall performance.

Fig. 5. Graphical representation of (a)Delay and (b)Power at different heights of a TSV

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177

Volume 7 Issue V, May 2019- Available at www.ijraset.com

The Fig. 5. Shows the impact of Height on delay and power. As the height is varied from 0.95 to 2.85  $\mu m$  the delay and power also increased gradually.

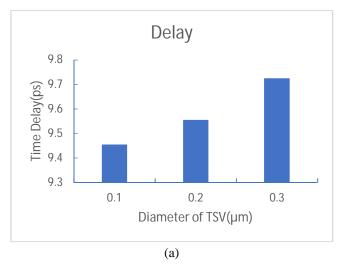

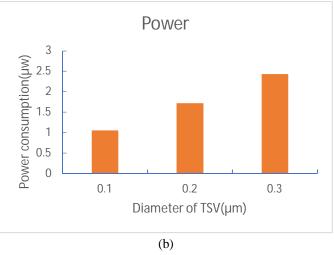

The variation in speed and power consumption is observed when the diameter of TSV is varied. As the diameter increased the delay and the power consumed by TSV also increased but of very less amount which will have a slight impact on the performance.

Fig. 6. Graphical representation of (a)Delay and (b)Power at different diameters of a TSV

The Fig. 6. Shows the impact of diameter on delay and power. As the diameter is varied from 0.1 to 0.3  $\mu m$  the delay and power are increased by having minor effects on reliability and performance.

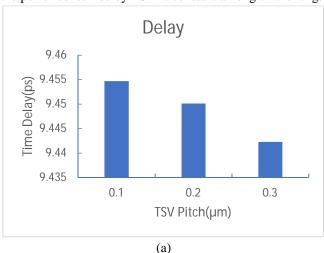

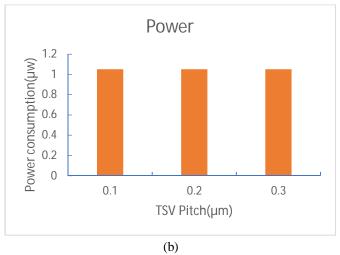

The variation in speed is observed when the pitch of TSV is varied. As the pitch increased the delay is decreased but negotiable and the power consumed by TSV is constant among all the lengths.

Fig. 7. Graphical representation of (a)Delay and (b)Power at different pitches of a TSV

The Fig. 7. Shows the impact of pitch on delay and power. Here pitch is the distance between TSVs. As the pitch is varied from 0.1 to  $0.3 \,\mu m$  the delay is slightly reduced and the power is constant. From the above analysis this variation in pitch will not have any influence on the overall performance.

### V. CONCLUSION

The Electrical Equivalent model for three coupled Through Silicon Vias (TSVs) was designed and studied the electrical behaviour of the designed model by varying the height, diameter and pitch parameters. The results of this analysis show that the height of TSV has major impact on the overall circuit that effects the total performance of the device. Whereas the other parameters have very slight impact but are considerable while using multiple TSVs.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue V, May 2019- Available at www.ijraset.com

### REFERENCES

- [1] Austin Lancaster, Manish Keswani, "Integrated circuit packing review with an emphasis on 3D packaging", Integration the VLSI journal http://dx.doi.org/10.1016/j.vlsi.2017.09.008.

- [2] Zhaowen Yan, Ting Kang, Wei Zhang, and Jianwei Wang, "Modeling and Electromagnetic Analysis of Multilayer Through Silicon Via Interconnect for 3D Integration", International journal of antennas and propagation, Vol. 2015, Article ID. 470952.

- [3] Joohee Kim, Jun So Pak, and Joungho Kim, "Electrical Modeling of a Through Silicon Via", Electrical Design of Through Silicon Via.

- [4] Ki Jin Han, Madhavan Swaminathan, and Tapobrata Bandyopadhyay, "Electromagnetic Modelling of Through-Silicon Via (TSV) Interconnections Using Cylindrical Model Basis Functions", IEEE Transactions on Advanced Packaging, Vol. 33, No. 4, November 2010.

- [5] Kumar M.G., Agarwal Y., Chandel R., "Timing and Stability Analysis of CNT Interconnects", IEEE international symposium on Nano electronic and Information systems (2015).

- [6] Agarwal Y., Kumar M.G., Chandel R., "Comprehensive Model for High-speed Current-Mode Signaling in Next Generation MWCNT Bundle Interconnect using FDTD Technique", IEEE Transactions on Nanotechnology. 15, 590-598 (2016).

- [7] Agarwal Y., Kumar M.G., Chandel R., "A Unified Delay, Power and Crosstalk Model for Current Mode Signaling Multiwall Carbon Nanotube Interconnects", 37, 1359—1382 (2018).

- [8] Kumar M.G., Agarwal Y., Chandel R., "An Efficient Crosstalk Model for Coupled Multiwalled Carbon Nanotube Interconnects", 60, 487-496 (2018).

- [9] Wen-Sheng Z., Jie Z., Yue H., Shilei S., Gaofeng W., Linxi D., Liyang Y., Lingling S., Wen-Yan Y., "High Frequency Analysis of Cu-Carbon Nanotube Composite Through-Silicon Vias", IEEE Trans. Nanotechnology (2016).

- [10] L. Qian, Z. Zhu, and Y. Xia, "Study on transmission characteristics of carbon nanotube through silicon via interconnects," IEEE Microw. Wireless Compon. Lett., vol. 24, no. 12, pp. 830–832, Dec. 2014.

- [11] D. Jiang, W. Mu, S. Chen, Y. Fu, K. Jeppson, and J. Liu, "Vertically stacked carbon nanotube based interconnects for through silicon via application," IEEE Electron Device Lett., vol. 36, no. 5, pp. 499–501, May 2015.

- [12] Madhav rao, "Vertical delay modeling of copper/carbon nanotube composites in a tapered through silicon via", IEEE 67th Electronic components and technology, 2017.

- [13] Andrea G. Chiariello, Antonio Maffucci and Giovanni Miano, "Electrical Modeling of Carbon Nanotube Vias", IEEE transactions on electromagnetic capability, Vol. 54, NO. 1, Feb 2012.

- [14] C. Xu, H. Li, R. Suaya, and K. Banerjee, "Compact AC modeling and performance analysis of through-silicon vias in 3-D ICs," IEEEE Trans. Electron Devices, vol. 57, no. 12, pp. 3405–3417, Oct. 2010.

- [15] A. G. Chiariello, A. Maffucci, and G. Miano, "Electrical modeling of carbon nanotube vias," IEEE Trans. Electromagn. Compat., vol. 54, no. 1, pp. 158–166, Feb. 2012.

3356

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)