# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 3 Issue: V Month of publication: May 2015

DOI:

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

## High Speed Noise Tolerant Domino Circuit For Wide Fan-in AND-OR Gates

K.Rajasri<sup>1</sup>, M.Manikandan<sup>2</sup>

<sup>1</sup>M.E, Applied Electronics, IFET College of Engineering, Villupuram, Tamilnadu, India <sup>2</sup>Assistant Professor, IFET College of Engineering, Villupuram, Tamilnadu, india

Abstract: In this paper, a new technique is proposed for wide fan-in OR gates. Here the current comparison based domino circuit is used to design a low leakage, high speed wide fan-in circuit. Dynamic gates have been excellent choices in the design of high performance modules in modern microprocessors. Dynamic gates are indispensable for constructing wide high-speed OR and AND-OR gates in CMOS. They are especially useful in multiport memories, where single-ended read bit-lines are needed for compactness and (even) low-power consumption. Circuits implemented with dynamic logic have very low parasitic capacitance and the number of transistors required in this technique is very less compared to static CMOS logic. This wide fan-in OR gates are simulated using 14nm high performance predictive technology model demonstrate 60% power reduction and at least 2.41× noise-immunity improvement at the same delay compared to the standard domino circuits for 256-bit OR gates.

Keywords: Domino logic, high-speed domino circuit, leakage power, noise tolerance, transistor sizing.

#### I. INTRODUCTION

Dynamic logic gates and circuits have been excellent choice in the design of high-performance modules such as multiple bit adders, subtractors, multipliers, comparators, multiplexers, registers, etc in modern VLSI microprocessors. The advancement in fabrication technology along with the shrinking device size has allowed for placement of nearly two billion transistors on Intel's latest processor. The digital logic gates and circuits designed using dynamic domino technique is considerably faster than the logic gates and circuits designed with standard static logic style. The aggressive technology scaling to improve the performance as well as the integration level makes the noise play a major role in design parameters like area, power and speed. Therefore the digital integrated circuit noise has become one of the most important issues in the design of deep submicron VLSI chips. The robustness and performance of wide fan-in dynamic circuits significantly degrade with increasing levels of process variations and sub threshold leakage. A number of design techniques such as PMOS feedback keeper transistor method to prevent the dynamic node floating problem, precharging the internal nodes to eliminate the charge sharing problem and weak complementary p-network is constructed to improve the noise tolerance to the level of skewed static CMOS logic gates, have been developed in the past three decades to minimize the effect of noise in dynamic circuits. It is also shown that voltage scaling aggravates the crosstalk noise in the dynamic circuits and reduces circuit noise immunity, motivating the need for noise-tolerant circuit design. To design a high performance domino logic circuit, there are two most important factors to be considered when designing a keeper circuit. The first factor is the additional loading caused by the keeper and its control circuits and the second factor is the keeper circuit should be capable of switching off very fast. If the keeper circuit remains ON during evaluation it will compete for longer time with the NMOS network during the pull down process. Designing feedback keeper circuit for wide fan-in gates is a challenging task since the leakage current largely depends on increase in variability. High fan-in compact dynamic gates are often employed in performance-critical units of microprocessors and other high-performance VLSI circuits. The use of wide dynamic gates is strongly impacted by reducing noise margins and increasing leakage currents in sub-14nm low- devices. Traditionally, dynamic floating nodes have been avoided by employing a static path through a pull-up and/or pulldown device referred "keeper". The increase in the variability and magnitude of the leakage current has become a major bottleneck in realizing such wide OR gates. Especially, in case of dynamic logic gates, the robustness of the dynamic node has to be guaranteed across different process corners without significant loss in the performance. In this paper, a 256-bit wide fan-in OR gate circuit is designed using current comparison based domino circuit. This technique reduced the parasitic capacitance at dynamic node. This type of domino circuits consists of an current mirror to replicate the leakage current of a dynamic gate pulldown stack and thus tracks process, voltage, and temperature. In this paper the effect of temperature on the circuit performance is analyzed in detail by sweeping the temperature from 25°C to 70°C. The performance of the dynamic circuits can be significantly improved by precise design and properly sizing the transistors. Usually in all the digital circuits the transistor gate length remains uniform. So the size of the transistor in digital circuits depends on the width of the transistor. In this paper the 256-bit wide fan-in OR gate domino circuit is implemented with L=0.014µm technology along with a supply voltage of 0.7V.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

The paper is organized as follows. Section II details the circuit implementation and operation of the 256-bit wide fan-in OR gate using current comparison based domino techniques. Section III compares the performance of this circuit using the simulated results. Section IV concludes the paper.

#### A. Circuit Design

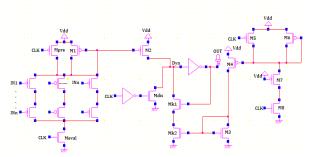

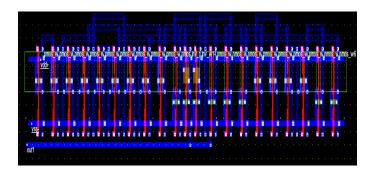

The circuit diagram of a wide fan-in OR gate circuit implemented using current comparison based domino (CCD) technique is shown in fig.1 and its layout is shown in fig.2. The wide fan-in OR gate circuit implemented using current comparison based domino (CCD) technique uses a current mirror to replicate the leakage current of the pull-up network and it tracks process, voltage, and temperature.

Fig.1.Wide fan-in OR gate using CCD

Fig.2. Layout of the wide fan-in OR gate circuit using current comparison based domino logic

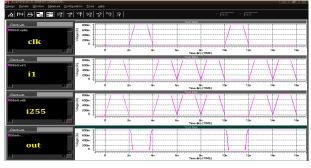

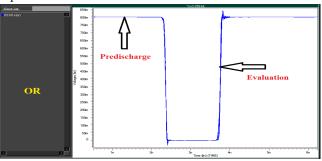

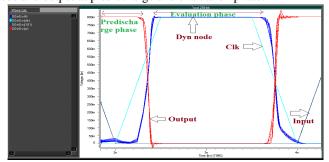

The timing diagram of a 256bit wide fan-in OR gate is shown in Fig.3. The timing diagram shows output of the circuit. From this timing waveform, we know that CCD circuit must operate in two phases predischarge phase and evaluation phase. During the predischage phases clk=0. So dynamic node is fully discharged. So we get output as high. During evaluation phase clk=1. It has two state. First state, all inputs are high. When all inputs are high, it has some leakage current in its dynamic node. It can be eliminated using reference current circuit. In second state, one of the input flows to low. It cause dynamic node to charged fully to Vdd. So we get output as low.

Fig.3 Timing diagram of the 256-bit wide fan-in OR gate using CCD

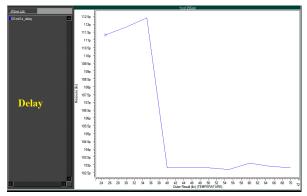

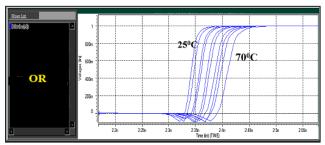

The Fig.4 shows, delay of 256 bit wide fan-in OR gate using CCD circuit. Delay varies depends on the temperature.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Temperature is main component of circuit. When the temperature increases gradually, delay of the circuit decreases. Because circuit get minimum amount of power. So it go to off stage.

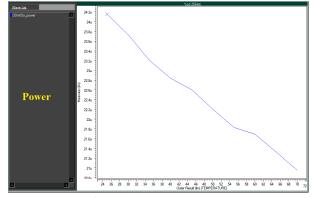

Fig.4 Delay Vs Temperature

Fig.5 Delay Vs Temperature

The Fig.5 shows effect of temperature on the power consumption of the circuit. When temperature increases, power of the circuit decreases. So the circuit performance get reduced.

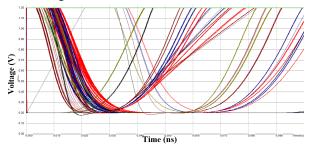

Fig. 6 Voltage Vs Time waveforms of 256-bit wide fan-in OR gate using CCD

Fig.7 Effect of temperature on the performance of 4-bit adder using LCR

The output voltage Vs Time characteristic of the 256-bit wide fan-in OR gate is shown in Fig.6. This eye diagram shows the precharing and evaluation of the circuit. In this wide fan-in OR gate circuit a current mirror is connected to the keeper which

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

compensates for the sub threshold leakage current of the pull-down network. This current mirror circuit can be shared for all the logic gates in the circuit. In this configuration the keeper and current mirror circuit minimizes the delay of the circuit (delay in the order of pico seconds) by minimizing the effect of charge sharing. This circuit need proper selection of clock signal. If the clock frequency exceeds 500MHz, the performance of the 256-bit wide fan-in OR gate circuit degrades. The effect of temperature on the performance of 256-bit wide fan-in OR gate circuit is shown in Fig.7. In this work the temperature is varied from  $25^{\circ}$ C to  $70^{\circ}$ C. From the fig.8 it is clear that as the temperature increases the transition delay also increases due to the increase in leakage current. The circuit is implemented using L=0.014 $\mu$ m technology with  $V_{DD}$  =0.7V. The simulation results shows that the circuit performance is superior in terms of speed and power compared to the adder circuits implemented using standard static logic circuit techniques.

Fig.8 Voltage Vs Time waveforms of 256-bit wide fan-in OR gate using CCD

The pre-charge and evaluation phases of the OR(output) of a 256-bit wide fan-in OR gate circuit designed using CCD technique is shown in Fig.8. As the clock frequency increases the output voltage decreases due to the parasitic capacitances. The operation of the circuit is as follows. When clock goes low, the dynamic node will be predischarged to  $V_{DD}$  (predischarge phase) and the output remains high in this condition. When the clock signal changes the state from low to high the circuit evaluate the logic function (evaluation phase) and the output remains low.

Fig. 9 Power Vs Time waveforms of 256-bit wide fan-in OR gate using CCD

In Fig.9, the Power Vs Time waveform of 256-bit wide fan-in OR gate is shown. When Power is zero, the current is also zero. That means the circuit is in OFF state. When the circuit consumes small amount of power, the current in the circuit is also increases. The current is in negative because PMOS is operate in reverse biased region. The PMOs is operate in negative voltage only. That's why the circuit has negative current. In this paper 256bit wide fan-in OR gate is presented with L=0.014µm technology and with a supply voltage of 0.7V. These high performance domino styles improve the scalability of multiple bit domino logic gates. Using these method it is possible to implement the wide fan-in circuits with a transistor gate length of L=10nm along with a supply voltage of 0.7V. These wide fan-in circuits are superior in performance compared to conventional static logic wide fan-in OR and AND gates. These circuits minimize the chip area, minimize the leakage power, and improve the noise tolerance without much speed degradation. Also the delay between the gates is now reduced to the order of pico seconds. These types of domino logic circuits can be used in high performance microprocessors.

### II.SIMULATION RESULTS

The simulations were performed using L= $0.014\mu m$  technology along with the supply voltage  $V_{DD}$ =0.7V. In this paper a 256-bit wide fan-in OR gate is constructed using current comparison based domino circuit. In this type of circuit a single reference current is used to share reference current to all the transistor in the circuit. Since a single current mirror structure can be shared among more than one domino logic circuits, the CCD technique is useful for constructing wide fan in circuits such as multiple

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

bit adders, registers, multiplexers etc. The Fig.10 shows simulation result of wide fan-in OR gate using CCD technique. It shows voltage at the different node and output at predischarge and evaluation phase.

Fig. 10. Simulation result

#### III. CONCLUSION

As the technology scales down, the leakage current of the pull down evaluation network increases, especially in wide fan in dynamic gates such as wide OR gates, wide AND-OR gates used in microprocessors. This will increase the power consumption and reduce the noise immunity. In this paper, the performance of 256-bit wide fan-in circuit designed using current comparison based domino circuit technique is analyzed in detail. The 256-bit wide fan-in OR gate circuit is simulated using L=0.014 $\mu$ m technology along with supply voltage  $V_{DD}$ =0.7V. The experimental results shows that these AND-OR gate circuits gives superior performance.

#### REFERENCES

- [1] Ali Peiravi and Mohammad Asyaei, "Current-Comparison-Based Domino: New Low-Leakage High-Speed Domino Circuit for Wide Fan-In Gates," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 21, no. 5, may 2013.

- [2] H. Mahmoodi and K. Roy, "Diode-footed domino: A leakage-tolerant high fan-in dynamic circuit design style," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 51, no. 3, pp. 495–503, Mar. 2004.

- [3] A. Alvandpour, R. Krishnamurthy, K. Sourrty, and S. Y. Borkar, "A sub-130-nm conditional-keeper technique," IEEE J. Solid-State Circuits, vol. 37, no. 5, pp. 633–638, May 2002

- [4] M. H. Anis, M. W. Allam, and M. I. Elmasry, "Energy-efficient noise-tolerant dynamic styles for scaled-down CMOS and MTCMOS technologies," IEEE Trans. Very Large Scale (VLSI) Syst., vol. 10, no. 2, pp. 71–78, Apr. 2002.

- [5] Y. Lih, N. Tzartzanis, and W. W. Walker, "A leakage current replica keeper for dynamic circuits," IEEE J. Solid-State Circuits, vol. 42, no. 1, pp. 48-55, Jan. 2007.

- [6] H. Suzuki, C. H. Kim, and K. Roy, "Fast tag comparator using diode partitioned domino for 64-bit microprocessors," IEEE Trans. Circuits Syst., vol. 54, no. 2, pp. 322–328, Feb. 2007.

- [7] H. F. Dadgour and K. Banerjee, "A novel variation-tolerant keeper architecture for high-performance low-power wide fan-in dynamic or gates," IEEE Trans. Very Large Scale (VLSI) Syst., vol. 18, no. 11, pp. 1567–1577, Nov. 2010.

- [8] L. Wang, R. Krishnamurthy, K. Soumyanath, and N. Shanbhag, "An energy-efficient leakage-tolerant dynamic circuit technique," in Proc. Int. ASIC/SoC Conf., 2000, pp. 221–225.

- [9] R. G. David Jeyasingh, N. Bhat, and B. Amrutur, "Adaptive keeper design for dynamic logic circuits using rate sensing technique," IEEE Trans. Very Large Scale (VLSI) Syst., vol. 19, no. 2, pp. 295–304, Feb. 2011. 65

- [10] K. Bowman, S. G. Duval, and J. D. Meindl, "Impact of die-to-die and within-die parameter fluctuations on the maximum clock frequency distribution for gigascale integration," IEEE J. Solid-State Circuits, vol. 37, no. 2, pp. 183–190, Feb. 2002.

- [11] C. H. Kim, K. Roy, S. Hsu, R. Krishnamurthy, and S. Borkar, "A process variation compensating technique with an on-die leakage current sensor for nanometer scale dynamic circuits," IEEE Trans. Very Large Scale (VLSI) Syst., vol. 14, no. 6, pp. 646–649, Jun. 2006.

- [12] R. G. David Jeyasingh, N. Bhat, and B. Amrutur, "Adaptive keeper design for dynamic logic circuits using rate sensing technique," IEEE Trans. Very Large Scale (VLSI) Syst., vol. 19, no. 2, pp. 295–304, Feb. 2011.

- [13] N. Shanbhag, K. Soumyanath, and S. Martin, "Reliable low-power design in the presence of deep submicron noise," in Proc. ISLPED, 2000, pp. 295-302.

- [14] R. H. Krambeck, Charles M. Lee, and Hung-fai Stephen Law, "High-Speed Compact Circuits with CMOS," IEEE Journal of Solid-State Circuits, vol. sc-17, no. 3, June 1982.

- [15] Li Ding and Pinaki Mazumder, "On Circuit Techniques to Improve Noise Immunity of CMOS Dynamic Logic," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 12, no. 9, september 2004.

- [16] Massimo Alioto, Gaetano Palumbo and Melita Pennisi, "Understanding the Effect of Process Variations on the Delay of Static and Domino Logic," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 18, no. 5, may 2010.

- [17] K.Rajasri, M.Manikandan, A.Bharathi "A Sub-22nm Wide fan-in gate Design using Domino circuit", IJSETR, vol.3, issue 11,pp. 2914-2918, Nov. 2014.

- [18] K.Rajasri, M.Manikandan, P.Santhini and S.Ashvini, "Design of Wide Fan-in OR gate using Domino Circuit in 45nm CMOS Technology", IJARECE, vol.3, issue 10, pp. 1327-1331,Oct. 2014.

- [19] M.Manikandan, K.Rajasri and A.Bharathi, "High Speed Low Power Noise Tolerant Multiple Bit Adder Circuit Design Using Domino Logic", IJARECE, vol.3, issue 10,pp. 1261-1266, Oct. 2014.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)