IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 7 Issue: VI Month of publication: June 2019

DOI: http://doi.org/10.22214/ijraset.2019.6443

### www.ijraset.com

Call: 🕥 08813907089 🔰 E-mail ID: ijraset@gmail.com

## Design and Implementation of Robust Router with Cache Memory using VLSI

Shikha Rai A<sup>1</sup>, Madhu Raghu<sup>2</sup>

<sup>1</sup>Assisstant Professor, Department of Electronics and Communication Engineering, SCEM College of Engineering, Adyar, Mangaluru, India

<sup>2</sup>Assisstant Professor, Department of Information Science and Engineering, SCEM College of Engineering, Adyar, Mangaluru, India

Abstract: The main approach here is to design a variable hardware router code by using Verilog and a VLSI design for the implementation at the synthesizable level. The focus is to make this router as much variable which will give the robustness for the design to be called as a Robust Router in which we can make the same router to not only go for N number of connections but also to detect all variety of packets and route the same. To do so code should be added with specific case's for every type of packets and to add to the router to route the packets. With this project an approach is to get the basic packets routing with multiple protocols starting with the IPv4 and IPv6.

Keywords: Robust Router, Multiple protocols with IPv4 and IPv6, strategies of data transmission.

#### I. INTRODUCTION

In today's market, communication is very important and also complex that it is not possible to communicate or send a data from more sources to destination at a time. The routing is done by simple software which will take more time, which has minimal set of pins and it is not possible to make it reconfigurable due its compactness, so HDL based robust router is designed which will help to configure for multiple input and output and it is also possible to communicate with high speed and it will take less time which is well robust at time we can communicate with the many source and destination.

In the emerging environment of high performance IP networks, it is expected that local and campus area backbones, enterprise networks, and Internet Service Providers (ISPs) will use multi giga bit and terabit networking technologies where IP routers will be used not only to interconnect backbone segments but also to act as points of attachments to high performance wide area links. Special attention must be given to new powerful architectures for routers in order to play that demanding role. It is observed that the achievement of high throughput IP routers is possible if the critical tasks are identified and special purpose modules are properly tailored to perform them.

#### II. RELATED WORK

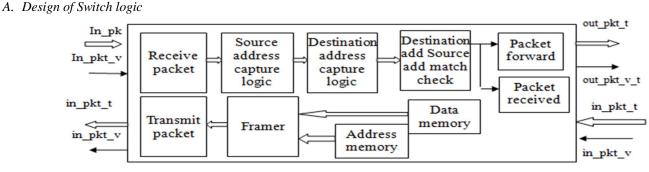

Fig 2.1: Design of Switch logic

Initially in\_pkt and in\_pkt\_v will be received by receive packet block. Then it will send it to source address and destination address decoder, then sent to source and destination address, source address match check. If address is matched packet is terminated and saved inside local memory. If not, it is forward by passing an out pkt\_t and out\_pkt\_v\_t. If assume that the switch is a receiving node which would be enabled by TCAM,TCAM interface in in\_pkt\_t and in\_pkt\_v will be sent to framer logic through address memory and data memory.

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177

Volume 7 Issue VI, June 2019- Available at www.ijraset.com

B. Design of Routing Lookup System

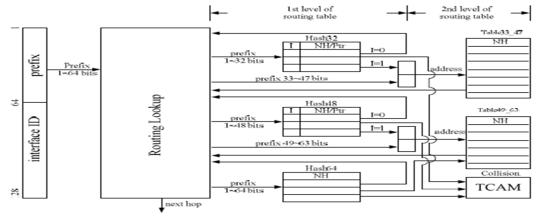

Fig 2.2 : The architecture of routing lookup system

The TCAM performs a parallel search to achieve high performance routing lookup. The second layer of the routing table contains two tables: TAB33\_47, which stores entries with prefixes lengths between 33 and 47 bits; and TAB49\_63, which stores entries with prefixes between 49 and 63 bits. The routing lookup ASIC contains the control unit, the datapath and the cache memory implemented in TCAM.

#### **III. EXPERIMENTAL RESULTS**

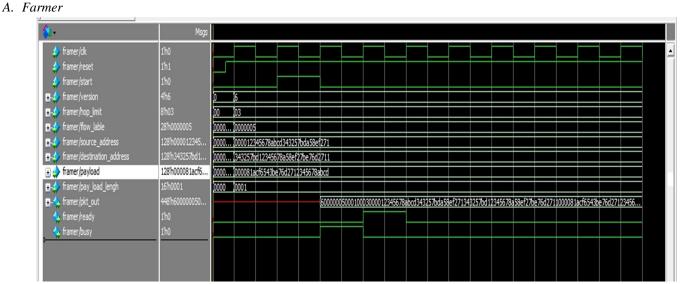

Fig 3.1 : Waveform showing the output of Framer

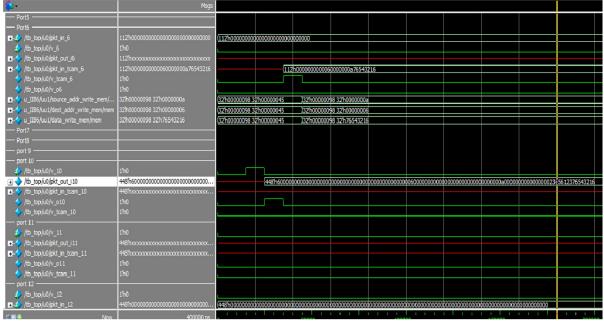

#### B. Payload Read Of A Farmer

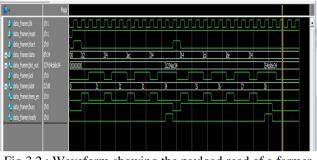

Fig 3.2 : Waveform showing the payload read of a farmer

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue VI, June 2019- Available at www.ijraset.com

C. Data Transmission And Conversion

Fig 3.3 Waveform showing the output of simple transfer and packet conversion.

When the enable signal on then the packet containing the source address a will be sent to the destination address 6 as specified. In this case the source address is of version 6 and destination address is of version 4. Hence conversion of version takes place.

#### **IV. CONCLUSION**

In high-speed networking applications, TCAM has been used as one of the principal components due to its ability to perform fully associative ternary search. This ability can be exploited to perform an wide range of operations, and new applications are still being discovered and implemented. To provide a fair comparison against past techniques when power is concerned, there is a need for an accurate TCAM power model that can be directly compared against comparable SRAM, cache, and logic models.

This Project is mainly concerned about providing robustness to the router for networking purpose with multiple protocols and multiple IP packets. Packet framing, reading packet from the memory and writing packet into the memory of the router is designed and the packet processing is done without collision. The TCAM is designed along with the v6/v4 converter. Hence This model will enable realistic energy estimations to be made across a wide range of TCAM based applications and designs. Presently the design is built and simulated for 16-nodes. It find difficulty to implement because of huge combinational logic as a reason implementation is realized for 8-nodes.

#### REFERENCES

- [1] "Data communication and networking", BEHROUZ A FOROUZAN

- [2] "Design and Implementation of Robust Router Using Vlsi" Shaik. Mallika et al. Int. Journal of Engineering Research and Application Vol. 3, Issue 5, Sep-Oct 2013

- [3] "A High Throughput ASIC Design for IPv6 Routing Lookup System" 978-1-4673-5762-3/13/\$31.00 ©2013 IEEE

- [4] H. Song, F. Hao, M. Kodialam and T. V. Lakshman, "IPv6 Lookups Using Distributed and Load Balanced Bloom Filters for 100Gbps Corer outer Line Cards," in Proc. IEEE INFOCOM, 2009.

- [5] Route Lookup Using Hash-Based Prefix-Compressed Trie," IEEE/ACM Transactions on Networking, vol. 20, no. 4, pp. 1262 1275, August 2012.

- [6] L. Luo, G. Xie, Y. Li, L. Mathy and K. Salamatian, "A Hybrid IP Lookup Architecture with Fast Updates," in Proc. IEEE INFOCOM, 2012.

- [7] H. Liu, "Reducing Cache Miss Ratio for Routing Prefix Cache," in Proc. IEEE GLOBECOM, 2002.

- [8] C.-S. Wu, W.-L. Shyu and T.-C. Hou, "Efficiency Analyses on Routing Cache Replacement Algorithms," in Proc. IEEE ICC, 2002.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)