# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 7 Issue: VII Month of publication: July 2019

DOI: http://doi.org/10.22214/ijraset.2019.7167

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177

Volume 7 Issue VII, July 2019- Available at www.ijraset.com

### Simulation and Analysis of LG SOI TFET

Monika Singh<sup>1</sup>, Suman Kumar Mitra<sup>2</sup>

<sup>1, 2</sup>Electronics and Communication Department, Harcourt Butler Technical University

Abstract: In this paper, LG SOI TFET is proposed and simulated. The tunneling junction in the LG SOI TFET is perpendicular to the channel direction that facilitates the implementation of a relatively large tunneling junction area which leads to increase in the drain curent. The channel is mainly distributed in the vertical direction, reducing the device area. This device feature high current drivability and abrupt on-off transition. The proposed LG SOI TFET shows higher on-current  $(I_{ON})$ . All the simulation is performed by using Sentaurus TCAD including nonlocal BTBT model.

Keywords: Tunnel Field Effect Transistor (TFET), L-Shaped Gate, Tunneling Junction, ON State Current ( $I_{ON}$ ), OFF State Current.

#### I. INTRODUCTION

As the Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) is scaled down for the low power consumption because MOSFET cannot have a Subthreshold Swing (SS) below to the conventional limit of 60mv/dec at the room temperature [1, 2]. To maintain a high ON current, Subthreshold Swing (SS) needs to be reduced. To overcome these limitations the Tunnel Field Effect Transistor (TFET) has proposed as one of the most promising device. TFET has attracted a great deal of attention for its low Subthreshold Swing (SS) and high ON state current at low power supply ( $V_{dd}$ ) [3, 4].

kink effect exists in the I<sub>d</sub>-Vg graph and it originates from abrupt change in source doping. Due to this subthreshold swing (SS) and on-state current (Ion) of TFETs have been degraded. To improve SS and Ion the kink effects should be avoided and rounding off the sharp edge of source corner [5]. Hump effects of L-Shaped TFET have been discussed. Hump effect seem to be originated from the extended source region so there are two TFETs in parallel whose Turn-on voltages ( $V_{turn-on}$ ) are different., Non local tunneling model and Quantum mesh are to be used for accurate calculation. During the fabrication process, source junction should be designed carefully [6]. High turn on voltages is problematic for low power application. By introducing n-type dopants in tunneling regions, the design of L-Shaped TFET has been improved. When  $N_D$  increases, both subthreshold swing and  $V_{turn-on}$  decrease. N-type dopants in tunneling Junction area can lower V<sub>turn-on</sub> while keeping SS low and I<sub>on</sub> high [7]. The tunneling junction is perpendicular to the direction of channel that provides large tunneling junction area. The U-Shaped Channel in the vertical direction that reduces the device area and makes the channel distribute in the vertical direction. Between source and intrinsic region, a N<sup>+</sup> pocket has been introduced to improve the characteristics of device. N<sup>+</sup> pocket region and gate overlap in vertical direction as well as lateral direction to enhance the electric field. That resulting in the 50% increment in ON state current as compared to other L-Shaped TFETs [8]. A PNPN TFET with L-Shaped gate is proposed for on- state current (I<sub>on</sub>) enhancement. The line and point tunneling between the source and  $N^+$  pocket by which the tunneling area has been enlarged effectively [9]. The three different types of tunneling structures are discussed on the basis of their single event transient performance, such as the conventional planar TFET, Planar TFET with pocket and L-Shaped TFET. Among all three TFET structures the L-Shaped TFET is far better [10].

In reality, the conventional planar silicon-based TFET has an inherent disadvantage of low ON-state current ( $I_{ON}$ ) because of silicon's relatively large band gap [11]. To improve ON state current, various techniques have been reported with simulation and experimental results. According to our previous research results, the former is originated from the small cross sectional area of tunneling junctions which is determined by channel inversion layer thickness. The latter is originated from the dependency of tunneling barrier width on the gate voltage ( $V_{ON}$ ) [12].

#### II. DEVICE STRUCTURE AND SIMULATION METHOD

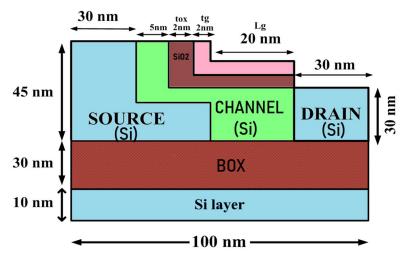

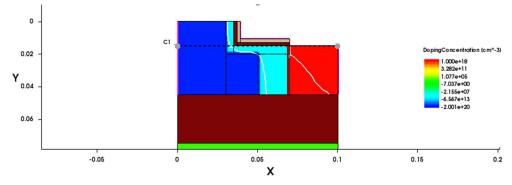

The proposed LG SOI TFET structure is illustrated in Figure 1. The gate resembles the alphabet "L" (PINK COLOUR). The proposed device makes band-to-band tunneling in both vertical and horizontal direction, which can effectively improve the device performance. LG SOI TFET has P-type doping of  $1x10^{20}$  cm<sup>-3</sup> and  $1x10^{17}$  in source and channel region respectively and N-type doping of  $1x10^{18}$  drain region. Simulation of the proposed device is carried out using Sentaurus TCAD including nonlocal BTBT model[13].

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue VII, July 2019- Available at www.ijraset.com

Figure 1. The Schematic Structure Of LG SOI TFET

TABLE 1

Device Parameters Used For The Simulation

| Device I drameters esed for the Simulation |                  |             |                  |  |  |

|--------------------------------------------|------------------|-------------|------------------|--|--|

| PARAMETER                                  | SYMBOL           | VALUE       | UNIT             |  |  |

| NAME                                       |                  |             |                  |  |  |

| Gate Oxide                                 | $t_{ox}$         | 2           | nm               |  |  |

| Thickness (SiO <sub>2</sub> )              |                  |             |                  |  |  |

| Source Height                              | $H_{S}$          | 45          | nm               |  |  |

| Drain Height                               | $H_D$            | 30          | nm               |  |  |

| Gate Length                                | $L_{\mathrm{g}}$ | 20          | nm               |  |  |

| Channel                                    | $t_{ch}$         | 5           | nm               |  |  |

| Thickness                                  |                  |             |                  |  |  |

| Channel Width                              | $W_{CH}$         | 30          | nm               |  |  |

| Source Doping                              | N <sub>S</sub>   | $1x10^{20}$ | cm <sup>-3</sup> |  |  |

| Drain Doping                               | $N_D$            | $1x10^{18}$ | cm <sup>-3</sup> |  |  |

| Channel Doping                             | $N_i$            | $1x10^{17}$ | cm <sup>-3</sup> |  |  |

| Drain Voltage                              | $V_{dd}$         | 0.1         | V                |  |  |

#### III. RESULTS AND DISCUSSION

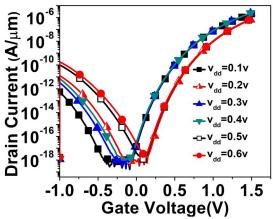

Figure 2. Transfer characteristics curves of the LG SOI TFET with different Drain Voltage  $(V_{dd})$

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177

Volume 7 Issue VII, July 2019- Available at www.ijraset.com

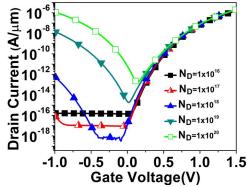

Figure 3. Transfer characteristics curves of the LG SOI TFET with different Drain Concentrations (N<sub>D</sub>) at V<sub>dd</sub>=0.1v

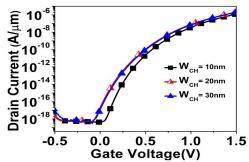

Figure 4. Transfer characteristics curves of the LG SOI TFET with different Channel Width ( $W_{CH}$ ) at  $V_{dd}$ =0.1v

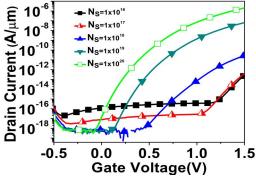

Figure 5. Transfer characteristics curves of the LG SOI TFET with different Source Concentrations ( $N_S$ ) at  $V_{dd}$ =0.1v

Figure 6. Schematic Diagram Of the LG SOI TFET

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue VII, July 2019- Available at www.ijraset.com

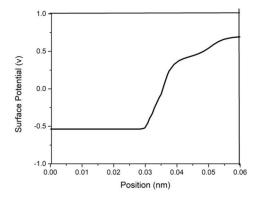

Figure 7. Surface Potential On Cut Line (C1) at Gate Voltage V<sub>g</sub>= 1.5v

The transfer characteristic curves of the LG SOI TFET with the different Drain Voltage ( $V_{dd}$ ) are shown in the Figure 2. It can be clearly observed from Figure 2 that OFF State leakage current ( $I_{OFF}$ ) is lowest and ON state current ( $I_{ON}$ ) is highest at Drain Voltage 0.1v which means this device is suitable fow Low Power Applications. In Figure 3, the transfer characteristics curves with the different Drain Concentrations ( $N_d$ ) and where we can easily analyze that on increasing the N-type doping in the drain region, the OFF State Leakage current is increasing.

TABLE 2

Drain Doping Variation

| Bruin Boping variation |                        |                         |                        |  |  |  |

|------------------------|------------------------|-------------------------|------------------------|--|--|--|

| DRAIN                  | I <sub>ON</sub> (A/µm) | I <sub>ON</sub> (A/µm)  | $I_{ON}/I_{OFF}$       |  |  |  |

| DOPING                 |                        |                         |                        |  |  |  |

| $(N_d)$                |                        |                         |                        |  |  |  |

| $1x10^{16}$            | 1.425x10 <sup>-6</sup> | 1.40x10 <sup>-16</sup>  | 1.018x10 <sup>10</sup> |  |  |  |

| $1x10^{17}$            | 1.878x10 <sup>-6</sup> | 1.166x10 <sup>-17</sup> | $1.60 \times 10^{11}$  |  |  |  |

| $1x10^{18}$            | 2.035x10 <sup>-6</sup> | 1.307x10 <sup>-17</sup> | 1.557x10 <sup>11</sup> |  |  |  |

| $1x10^{19}$            | 2.012x10 <sup>-6</sup> | 2.190x10 <sup>-15</sup> | 9.412x10 <sup>8</sup>  |  |  |  |

| $1x10^{20}$            | 2.077x10 <sup>-6</sup> | 6.446x10 <sup>-12</sup> | $3.22 \times 10^5$     |  |  |  |

TABLE 3 Channel Width Variation

| CHANEL | $I_{ON}$               | $I_{\mathrm{OFF}}$      | $I_{ON}/I_{OFF}$       |

|--------|------------------------|-------------------------|------------------------|

| WIDTH  | (A/µm)                 | (A/µm)                  |                        |

| 10nm   | 3.275x10 <sup>-6</sup> | 2.201x10 <sup>-15</sup> | 1.482x10 <sup>9</sup>  |

| 20nm   | 2.046x10 <sup>-6</sup> | 1.950x10 <sup>-17</sup> | 1.049x10 <sup>11</sup> |

| 30nm   | 2.035x10 <sup>-6</sup> | 1.307x10 <sup>-17</sup> | 1.557x10 <sup>11</sup> |

In Figure 5, the transfer characteristics curves with the different Drain Concentrations ( $N_d$ ) and resulting in the ON State Current increases with the P-type doping in the source reason. In Figure 6, this is the schematic diagram of the proposed device to just show the cut line (C1) at which the surface potential is to be calculated, although there is the two cut lines in the proposed device but here we have calculated surface potential with respect to only one cut line. In Figure 7, there is the graph between the positions and the surface potential at that particular position and it shows that the surface potential is reached the max at where front-gate ending point exists [14]. Then, the surface potential reduced due to the absence of a front gate, then gradually increased towards the drain side in region V. or we can say that surface potential is high at the channel junction region as well. After all the analysis we conclude that the proposed device is suitable for low power applications and it enables the high ON State Current and the OFF State Leakage Current has also reduced.  $I_{ON} = 2.035 \times 10^{-6} \,\text{A}/\mu\text{m}$ ,  $I_{OFF} = 1.307 \times 10^{-17} \,\text{A}/\mu\text{m}$ ,  $I_{ON}/I_{OFF} = 1.557 \times 10^{-11}$ .

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue VII, July 2019- Available at www.ijraset.com

#### IV. CONCLUSION

In this paper, LG SOI TFET was studied. The proposed device is demonstrated to achieve a significantly improved performance as compared with a planar TFET, in terms of  $I_{ON}$  on-off current ratio and subthreshold swing. The tunneling junction is perpendicular to the channel direction that facilitates the implementation of a relatively large tunneling junction area[15]. Low drain doping and high source doping is resulting in high  $I_{ON}$  and low  $I_{OFF}$ .

#### REFERENCES

- [1] Frank, D.J., Dennard, R.H., Nowak, E., Solomon, P.M., Taur, Y., Wong, H.S.P.: Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE 89(3), 259–288 (2001). https://doi.org/10.1109/5.915374

- [2] Ionescu, A.M., Riel, H.: Tunnel field-effect transistors as energy efficient electronic switches. Nature 479(7373), 329–337 (2011). https://doi.org/10.1038/nature10679

- [3] Choi, W.Y., Park, B.-G., Lee, J.D., Liu, T.-J.K.: Tunneling fieldeffect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Dev. Lett. 28(8), 743–745 (2007). https://doi.org/10.1109/LED.2007.901273

- [4] Avci, U.E., Morris, D.H., Young, I.A.: Tunnel field-effect transistors: prospects and challenges.IEEEJ.ElectronDev.Soc.3(3),88–95(2015). https://doi.org/10.1109/JEDS.2015.2390591

- [5] Sang Wan Kim, Woo Young Choi, Min-Chul Sun and Byung-Gook Park, "Investigation on the Corner Effect of L-Shaped Tunneling Field-Effect Transistor and Their Fabrication Method" J. Nanosci. Nanotechnol., vol. 13, no. 9, pp. 6376–6381, Sep. 2013.

- [6] Sang Wan Kim, Woo Young Choi, Min-Chul Sun and Byung- Gook Park, "Investigation on hump effects of L-shaped Tunnel Field Effect Transistor".

- [7] Sang Wan Kim1, Woo Young Choi2, Min-Chul Sun1, 3, Hyun Woo Kim1, and Byung-Gook Park1," Design Improvement of L-shaped Tunneling Field-Effect Transistors".

- [8] Zhaonian Yang "Tunnel Field Effect Transistor with an L shaped Gate". IEEE Electron Device Letters, vol.37, no.7, july 2016.

- [9] Peng Xu and Xinnan Lin\*," Current Enhanced PNPN Tunnel Field-Effect Transistor With L-Shaped Gate" The Shenzhen Key Lab of Advanced Electron Device and Integration, ECE, Peking University, Shenzhen Graduate School.

- [10] R.Gowri Manohari, Dr.K.K.Nagaraja, Dr.R.Srinivasan, "Single Event Transient analysis of Conventional planar tunnel FET, Planar tunnel FET with pocket and L shaped tunnel FET" International Conference on Nextgen Electronic Technologies, 2017.

- [11] W. Reddick and G. Amaratunga, "Silicon surface tunnel transistor," Appl. Phys. Lett., vol. 67, no. 4, pp. 494–496, Jul. 1995.

- [12] Q. Zhang, W. Shao, and A. Seabaugh, "Low-subthreshold-swing tunnel transistors," IEEE Electron Device Lett., vol. 27, no. 4, pp. 297–300, Apr. 2006..

- [13] W. G. Vandenberghe, A. S. Verhulst, G. Groeseneken, B. Soree, and W. Magnus, "Analytical model for point and line tunneling in a tunnel field-effect transistor," in Proc. SISPAD, Sep. 2008, pp. 137–140.

- [14] Sentaurus User's Manual, Synopsys.

- [15] Mitra, S.K., Goswami, R., Bhowmick, B.: A hetero-dielectric stackgate SOI-TFET with back gate and its application as a digital inverter. Super lattice Microstruct. 92, 37–51 (2016). https://doi.org/10.1016/j.spmi.2016.01.040

- [16] Vandenberghe, W., Verhulst, A.S., Groeseneken, G., Soree, B., Magnus, W, "Analytical model for point and line tunneling in a tunnel field-effect transistor". In: Proc. Int. Conf. SISPAD, pp. 137–140(2008). https://doi.org/10.1109/sispad.2008.4648256

1031

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)