# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 8 Issue: V Month of publication: May 2020

DOI: http://doi.org/10.22214/ijraset.2020.5030

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 8 Issue V May 2020- Available at www.ijraset.com

### ASIC Implementation of Serial Commutator Fast Fourier Transform for Real Valued Signal

Viraj Bhusari

Department of Micro and Nano-electronics, VIT University, Vellore, Tamilnadu, India-632014

Abstract: This paper presents serial pipelined Fast Fourier Transform hardware architecture for real valued signal. The SC-RFFT uses bit exchange circuitry for serial data at intermediate stages. The observation made from proposed architecture is that, in radix 2 FFT algorithm one fourth of the samples are rotated at first stage and remaining stages requires half rotators. For real valued input signals numbers of butterflies are reduced, hence clock pulses. As a result the proposed architecture has less hardware requirement compared with serial commutator for conventional FFT.

Keywords: RFFT, Serial Commutator, Bit-Exchange, ASIC implementation, Pipelining

#### I. INTRODUCTION

As VLSI technology is growing day-by-day, DSP and communication system devices also demands high speed computation and minimum hardware requirement.

DFT and FFT are widely used and important area of DSP. Frequency domain analysis of signal provides information which is difficult to analyse signal in time domain. So, different transform techniques can be used to analyse signal in frequency domain. So, DFT is one of the popular technique. FFT is an efficient algorithm to implement DFT. FFT removes redundant calculations and reduces the arithmetic units, so it is much faster.

There are many techniques have been proposed to increase the speed of FFT algorithm in last few years. The arithmetic complexity and its recursive structure decide the performance of FFT structure.

The various architectures are already available for computation of FFT. But pipelined architectures are more popular and suitable to process high speed data.

The conventional architectures of FFT use dedicated RAM to perform butterfly operations. In contrast, the pipelined architectures directly begin FFT computation instead of storing input in dedicated RAM.

Mainly, there are two types of Pipelined FFT's. First one is serial pipelined FFT process, which computes one sample per clock cycle. And second type is parallel pipelined FFT process which computes several samples in parallel per clock cycle.

Over the period the development happened widely in Parallel pipelined FFT architecture. The multipath delay commutator reduces the number of required amount of butterflies, memory and rotators. In contrast, the efficient development in serial pipelined architecture is not reached up to mark of parallel ones yet. In serial pipeline, the single-delay commutator (SDC) FFTs improves the use of butterflies and rotators but it takes larger memory.

Therefore, in every case, there is trade-off among butterflies, rotators and memory. Above mentioned both type of pipelined FFT architectures can compute both real and complex signals. But, most of signals which receive from outside world are real-valued. So, complex FFT processors are not efficient to compute real-valued signals.

So, customized real-valued FFT (RFFT) signal is required, which increases hardware efficiency over complex FFT processors. In N-Point DFT, X[k] is representation of x[n], and if x[n] is real valued then by Hermitian symmetry property, X[N-k] = X[k] implies, out of N outputs of FFT algorithm N/2 -1 are conjugate symmetry. So, these conjugate symmetry points become redundant and are not necessary to compute it. For 16-point radix-2 FFT, then half of the butterfly and multiplication terms become redundant if this property applied to Data flow graph (DFG). Moreover, many real-time applications such as video, audio, image, mobile applications and biomedical applications require RFFT.

So, operation on real valued signal is done by either parallel pipelined or by serial pipelined architectures. The architecture for the parallel pipelined FFT processors for real valued signal is proposed [2]. This paper presents the Serial commutator for real valued FFT (SC-RFFT).

This SC-RFFT uses bit-exchange circuit for data management of serial data at intermediate stages. This architecture requires less number of registers, rotators and butterflies. The sections organised as follows. Section II gives explanation of proposed architecture for SC-RFFT. Section III compares the computation complexity using proposed architecture.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 8 Issue V May 2020- Available at www.ijraset.com

#### II. PROPOSED ARCHITECTURE

In N point DFT, with Radix-2 base N=log<sub>2</sub>N stages are required. In this paper, the proposed model if for N=16 points. So, n=4 stages are required. Here, all 16 point inputs are received first atage of serial commutator are real.

| STAG | E 1                            | STAGE | E 2                | STAGE | 3     | STAGE 4     | k              |

|------|--------------------------------|-------|--------------------|-------|-------|-------------|----------------|

| 0    | 0                              | 0     | 0                  | 0     | 0     | 0 0 -       | <b>→</b> 0     |

| 8    | 8 Wº                           | 4     | 0 4                | 2     | 2 Wº  | 1 2 1 -     | - 8            |

| 2    | 2                              | / 2   | 2                  | < 4   | 4 W0  | /4 4 -      | <b>→</b> 2     |

| 10   | 10 wº X                        | 6     | ⊚ 6 W <sup>4</sup> | 6     | 6 \   | 5 5 -       | <b>→</b> 10    |

| 4    | 4×                             | ×8    | 8 W <sup>0</sup>   | 8     | 8     | / /8 8 -    | <b>→</b> 1     |

| 12   | ∞ 12 W <sup>4</sup>            | 12    | ∞ 12               | 10    | 10 we | ( / 9 ) 9 - | - 9            |

| 6    | 6                              | 10    | 10 W2              | 12    | 12    | X /12 12 -  | <b>→</b> 3     |

| 14   | ⊚ 14 W <sup>4</sup>            | 14    | ∞ 14               | 14    | 14 X  | 13 -        | <b>→</b> 11    |

| 1    | 1                              | 1     | 1                  | 1     | 1/ X  | / 2 2 -     | <b>→</b> 4     |

| 9    | 9 Wº                           | 5     | <sub>∞</sub> 5     | 3     | 3 w.  | 3 3 -       | <b>→</b> 12    |

| 3    | 3                              | 3     | 3                  | < 5 l | 5 w2/ | 6 -         | <b>→</b> 6     |

| 11   | ∞ 11 wº X                      | 7 🔀   | ∞ 7W <sup>4</sup>  | 7     | 7 / / | 7 7 7 -     | - 14           |

| 5    | 5                              | ×9 ,  | 9 W1               | 9     | 9//   | 10 -        | <b>→</b> 5     |

| 13   | ∞ 13 W <sup>4</sup> ×          | 13    | <u>∞</u> 13        | 11    | 11w4  | 11 11 -     | <b>→</b> 13    |

| 7    | 7/                             | 11    | 11W3               | 13    | 13/   | 14 14 -     | <b>→</b> 7     |

| 15   | <sub>∞</sub> 15 W <sup>4</sup> | 15    | <sub>∞</sub> 15    | 15    | 15    | 1515 -      | <del></del> 15 |

| 1    |                                | 1     | 1                  |       | 1     |             |                |

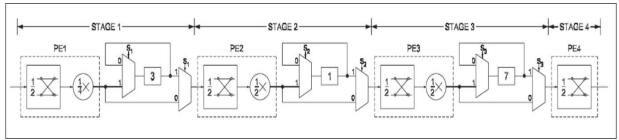

Fig1. Data Flow Graph of radix-2 SC-RFFT

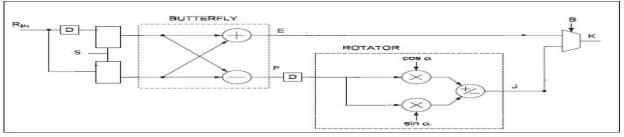

So, any radix-2 FFT architecture which computes one sample per clock cycle only needs one adder and half a rotator per stage. This leads to  $log_2N$  butterflies and  $(log_4N-1)$  rotators to implement complete FFT. The butterfly structure used here has only real adder and real subtracter instead of complex ones, the rotators is made up of two multipliers and one adder instead of four real multipliers and two adders. Fig 2. shows the proposed architecture for serial computation of 16 point radix-2 SC-RFFT. The Processing Element (PE) used to calculate butterflies and rotations.

Fig2. Proposed Architecture of 16 point radix 2 SC-RFFT

#### 1) PE1: Processing element for 1<sup>st</sup> stage is shown in Fig.3

Fig3. Processing Element used at Stage 1

For real valued signal Outputs are First stage don't have real plus imaginary terms, hence one real adder and real subtractor required. Control element is used to select input using select line. Rotator requires only 1 rotation per 4 clock cycles hence quarter rotator used.  $Y_0 = I_0 + I_8$ ,  $Y_8 = (I_0 - I_8)e^{-j\alpha}$ . Inputs are in consecutive clock cycles,  $Y_0$  and  $Y_8$  are obtained in consecutive clock cycles.

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 8 Issue V May 2020- Available at www.ijraset.com

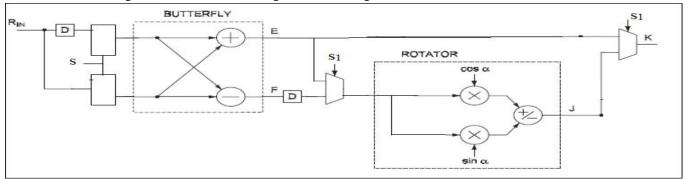

2) PE2, PE3: Processing element for 2<sup>nd</sup> and 3<sup>rd</sup> stage is shown in Fig. 4

Fig4. Processing Element used at stage 2 and stage 3

In 2<sup>nd</sup> and 3<sup>rd</sup> stage mux is used to control input to rotator. In the last stage processing element does not require any rotator.

Table 1: Timing diagram of PE stage 1

| T | In    | S | Е                 | F             | K     |

|---|-------|---|-------------------|---------------|-------|

| 0 | $I_0$ | 0 |                   |               |       |

| 1 | $I_8$ | 1 | $Y_0 = I_0 + I_8$ |               | $Y_0$ |

| 2 |       | 0 |                   | $Y_0=I_0-I_8$ | $Y_8$ |

Table 2: Timing diagram of PE stage 2

|   |                | υ | 0 0               |                      |       |

|---|----------------|---|-------------------|----------------------|-------|

| T | In             | S | Е                 | F                    | K     |

| 4 | $\mathbf{Y}_0$ | 0 |                   |                      |       |

| 5 | $Y_8$          | 1 | $Z_0 = Y_0 + Y_4$ |                      | $Z_0$ |

| 6 |                | 0 |                   | $Z_4 = Y_0 - Y_{\$}$ | $Z_4$ |

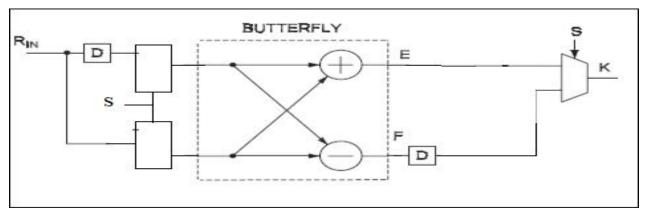

#### 3) PE4: Processing element for 4<sup>th</sup> stage is shown in Fig.5

Fig5. Processing Element used at stage 4

#### A. Bit Exchange Element

Outputs of processing should be re-arranged before given as inputs to next processing element. Samples to be operated together must come in consecutive clock cycles: hence Bit-exchange circuit is required. Inputs required to be delayed by different amount for different stages, This circuit can be used for DIF as well as DIT.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 8 Issue V May 2020- Available at www.ijraset.com

#### III.COMPARISON AND ANALYSIS

Table 3 and Table 4 give comparison for pipelined FFT architectures for serial data. Table 3 does not focuses on any specific order for I/O, whereas next table gives comparison for natural inputs and outputs. In Table 3, first table denotes the type of architecture, and numbers of rotators, adders used in architecture are showed in second, third column, and latency and throughput is compared in last two columns. Since all architecture process serial data, throughput can be calculated by one sample/clock cycle.

Table 3 compares different parameters for natural inputs and outputs. Proposed architecture reduces the number of delay registers by 50%.

Table 3: Comparison for pipelined architecture for N-point FFT for serial data

| Pipelined Architecture | Complex Rotators        | Complex Adders        | Latency (cycles) | Throughput |

|------------------------|-------------------------|-----------------------|------------------|------------|

| SDF Radix-2, [2]       | 2(log <sub>4</sub> N-1) | 4(log <sub>4</sub> N) | N                | 1          |

| SDF Radix-2, [9]       | log <sub>4</sub> N-1    | 2(log <sub>4</sub> N) | 4N/3             | 1          |

| SDF Radix-4, [3]       | log <sub>4</sub> N-1    | 8(log <sub>4</sub> N) | N                | 1          |

| SDF Radix-4, [2]       | log <sub>4</sub> N-1    | 4(log <sub>4</sub> N) | N                | 1          |

| SDF Split-radix, [13]  | $log_4N-1$              | 4(log <sub>4</sub> N) | N                | 1          |

| SDF Radix-4, [14]      | log <sub>4</sub> N-1    | 3(log <sub>4</sub> N) | 2N               | 1          |

| SDC-SDF Radix-2, [8]   | log <sub>4</sub> N-1    | 2(log <sub>4</sub> N) | 3N/2             | 1          |

| Proposed SC-RFFT       | log <sub>4</sub> N-1    | 2(log <sub>4</sub> N) | N                | 1          |

Table 4: Comparison for pipelined architecture for N-point FFT for natural inputs and outputs

| Pipelined Architecture | Complex Rotators        | Complex Adders | Latency (cycles) | Throughput |

|------------------------|-------------------------|----------------|------------------|------------|

| SDC Radix-2, [6]       | 2(log <sub>4</sub> N-1) | $2(\log_4 N)$  | 2N               | 1          |

| SDC Radix-2, [5]       | 2(log <sub>4</sub> N-1) | $2(\log_4 N)$  | 2N               | 1          |

| Proposed SC-RFFT       | log <sub>4</sub> N-1    | $2(\log_4 N)$  | N                | 1          |

| Radix-2, even N        |                         |                |                  |            |

| Proposed SC-RFFT       | log <sub>4</sub> N-1    | $2(\log_4 N)$  | N                | 1          |

| Radix-2, odd N         |                         |                |                  |            |

#### IV.RESULTS

SC-RFFT for n=1024 points and word length as 16 bits is implemented on ASIC technology using UMH 90-nm technology. Various parameters for former architectures are compared in Table 5. In proposed architecture clock frequency and area are improved with compared to other architectures.

For s<sup>th</sup> stage, number of delay registers required given as  $(2^{n-s-1}-2^0)$ . For  $1^{st}$  stage required delay registers are  $(2^{4-1-1}-2^0)=3$ . For  $2^{nd}$  stage, required delay registers are  $(2^{4-2-1}-2^0)=1$ . For last stage, required delay registers are  $(2^{4-1}-2^0)=7$ . Thus for 16-bit RFFT 11 delay registers are required. And also, number of delay registers for N-bit is given as: (Number of bits- Number of stages-1).

Table 5: Comparison of serial FFT after implementing on ASIC

| Parameter        | Proposed Architecture | [15]    | [16] | [17]   |

|------------------|-----------------------|---------|------|--------|

| FFT Size         | 1024                  | 64      | 2048 | 256    |

| Radix            | 2                     | $2^{3}$ | 24   | 24     |

| Architecture     | SC-RFFT               | SDC     | SDF  | SDF    |

| Word length      | 16                    | 16      | 10   | =      |

| Technology (nm)  | 90                    | =       | 180  | 180    |

| Voltage (V)      | 0.9                   | =       | 2.7  | 1.8    |

| Clk (MHz)        | 200                   | 166     | 76   | 51.5   |

| Area (mm²)       | 0.15                  | 0.47    | 7.58 | =      |

| Gate Count       | 134066                | =       | -    | 173875 |

| SQNR (dB)        | 55                    | -       | 45.3 | -      |

| Power (mW)       | 8.0                   | 29.7    | 526  | -      |

| Norm. Power (mW) | 8.0                   | -       | 9.18 | -      |

179

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 8 Issue V May 2020- Available at www.ijraset.com

#### V. CONCLUSIONS

This paper presents novel architecture for the 16-point radix-2 serial commutator for real valued fast fourier transform (SC-RFFT) architecture. This bit exchange circuit for data management at intermediate stages. Compared to previous designs [1], SC-RFFT reduces execution time for computation of real valued input signal FFT. Finally proposed architecture is implemented on ASIC technology for 90nm technology and experimental results are obtained which clearly shows that proposed architecture has small area and consumes low power with compared to previous architectures.

#### REFERENCES

- [1] M. Garrido, J. Grajal, M. A. Sánchez, and O. Gustafsson, "Pipelined radix-2k feedforward FFT architectures," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 21, no. 1, pp. 23–32, Jan. 2013.

- [2] S. He and M. Torkelson, "Design and implementation of a 1024-point pipeline FFT processor," in Proc. IEEE Custom Integr. Circuits Conf., May 1998, pp. 131–134.

- [3] A. M. Despain, "Fourier transform computers using CORDIC iterations," IEEE Trans. Comput., vol. C-23, no. 10, pp. 993-1001, Oct. 1974.

- [4] M. Sánchez, M. Garrido, M. López, and J. Grajal, "Implementing FFT-based digital channelized receivers on FPGA platforms," IEEE Trans. Aerosp. Electron. Syst., vol. 44, no. 4, pp. 1567–1585, Oct. 2008.

- [5] X. Liu, F. Yu, and Z. Wang, "A pipelined architecture for normal I/O order FFT," J. Zhejiang Univ., Sci. C, vol. 12, no. 1, pp. 76–82, Jan. 2011.

- [6] Y.-N. Chang, "An efficient VLSI architecture for normal I/O order pipeline FFT design," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 55, no. 12, pp. 1234–1238, Dec. 2008.

- [7] Z. Wang, X. Liu, B. He, and F. Yu, "A combined SDC-SDF architecture for normal I/O pipelined radix-2 FFT," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 23, no. 5, pp. 973–977, May 2015.

- [8] W.-C. Yeh and C.-W. Jen, "High-speed and low-power split-radix FFT," IEEE Trans. Signal Process., vol. 51, no. 3, pp. 864–874, Mar. 2003.

- [9] G. Bi and E. Jones, "A pipelined FFT processor for world-sequential data," IEEE Trans. Acoust., Speech Signal Process., vol. 37, no. 12, pp. 1982–1985, Dec. 1989

- [10] T. Adiono, M. S. Irsyadi, Y. S. Hidayat, and A. Irawan, "64-point fast efficient FFT architecture using radix-23 single path delay feedback," in Proc. Int. Conf. Elect. Eng. Informat., Aug. 2009, vol. 2, pp. 654–658.

- [11] T. Lenart and V. Öwall, "Architectures for dynamic data scaling in 2/4/8 K pipeline FFT cores," IEEE Trans. Very vol. 14, no. 11, pp. 1286–1290, Nov. 2006.

- [12] C.-P. Fan, M.-S. Lee, and G.-A. Su, "A low multiplier and multiplication costs 256-point FFT implementation with simplified radix-24 SDF architecture," in Proc. IEEE Asia-Pacific Conf. Circuits Syst., Dec. 2006, pp. 1935–1938.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)