IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 8 Issue: VI Month of publication: June 2020

DOI: http://doi.org/10.22214/ijraset.2020.6369

### www.ijraset.com

Call: 🕥 08813907089 🔰 E-mail ID: ijraset@gmail.com

## Architecture Design and FPGA Code Development for ADC Module

Akash Ajayakumar<sup>1</sup>, Maruti Zalte<sup>2</sup>

<sup>1</sup>M.Tech Student, <sup>2</sup>Asst. Prof., Department of Electronics and Telecommunication Engineering, K.J.Somaiya College of Engineering

Abstract: High resolution ADCs play a vital role in designing a system for high end applications where the need for accuracy and preciseness plays a very important factor. In this work, we designed a system where this module will receive the temperature signal; the range of temperature signal varies from 0.0V to 10V dc. We write the necessary HDL code for the FPGA block for this module to read, write, sample and generate the timer pulse from the temperature signal received. In order to achieve a system with higher accuracy, the process of computation and updating of data is done every second. As the system calls for precise measurement it is required to have an ADC of 24-bits. We have written the necessary code and generated the output which shows the data being written on an ADC and after accepting the data how it is read in an ADC and the sampling is performed on the data which is read. In order to achieve the operation under a controlled environment the code for the timer pulse is generated.

Keywords: FPGA, RTL Structure, ADCs, HDL

#### I. INTRODUCTION

Field Programmable Gate Arrays (FPGAs) are silicon devices which are pre-fabricated and are programmed electrically to become any kind of digital circuit [1]. They have numerous advantages over a fixed function Application Specific Integrated Circuit (ASIC) technologies. ASCIs take a lot of time for fabrication and cost a lot of money for its fabrication, whereas FPGAs can be configured at a much faster rate and if any mistake occurs, it could be reconfigured back easily hence it is cost efficient compared to ASCIs. Thus this flexibility of an FPGA comes with a significant cost in area, power consumption and the delay. These disadvantages are caused from FPGA's programmable routing fabric which trades power, area and speed for quick fabrication. Even having such disadvantage, FPGA acts as an alternative for digital system implementation based on their low cost and fast turnaround [1]-[3]. As provided in the Moore's law the access to performance and scaling is given by FPGAs. With the progress of Moore's law, difficulties occurred due to the submicron processes making the design for ASIC very expensive and difficult. Because of such higher expense and a higher return on amount invested drives digital design toward FPGA implementation. A user must employ computer aided design (CAD) tools for FPGA designs. Due to the vast growth in the VLSI technology, it is possible for a design to design a single chip with more than 100000 transistors. As a result of huge amount of transistors on a single chip, the design complexity increases hence, to verify these circuits on a breadboard was not possible. Hence for design and verification of VLSI digital circuits, computer aided techniques plays a very vital role. Programs to do automatic routing and placement of circuit layouts became very popular.

The designers felt a need to standardize a language for describing digital circuits. Thus Hardware Descriptive Languages (HDL) came into existence. To model the concurrency of processes found in hardware elements was made possible by the HDLs to the designers. A hardware description language (HDL) could be defined as language which is specifically written for describing the behavior and structure of electronic circuit. A hardware description language is written for a precise and correct simulation and analysis of an electronic circuit. One important difference between most programming languages and HDLs is that HDLs explicitly include the notion of time [4]. Especially when it comes to complex circuits, HDL plays an integral part for electronic design automation (EDA) systems such as application-specific integrated circuit, programmable logic devices and microprocessors [5].

The module which we developed would receive the temperature signal as an input to the system. The range of temperature signal is from 0.0v to 10V. The module has to compute the process of writing, reading, sampling from the temperature signal received.

In order to achieve a very high accuracy the process of computation and updating of signal is done in every second, it is required to have an ADC of 22 bits or more for such purpose. The analog signal is passed via an ADC which converts an analog signal to a digital signal which is connected to a FPGA block where the necessary HDL codes are written to perform necessary operations, which is followed by a DAC which converts the processed signal to corresponding analog signal.

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 8 Issue VI June 2020- Available at www.ijraset.com

#### II. FUNCTIONAL REQUIREMENTS OF FPGA

- A. FPGA should sample the ADC data and computation must be performed continuously

- *B.* After every computation, FPGA should generate ADC convert signals initiating ADC to acquire data. ADC asserts a busy signal and FPGA should wait till the busy signal is de asserted by ADC. FPGA should initiate a read operation and complete the reading of ADC value.

- *C.* The ADC read is to be done 24 consecutive times to acquire data from ADC to take the average sample values (24samples) if required for future computation. The reading of 24 data samples will be repeated continuously after specific time interval to get the new sample value of ADC data.

#### **III.ARCHITECTURE OF RTL DESIGNFOR FPGA**

The design is to be implemented using Verilog HDL as hardware design language. The main functional blocks to be implemented in FPGA are basic timer block, ADC read, ADC write and sampling blocks.

Fig. 1 RTL Design for FPGA

Fig. 1 shows the RTL design, these are the blocks for which the necessary codes would be written for executing the necessary operation. Each block signifies a specific function corresponding from the data read, data write, data sampling by an ADC.

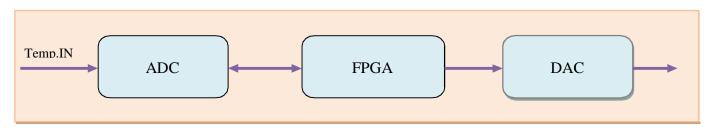

#### **IV.SYSTEM BLOCK DIAGRAM**

Fig. 2 Block Diagram for the System

Fig. 2 represents the block diagram for a system which consists of several hardware equipments namely being the ADC which converts the analog signal into necessary digital signal which are processed in a FPGA which is programmed to perform necessary functions. The processed digital signal from a FPGA is passed through a DAC which convert these digital signals to corresponding analog signal and is passed through for further operations. The input to an ADC is temperature signal which ranges from 0.0v to 10v dc. The output processed from the FPGA could be altered accordingly to the requirements mainly for high end applications which require for precise and accurate calculations of the signals.

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 8 Issue VI June 2020- Available at www.ijraset.com

#### V. RESULTS AND DISCUSSIONS

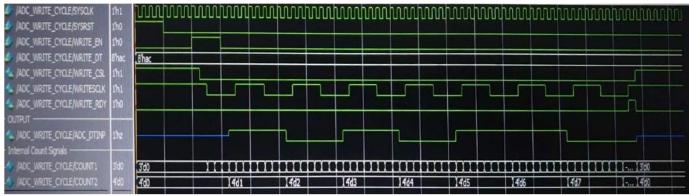

Fig. 3 Result for ADC Write Cycle

The system remains in an ideal state when the reset signal has a value 1. For the system to operate the reset signal should be set to a value 0. The input is a 8 bit signal having value "ac" which corresponds to an equivalent binary value of "1010 1100". The system starts its operation as soon as an enable signal is triggered which is represented by "WRITE\_EN" signal. As soon as the enable signal is triggered the operation begins and the output can be observed respectively "ADC\_DTINP" signal respectively. As soon as the operation is completed a ready signal represented by "WRITE\_RDY" is set to 1 indicating operation is completed .

|                          | M         | ф<br>       |      |      |         | -    | haar           |       | haar   | haa      | hoor  | hoo   | nhnnr  | honi  | hoor  | nnnn  | nnnn   | hnni  | nnnn  | hhnnt | hr |

|--------------------------|-----------|-------------|------|------|---------|------|----------------|-------|--------|----------|-------|-------|--------|-------|-------|-------|--------|-------|-------|-------|----|

| 5 /ADC_READ_CYCLE/SYSCLK | 1ħ1       | mm          | տոող | nnnh | UUUL    |      |                | LUUU  | uuuu   | 4000     | 4000  | 4000  | 4000   | 40.00 | 4000  | 4000  | 0000   | 1000  | 1000  |       |    |

| ADC_READ_CYCLE/SYSRST    | 1110      |             |      |      |         |      |                | -     |        |          |       |       | -      |       |       |       |        |       |       |       |    |

| ADC_READ_CYCLE,READ_ENS  | 1110      |             |      |      |         |      | _              | -     | -      |          | =     | =     | -      | -     | -     | -     | -      |       |       |       |    |

| ADC_READ_CYCLE/ADC_DOUT  | 1h1       |             |      |      |         |      |                |       |        |          |       |       |        |       |       |       |        |       |       | -     |    |

| ADC_READ_CYCLE/READ_CSEL |           |             |      |      | _       | _    | -              |       |        | <u> </u> |       |       |        | 5     |       | 5     |        | 5     |       |       |    |

| ADC_READ_CYCLE/READ_SCLK |           |             |      | Ļ    |         |      |                |       |        |          | +     |       |        | L-    | +     |       |        |       | t h   |       |    |

| ADC_READ_CYCLE/READ_RDY1 | 1110      |             |      |      |         |      |                |       | _      |          |       |       |        |       |       |       |        |       |       |       |    |

| DUTPUT                   | 851111111 | (8500000000 |      |      | 1851000 | 0000 | <b>185</b> 110 | 00000 | [8b11] | 00000    | 18511 | 10000 | (8b11) | 11000 | [8b11 | 11100 | 185111 | 11110 | [8511 | 11111 |    |

| nternal Count Signals    |           |             |      |      |         |      |                |       |        |          |       |       |        |       |       |       |        |       |       |       |    |

| ADC_READ_CYOLE/COUNT1    | 36000     | 35000       |      | m    | m       | III  | m              | m     |        | m        |       |       |        |       |       |       |        |       | 3     | 6000  |    |

| INDC_REND_CYCLE/COUNT2   | 450000    | 460000      |      |      | 450001  |      | (4b001         | 0     | 146001 | 1        | 46010 | 0     | 46010  | 1     | 4601  | 0     | 46011  | 1     |       | 60000 |    |

Fig. 4 Result for ADC Read Cycle

Fig.4 represents the result for the ADC read cycle, the system is under an ideal state when the reset is set to 1. The operation starts when the reset to 0 and an enable signal represented by "READ\_ENB" is triggered. "ADC\_DOUT" is set to 1 and we can observe the output represented by "DATA\_8BIT" starting from an initial value which was "000000000" under ideal condition to "11111111" at the end of execution. After the execution is completed a ready signal represented by "READ\_RDY1" triggers to 1.

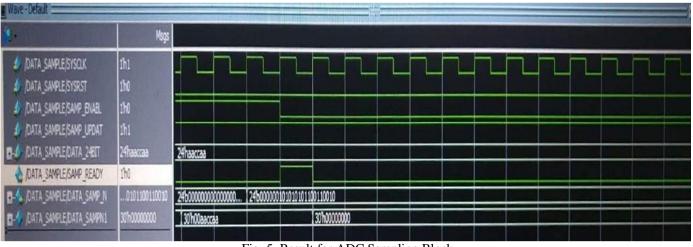

Fig. 5 Result for ADC Sampling Block

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 8 Issue VI June 2020- Available at www.ijraset.com

Fig. 6 Result for Timer Pulse Generation

Fig. 6 shows the generation of a timer pulse signal which is a 10ms pulse generated from a 10MHz input signal. It is done for the controlled operation of the system.

#### VI. CONCLUSION

We have designed a system and written necessary HDL code for an FPGA block for the ADC operations namely being ADC read, ADC write, ADC sampling. The timing pulse has been generated in order for a system to operate under a controlled environment. The results obtained are represented using pulses and the obtained results are checked and verified. This ADC operation plays a vital role when it comes for high end applications where the results to be obtained must be highly accurate and precise.

#### REFERENCE

- [1] Kuon, Ian, Russell Tessier, and Jonathan Rose. FPGA architecture: Survey and challenges. Now Publishers Inc, 2008.

- [2] Trimberger, Stephen M., ed. Field-programmable gate array technology. Springer Science & Business Media, 2012.

- [3] Calhoun, Benton Highsmith, Joseph F. Ryan, Sudhanshu Khanna, Mateja Putic, and John Lach. "Flexible circuits and architectures for ultralow power." Proceedings of the IEEE 98, no. 2 (2010): 267-282.

- [4] Gupta, Rajesh K., and Stan Y. Liao. "Using a programming language for digital system design." IEEE Design & Test of Computers 14, no. 2 (1997): 72-80.

- [5] Dubey, Rahul, Pramod Agarwal, and M. K. Vasantha. "Programmable logic devices for motion control—A review." IEEE Transactions on Industrial Electronics 54, no. 1 (2007): 559-566.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)