## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 9 Issue: I Month of publication: January 2021

DOI: https://doi.org/10.22214/ijraset.2021.32893

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 9 Issue I Jan 2021- Available at www.ijraset.com

# Two Phase Sample and Low Power Hold Circuit Design and Simulation using Current Regulated AB Class Topology Conveyor

Vasu Sharma<sup>1</sup>, Prof. D. S Ajnar<sup>2</sup>, Prof. P. K Jain<sup>3</sup>

<sup>1</sup>M.tech Student, Department of Information Technology, Shri G.S. Institute of Technology and Science, RGPV

<sup>2</sup>Professor, Shri G.S. Institute of Technology and Science, RGPV

<sup>3</sup>Professor, Shri G.S. Institute of Technology and Science, RGPV

Abstract: The current operated conveyor is the two-stage sample and hold-circuit, with two individual sample- and hold-circuit attached in the initial step in cascading topography. In the final step, the final output from the original sample and hold circuit will be corrected and the topology current conveyor AB is worked like a switch. The sample and holding circuit phases are all aligned and operated with low energy consumption at the same distortion current. More reliable results with exceptionally high linearity and flatter output waveform during hold time have the features of the proposed circuit. The suggested sample and keeping circuit was simulated with 0.18  $\mu$ m metal oxide complement (CMOS). The greatest interest is the simulation of a circuit analog transition.

Keywords: Sample & Hold Circuit, AB-Class Current Conveyor, Low Power Feeding, Analog Shift, Power dissipation.

### I. INTRODUCTION

All signals are transmitted in digital form in the digital world since they are easy to use, store & pass, but every signal is processed in analog form in the physical world, and so comes the task of an electronic engineer who knows how to more effectively transform analog signal into digital signal to store and relay the information present in the signal from one location to another. The sample and keep circuit was used to transform analog signal to a digital signal. It produces input voltage tests and holds this specimen for a certain time. For the high frequency and fast switching capacity AB-current conveyors are used. The sample and retaining circuit is also used in the data converting systems in different systems between the antenna and the digital circuit..

In the De- glitcher circuit, the sample and retain circuit is often used to prevent signal & analog de- multiplexer noise. When output current signal is required, operational amplifiers don't function properly and consequently the implementation of AB current carrier circuits comes into play as they work without global feedback, and often, compared with operational amplifier circuits, have various high frequency behavior effect.

In two phases of clock, the sample and hold circuit is regulated. In the initial clock step, the input is monitored and the input is kept in the second phase. The circuit uses a clock signal with a square wave. Inject in the signal, pedestal error and aperture jitter etc. Are certain errors contained in a sample and hold circuit? The circuit is also commonly used for sampling and holding in biomedical systems. The AB - current conveyor (CCII) [4] of second generation[2] is used because it has a high and a low.

Impedance rather than the first-generation current conveyor with two low impedance inputs. The current conveyor circuit is a network of three ports: X, Y & Z. In order to process both current and voltage signals, second generation current conveyors can be used. Two outputs are available for CCII, Z+&Z.

Two outputs are available for CCII, Z+&Z. With Z+ pin the present path is same with X port and with Z- pin opposite. The current transport system is used in the proposed circuit as a sample & keep circuit switch. In the case of the current transport device, a clock pulse, the voltage is transmitted from Y to X, while the current is transmitted from X to the Y port, but the pins all operate at very high impedance at high clock speed. The current transmission is carried out at the low clock level . In Output waveform is more reliable in two stage sample & hold circuit compared to single stage since input is constantly varied in mono stage, resulting in output variation at the time of holding, whereas in two stage, variation is much less at the output of the first stage, resulting in more flat output during holding time. For all stages, the clock is supplied concurrently and coordinated with each other, so both stages work simultaneously, which in turn ensures they track and keep at the same time.

In The proposed circuit has very high reliability and favorable performance, in comparison to previous circuits in the data conversion process. CCII'S Fundamental Framework

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 9 Issue I Jan 2021- Available at www.ijraset.com

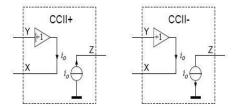

In the fact that there is no current flowing through the Y terminal, CCII differs from the first generation conveyor because terminal Y is a high impedance terminal while Z port is the current outlet and X terminal is the voltage input in the current conveyor. Therefore, unlike the first generation current conveyor, the current conveyor AB can be conveniently used for both current and voltage signals. There are two types of conveyor found in AB - negative and positive current conveyor. The current direction of the output port of the positive conveyor is the same as that of the input port, but the current direction of the output port of the negative conveyor is opposite to that of the input port. In FIG 1, all forms of conveyor symbols are shown.

This matrix representation of second generation current conveyor is

$$\begin{bmatrix} Iy \\ Vx \\ Iz \end{bmatrix} \models \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ 0 & +1 & 0 \end{bmatrix} \begin{bmatrix} Vy \\ Ix \\ Vz \end{bmatrix}$$

In the second level, the voltage of the conveyor current occurs at terminal X while the voltage appears at terminal Y and functions as a voltage follower flowing in port Z is same as flowing in port X act as a current follower, connected together

FIG 1(a) CCII(positive) and CCII(negative)

The current conveyor is used as a switch in the sample and retain circuit and is administered by a current pulse. The operation of the switch is to transfer the signal in a more methodical manner from one terminal to another terminal without major signal loss. Therefore, with negligible loss, the current conveyor transfers the signal as well as manages the signal as it passes through it.

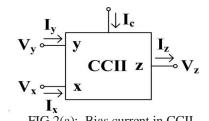

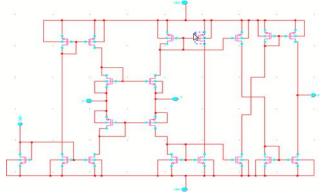

The current conveyor genuinely relies on the current mirror circuit that plays a major role between the terminals in monitoring the current as well as voltage. In this circuit, the present mirror is used, so the current in different branches would be the same, because this current passes with the same metal oxide semiconductor impedance. Therefore, the voltage between the semiconductor metal oxide terminals would also be equal. The circuit's bias current controls the current flow as it controls the MOS it is passing into. CCII sign of Bias Present in FIG 2(a) Fig 3(a), which is made up of N-MOS and P-MOS, is shown and its diagram is shown into it.

FIG 3(a): schematic Diagram of AB-CCII

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 9 Issue I Jan 2021- Available at www.ijraset.com

### II. PROPOSED CIRCUIT

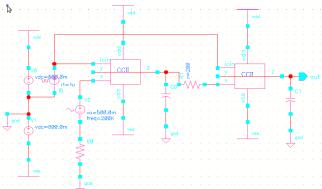

Two single phases of the sample and keep circuit with two phases are quickly cascaded, where the last phase corrects the first phase output. One capacitor and one resister are used in the single stage AB-CCII. Here, at the point of keeping, the single capacitor merely holds the charges and the single resister is used together with the capacitor for continuous pacing. AB-CCII acts as a switch for controlling and keeping time that governs the switching. Quiet current flows in the form of current pulses as the timing is shifted.

FIG 4(a): Schematic diagram of Sample and hold circuit with the help of AB-Current Conveyor

For both AB-CCII, the same quiet current is provided so that they can keep and track together. The diagram of the circuit suggested as shown in FIG 4 (a). The first initial stage output is given to the final stage input, which rectifies the initial stage output. Because equivalent input passes through both stages, both stages are coordinated with the same clock pulse. Therefore, at both stages, delays must be negligible. And we can't place a big capacitor value so the sample output and hold circuit would go down while the capacitor value rises. If the output from the same circuit can be rectified again, so the output would be entirely flatter relative to that circuit's previous output. In the first stage, at the moment of retaining the signal, there is a larger variation in the feedback and the voltage of the first stage is not flat and the capacitor discharges very easily. In the second phase, there is much less variation in the input at the keeping time, because the output is much flatter relative to the output of the initial stage.

We can increase the number of CCII stages for more reliable circuit outcomes, but the complication with the expansion is that the delay in the circuit often increases as the number of stages increases and because of increased delay, the circuit stages are not well aligned with the clock in the circuit. That is why it is not really possible to cascade more phases, but we can see effects in two phases, as opposed to a single phase, are more reliable. The sampling frequency called fc1 (fc1=1/tc1), since tc1 is the time span of the current pulses, is influenced by the performance of both sampling and keep circuits, when the current pulses are used as a clock for AB-CCII. The circuit output also relies on the time constant I determined by the multiplication of the R(resistance) and C(capacitor), so we can use this for T..

$$(\tau = RC)$$

.

### A. Non-Ideal Effect

Title and Author Details

Any outcome is possible on the first circuit on extreme ideal parameters, but in fact all parameters can be modified, as each circuit has its own resistance and power and is applied at high frequencies. AB-CCII parameters often change as the parameters changed are taken into consideration and the matrix has no unique zeroes and zeroes. Therefore the new matrix will be interpreted

$$\begin{bmatrix} Iy \\ Vx \\ Iz \end{bmatrix} = \begin{bmatrix} Yy & Air & Gmr \\ Avf & Zx & Avr \\ Gmf & Aif & Yz \end{bmatrix} \begin{bmatrix} Vy \\ Ix \\ Vz \end{bmatrix}$$

If Aif & Avf's value is the current going into the circuit and the transport voltages gains within the circuit, the current back- and conveyor voltage, which is near zero, is very close to the device and to Air & Avr respectively. The terminal impedance and admissions of Yz, Zx and Yy are reduced. The trans-conductance GMF(a) of terminal Y to terminal Z is important in some circuit implementations but the reverse trans-conductance Gmr(a) rarely affects the conduct of the circuit. If mistakes in current and voltage are taken into account, they may be rewritten as

$$V_{out} = V_{[in]} [1 - e^{1/\tau_n f}]$$

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 9 Issue I Jan 2021- Available at www.ijraset.com

Where  $\tau_n(a) = (R+R_{Xa})(CC_{Xa})$ ,  $R_{Xa}$  is the parasitic resistance and  $C_X$  is the parasitic capacitance.

We have to know about the resistance value in the simulation result. 501K cumulative and 10.00fF capacitance. Here the resistance value is very high, so that it is taken into consideration. Ideally, when monitoring, the circuit would be vulnerable to certain mistakes, both can be so much fewer.

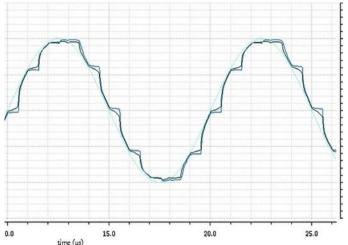

### B. Post Layout Simulation

On Cadence Virtuoso sampling & holding circuit is simulated. QRC was also tested and compared result with The consequences of the scheme. NO DRC error & NO LVS error with only minor differences in the comparison of findings without QRC. The use of the minimum surface with the least parasite effect is taken care of in circuit during final layout simulation. GDS was created with the output waveform in both the results after the final layout simulation. The designed area is square 2269.6598  $\mu$ m

### C. Simulation Results

In PSPICE simulation in c- virtuoso and 180nm technology is performed at this given circuit. Both files are taken from the Cadence Virtuoso library of gpdk180. The NMOS feature ratio is 302nm long and 3.01 $\mu$ m in width and PMOS feature ratio is 302nm long and 8.01 $\mu$ m broad. The voltage source is  $\pm 0.8$  volt and the voltage peak to peak is 0.6 volt.

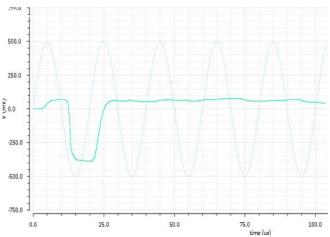

A skewed current value of  $1.0\mu A$  and a pulsed form of  $1.0\mu s$  is given. The defined tendency governs the whole circuit scenario and handles the sample and hold time. If the Ic(a) is  $0.0\mu A$  (Low 0), there is no signal-to-output signal transfer, which is known as the keeping state, the maximal resistance of input time by the 508K TS circuit is given. This is shown in FIG 7(a) when the input signal is in sinusoidal form but the circuit output is straight and the output voltage equals around 0. If Ic(a) is  $1.0\mu A$  (High 1), so the input signal transfer is achieved without a failure, since the very low resistance circuit is roughly 1.03K average.

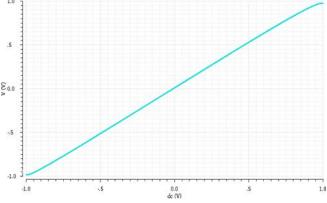

FIG 6(a): DC characteristics of CCII

This essentially means that the variation in output voltage is seen in a linear curve in comparison to the change in the input voltage. As input tension changes from -1V to 1V and the output tension can be shown to be between -0.98V and 0.98V..

FIG 7(a): Output wave at hold conditionin in S&h circuit

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 9 Issue I Jan 2021- Available at www.ijraset.com

The sample frequency of 1 MHz is given for the signal sampling and keeping on the circuit shown below FIG 8(a), where the signal is kept up in particular at a high clock level and the signal is monitored at zero level

The waveform output is seen in FIG 8(a) where 1 is the infeed signal wave and two other waves in the fig are the infeed and final stage output. As the keeping time arrives the output of the initial step is not quite flat. However, in the final step, the output is very flatter and the condenser discharges a little slowly. The measured capacitance and resistance of condensers are external and parasite

FIG 8(a): Output waveform

| Parameter                      | This<br>work | M.<br>Kumn<br>gera | Chatter<br>jee et<br>al | Eerr<br>eira<br>et al | Swigu<br>n et al. |

|--------------------------------|--------------|--------------------|-------------------------|-----------------------|-------------------|

|                                |              | [8]                | [9]                     | [10]                  | [11]              |

| Technology<br>(µm)             | 0.18         | 0.18               | 0.25                    | 0.8                   | 0.13              |

| Supply<br>voltage (V)          | ±0.8         | ±0.9               | 0.5                     | 5                     | 0.8               |

| Bandwidh<br>(MHz)              | 11           | 11                 | 6                       | 9                     |                   |

| Sampling<br>Rate (MS/s)        | 1            | 1                  | 1                       | 0.25                  | 1                 |

| THD (dB)                       | -46          | -62                |                         |                       |                   |

| Power<br>consumpti-<br>on (mW) | 0.011        | 0.015              | 0.4                     | 1                     | 1.85              |

Comprasion Table Between Proposed Circuit And Previous Circuits

### **III.CONCLUSIONS**

This sample and keep circuit is proposed in this manner, as opposed to the last circuit the circuit offers structural and preferential output. When the circuit has two steps, the final output waveform of the circuit will influence when the signal is retained. The usage of a current conveyor as a switch in this presented circuit, and this circuit provides us with less power and a greater speed. The transporter uses current as a switch and expects circuit flipping to normalize its results. The circuit also displays greater admiration for the output at stopping point than any other circuit produced to improve digital precision. In comparisons to standard present transducers, this AB-current transporter is even more reliable.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 9 Issue I Jan 2021- Available at www.ijraset.com

### REFERENCES

- [1] https://www.99acres.com/articles/indore-to-install-automatic-control-and-switching-system-for-samplehold.html.

- [2] M. Jablonski, G. De Mey, A. Kos, "Quad configuration for improved thermal design of cascode current mirror," Electronics Letters, vol. 48, 2012, pp. 80-82

- [3] V. Surakampontorn, W. Riewruja, V. Kumwatchara, and K. Dejhan, "Accurate CMOS-based current conveyors," IEEE Transactions on Instrumentation and Measurement, vol. 40, pp. 699-702, 1991.

- [4] M. Kumngern and K. Dejhan, "DDCC-based quadrature oscillator with grounded capacitors and resistors," Active and Passive Electronic Components, vol. 2009, pp. 1-5, 2009, doi:10.1155/2009/987304

- [5] M. Kumngern and K. Dejhan, "DDCC-based quadrature oscillator with grounded capacitors and resistors," Active and Passive Electronic Components, vol. 2009, pp. 1-5, 2009, doi:10.1155/2009/987304.

- [6] M. Kumngern, J. Chanwutitum, and K. Dejhan, "Electronically tunable multiphase sinusoidal oscillator using translinear current conveyors," Analog Integrated Circuits and Signal Processing, vol. 65, pp. 327-334, 2010

- [7] K.C. Smith and A.S. Sedra, "The current conveyor-a new circuit building block," Proc. IEEE, Vol. 56, pp. 1368--1 369, Aug. 1968

- [8] Hassan O. Elwan and A.M. Soliman, "Low--Voltage Low--Power CMOS Current Conveyors," IEEE Trans. on Circuits and Systems-I, Vol. 44, No. 9, pp. 828-835, Sept. 1997

- [9] R. Trejo-Guerra, E. Tlelo-Cuautle, V. H. Carbajal-Gómez, et al. "A survey on the integrated design of chaotic oscillator," Applied Mathematics and Computation, vol. 219, 2013, pp. 5113-5122

- [10] R. Chaisricharoen, B. Chipipop, "Novel CMOS second-generation current-controlled conveyo base on modified differential-pair inputstage," 7th International Conference on ASIC, 2007, pp. 707-710

- [11] "Methodology for designing switched capacitor sample and hold circuit used in data converters" IET circuits, Device and systems, 28th Nov 2013

- [12] Biao Li,"A high DC gain op-amp for sample and hold circuit", proceedings of the 2nd international conference on computer science and electronic engineering, ICCSEE 2013

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

### INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)