# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 9 Issue: III Month of publication: March 2021

DOI: https://doi.org/10.22214/ijraset.2021.33238

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

Volume 9 Issue III Mar 2021 - Available at www.ijraset.com

### High Overhead Flip-Flop Alert Dependent on Time Slack Control Charge Sharing

Pochana Ashok Kumar<sup>1</sup>, P. Venkatapathi<sup>2</sup>, M. Shiva Kumar<sup>3</sup>, Dr. M. Sreedhar Reddy<sup>4</sup>

<sup>1</sup>Mtech scholar, <sup>2</sup>Associate.Professor, <sup>3</sup>HOD, <sup>4</sup>Principal, Department of Electronics and Communication Engineering, Mallareddy

College of Engineering, Hyderabad

Abstract: Timing mistake predictors are extremely capable of minimizing the worst period by timing a design slackness regulation. However, such timing error forecasters need a large amount of silicone region and tests, which decreases the future system stage advantages. This paper includes the projection of installation breaches for low flip flop alert (FF). This includes an alarm generator with a pause buffer and a typical fast forward feature for a master/slave link. LUCC allows low overhead FF to leverage the energy sharing principles. The FF plan consumes just 30% less of the emission zone and transmits electricity 27% less of the simulation time. The proposed voltage and frequency on FF system with 130 Nm CMOS is used to figure out how voltage and frequency scaling could shift as FF operates. Testing the prototype chip results indicate that a power gain of 44 percent can be obtained with a distribution voltage of 0.9V comparing worst-case variant. Energy using 36% less than in the worst-case design for a conventional processor.

Index Terms: Low flip flop alert (FF), alarm generator, LUCC.

#### I. INTRODUCTION

This applies because of the variations in scaled output nodes with operating voltages, and temperatures. Timing or voltage guard bands apply combined operating power to provide voltage to compensate for PVT. Therefore these guard belts greatly reduce the performance or raise the power consumption in the best or usual conditions in a design. Furthermore, aging transistors degrade performance quality over time Watchbands can then be added in terms of the lifetime of the design. As a consequence, the conventional worst case design approach cannot be utilized as wide guard bands for combining energy-efficient structures are used in nanometer nodes. This is why methodologies for design that can reduce the guard bands were added.

Historically, device monitoring was proposed to monitor the chip status during the development phase. Body Biasing is used in these methods to adjust the transistor threshold voltage based on process conditions. This techniques can only help with drastic systemic improvements.

Vital circuit replicas were used to monitor the latency of the critical architecture routes. In this method we use the CAD to evaluate the volatility of the delay. This technique will cope with major changes globally, but not regional or local disputes. In addition, the critical path activation depends on the input data pattern.

If errors are found, on the other side, the time slowdown will solve local and global inequality. These techniques track mixed logical performance with sophisticated flip flops in particular (FF). In case of a timing breach, an error signal is flagged. Thus, through controlling the error signal, supply voltage or design frequency may be changed. These strategies are mostly split into two categories: [5] and [6] and [8] and [9].

Error detectors, for example, Razor I[6]and Razor II[7], are found after time errors arise, and architectural re-processing processes are used to fix the time defects. Error detectors, though, add substantial minimum route delays due to buffer injection that generate wide area overhead.

This capability is available for high-performance processor types, but not integrated circuits for applications (ASICs). There is no overhead demand for Bubble Blade. Pumping close schemes are introduced whereas FFs are seen on pipelines.

Error predictors flag a warning signal to monitor the late outcomes before time breaches occur. As the FF performance is often right, overhead correction of these techniques does not occur. Fehler predictors are good for ASIC application as a correction mechanism is not needed.

These methods can therefore only steadily track the delays of the critical routes. This group is the FF of the Canary Islands Canary FF uses a dual sampling architecture to predict time breaches. Thanks to its FF shadow, Canary FF has a wide spectrum of overhead capacity and prevents buffers.

Volume 9 Issue III Mar 2021- Available at www.ijraset.com

#### II. ERROR DETECTION AND CORRECTION FF

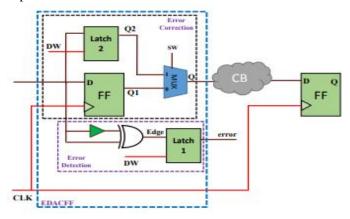

The EDAKFF is seen as Figure I consisting of two major components: ERROR and Correction. An ED transmitter detection device includes a buffer pause and an XOR gate and an error signal latches, where an essential direction signal change violates the FF time limit. The EC circuit consists of a main FF, a timer and a MUX as seen in this diagram (i).

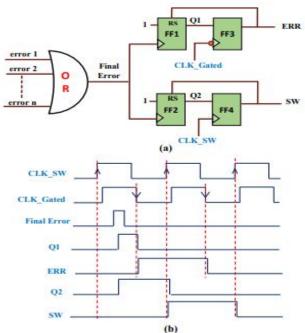

By selecting the right FF or latch value, we will recover from the time violation by using the MUX. After the correct data from latch 2, an error signal was observed, the control circuit in Figure (ii) induces the SW transmission for the MUX. This circuit also produces a single cycle clock event ERR (Error Pulse) signal, which allows you plenty of time to recover the error. Signals "CLK Gated" and "CLK SW." are the ERR and SW catch signals. Signals Please be told that the let signal is received on the boundary and the FF3 non-inverted clock. The ERR phase blocks CK and DW signals (iii).

Unlike previous experiments, we suggest a metastability detector for the performance of the FF, which is distinct. As the FFs are introduced into the circuit, they are used as an input to the inverter and become unreliable in performance the inverter. Our device will use MUX to enforce Q 1 first when faults arise on the Figure 1 circuit. Example 1. After obtaining signals from the error detector, the MUX selects the Q2 output of latch 2.

Figure 1. an EDACFF on an FPGA.

But the number can also be metastable in latch 1 and latch 2. This dilemma can be overcome by putting some time limits without a metastable sensor on the circuits. Section 3.5 includes a comprehensive overview.

Figure 2. (a) and (b).

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 9 Issue III Mar 2021- Available at www.ijraset.com

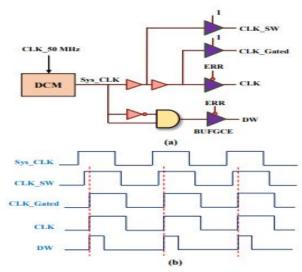

Illustration 3. (a) the Circuit of the Clock Generator and (b) its schedule.

A guard band (a variable-length clock) is recommended to be used in a late clock. In this way, the working frequency of the clock usually defines the architecture. In [13], an alternative is also proposed for a double sample configuration near Canary ff. A [14] time management device uses a warning window generator to prevent time breaches and to set up a detection window. A transformation detector in the clock tree is used in this approach to build a detection window that allows it tougher to apply the clock tree.

A linear detective found a sluggish data transfer to estimate chronological infringements over a span of time. This FF is not field-specific and power-efficient because the delay data is delayed by several buffers and the edge detector is applied. Proposes a sensor to track the master's late performance to forecast clock breaches. Since it uses the two samples configuration, a large area and power are required. A FF in records the transfer of data via the negative half-cycle. The design needs a running time of more than 50% to guarantee greater performance since an adverse semi-cycle of the clock measures its warning margin.

On the maximum stage of the tower, the latching master clock is pulsed. In this way, the edge detector consume more power and electricity. Double sampling architecture in situ detection is used. A error timing forecast uses the FF-like architecture, but a tunable delay buffer for the latency of the data signal. Architectures for the double sampling involve wide areas and overhead capacityA time error detector is indicated in the present format in [23]. A 9-transfer detector[24] may be used for low-power applications with a supply voltage level of 0.44–1.1 V. With expanded nanometer technology node variations[25], critical path detection is becoming difficult. Additional critical paths with the time error predictor can also be tracked to prevent a functional failure. Consequently, this article includes a low region and an average time error metric for time delays tracking. The proposed FF alarm can also be used as an ageing sensor next to the work [13] and [26].

#### III. SHARING-BASED PROPOSED FLIP-FLOP NOTIFICATION

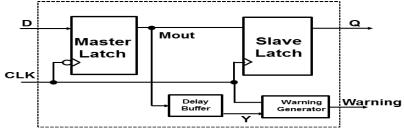

FF is used to check PC's time lapse breach . At the beginning of data life, FF can generate an alert if a passing of data happens before clock rollover. Traditionally, IFC monitoring for input from FD is involved to detect set-up violations. This phrase "late data" is used to identify the possible timing violations in both systems. The techniques use the sample transformation vector or word detector function.

Fig. 4. Proposed warning FF.

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 9 Issue III Mar 2021- Available at www.ijraset.com

The FFs may be classified into four groups.

- 1) Data entry Samples D FF and a double-sampling process [11];

- 2) Master latch performance samples Mout, using double sampling [20];

- 3) FF data entry D sample and transformation identification methodology;

- 4) Master latch performance Mout samples utilizing the technique for transfer detection [18].

When data from FF points is monitored for an incoming alarm, both the FF time and notification margin should be taken into consideration for buffer delays. In this method, only The Master Lock would be allowed to swing open while a door is closed. Buffer length.

FF Warning is targeting the tracking of activities that control regular transactions. Furthermore, there is an online method to monitor the calendar execution and lapses. The buffer period is the FF's proposed risk amount. If the "FF" is occurring right before the master latch is mounted, then there would be an alarm signal. The warning signal remains on low stage. As data arrives, the FF worked efficiently on it. Warning generators do not provide accurate details for late distribution. The graphic graph shows the sequence of the expected warning FF. 1.

#### A. Flip-flop operation suggested

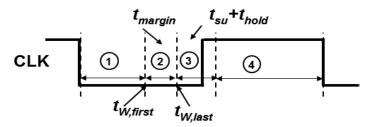

A transfer of data at the FF input occurs in one of the 4-time windows shown in the figure. 2. An early delivery of data is considered to be a data transition in window 1. The time slack in this case is quite strong. Window 2 is considered to be a late transition of knowledge The period slack accessible in this case is lower. If the critical path latency is increased due to adjustments in the PVT, data transmission in this window will break the timetable. A 3-period window data transfer leads to a configuration breach;

Fig.5.Possible data transfer timing windows.

Table I Proposed Notification Operation FF

| Timing<br>Window | Data<br>Transition | Before the rising<br>edge of clock |      |    | After the rising<br>edge of clock |      |      | Q    | Warning |  |

|------------------|--------------------|------------------------------------|------|----|-----------------------------------|------|------|------|---------|--|

|                  |                    | D                                  | Mout | Y  | D                                 | Mout | Y    |      |         |  |

| 1                | Rise               | 1                                  | 1    | 1. | X*                                | 1    | 1    | 1    | 1       |  |

|                  | Fall               | 0                                  | 0    | 0  | X                                 | 0    | 0    | 0    | 1       |  |

| 2                | Rise               | 1                                  | 1    | 0  | X                                 | 1    | - 1  | 1    | 0       |  |

|                  | Fall               | 0                                  | 0    | 1  | X                                 | 0    | 0    | 0    | 0       |  |

| 3                | Rise or Fall       | X                                  | PS** | PS | X                                 | PS/D | PS/D | PS/D | 1/0     |  |

| 4                | Rise or Fall       | X                                  | PS   | PS | X                                 | PS   | PS   | PS   | 1       |  |

<sup>\*</sup> Don't care \*\* Previous State

And the latch master output may be metastable. The cumulative time limit for the architecture should then be reached (1) so that changes to PVT will arise before the timing window 3. The overall period is defined

$$T_{\text{max}} \leq T_{\text{CLK}} - t_{\text{ClktoO}} - t_{\text{su}} - t_{\text{margin}}$$

(1)

TCLK is the clock duration, tClktoQ is the previous step of Q FF, tsu is the initialization period, tmargin is the warning margin. During timeout window four the master lock monitor does not Display transfers of data since the master lock is invisible.

FF warnings are found in table I and are sensed for each clock during low to high pulses (see Fig. 1). Although the specifics vary in the time window2, the master delayed is different from the master (Mout) internal. In this scenario, no warning signal will be provided. However, the FF samples the right meaning in both instances. If a switch takes place within time frame 3, the master latch (Mot) output will reach metastable status, and either logic "0" or logic "1" can be resolved. Thus, current (D) data or the previous state FF may be saved by delayed master performance (Y). The figure indicates the hypothetical timetable for the planned alert FF. 3.

Volume 9 Issue III Mar 2021- Available at www.ijraset.com

In the early clock cycle I, before the alarm margin, data are passed. The Master Lock needs to create a powerful and enduring impact. The method yields A1 after having "Y=-" During the clock's minus cent. The low and high clock phases are therefore both subject to the same delayed master output. (Y). (Y). Solid logic warning is output signal. The FF (D) pause and the MW output combined make up the input-to-output duration. Shift of data in clock intervals.

Fig.6.The suggested FF alert conceptual schedule.

When a master latch collects valid values or sets and samples them over time. This delayed master locking output allows the clock to turn the to A3 production in the high clock process . In this scenario, the continuous master output varies with a high and a low step of the period. However, the alarm generator works low like A4. It seems that the low voltage warning has been adequately transmitted, and the FF circuit has memorized the alertThis solution just does not need an overhead approach. The data transfer from an external source happens in clock cycle III during the master latch's initialization time frame. This transmission is not shown at the master buffer output as A6. For that cause, the FF could not detect that improvements have taken place. During the high clock process, it would not be possible to render any data transformations at the latch master outputs since they are invisible in the high-clock process. With this said, there is no short distance problem with the proposed FF. The minimum design time is a little over six months.

$$T_{\min} \ge t_{\text{old}} - t_{\text{ClktoQ}}$$

(2)

The minimum time-to-Q in the previous stage FF is tClktoQ and the minimum clock time for the previous stage FF is tMin. The slacken alarm in the FF was therefore defined as the difference between POFW and Last Warning (refer to Fig. 2). Preferably this period should be the pause. This disability is clearly detectable.

$$td$$

, slack= $td$ , buffer (3)

There to, the observable slack is the slack and the buffer is the buffer delay.

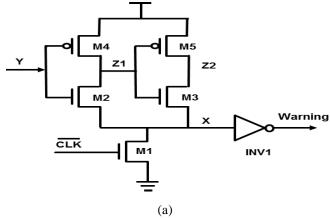

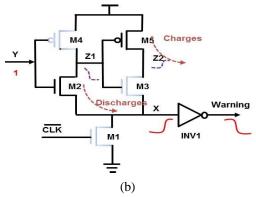

#### B. Warning & Generator

Alerts are generated utilizing the charging sharing concept. During the high clock phase, only seven transistors are needed. The alarm generator schemein Fig. 4. Two cascaded inverters are powered by delayed master production. On the bottom

Volume 9 Issue III Mar 2021- Available at www.ijraset.com

These transistors operate as traditional transistors, and during the timing stage the supply node X is set to logic nil. The X node flips clockwise in this case, while the M1 node remains unchanged. We like the alarm system, too. The intermediate loads per node vary with the input of the alarm generator in every Z1 to Z2 intermediate node for high and low clock edge transitions. The voltage of the intermediate node X is higher than the voltage of the node Y. The INV1 is intended to drive low voltage high current. The inverter threshold should be smaller than the node charging voltage. The INV1 inverter is 60 percent loaded. The inverter performance is smaller than the rated voltage.

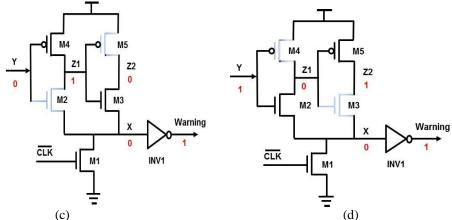

Table II gives the alarm generator operation. The delayed master development (Y) depends on the time frame (see Fig. 2). The adjustment in input data (d) causes: 1) the switch to Y during low-clocking; 2) the switch to Y during high-clocking, and 3) the switch to clocking at the next low-clocking stage. In the lower stage of the clock, where the data (D) is translated to time window 1. In the high-clock phase, when the transformation (D) takes place in time window 2 the transition to Y occurs. In Y before the next low clock step for the time windows 3 and 4 no data transfer occurred. The comprehensive role of the alarm generator is addressed in Sections IIB.1–II-B.3.

- 1) Clock Details (Y) Low-phase Change: If a transition occurs at Y in the low-clock period, the Y node condition is the same as in the high-clock cycle. For this cause, the intermediate nodes X, Z1, and Z2 stay unchanged. The logic gate X is going to be discharged until the CK = empty. When the alarm goes off, the reaction is urgent.

- 2) Clock High Phase Rise Transformation (Y): First in the clock is reasonable to zero in high phase with steep adjustments in warning input (Y). The Z1 phases are filled with a zero feedback during the low clock period, while the Z2 phase is loaded with a '1' logic. The original states are X, Z1 and Z2, respectively. Five and a half (a). The transistors M1 and M2 are related. The X node is excluded from the operation and empty logic is restored. In comparison, the Z1 and Z2 nodes are small and highThe status of nodes X, Z1 and Z2 changed during the positive half period of the clock after an improvement in the alarm. four four (b). If the transistor M1 is off, the driving is stopped. Eingang node B is loaded with Eingang node A. Sharing of loads between nodes X and Z1 Node X voltage grows to the conceptual level. If the voltage reaches the switching level, the warning signal is set to be tiny. This indicates there is a change in the delayed master production process.

- 3) During the High Clock Process case Transformation (Y): There is a significant level of noise in the Y-axis at low clock frequencies, and lowering the present clock frequency will increase this. The initial states are X, Z1, and Z2. Five five (c). The resistor at the bottom of the clock will give a high warning. The intermediate node Z1 has a high likelihood value and the value of the Z2 is large. The X node is loaded through the M3 resistor from the Z2 node on the increasing clock edge. This load shift improves the node's efficiency. The output of the alarm generators is somehow slow. In high clock step, there are three states X, Z1, and Z2, Four (d).

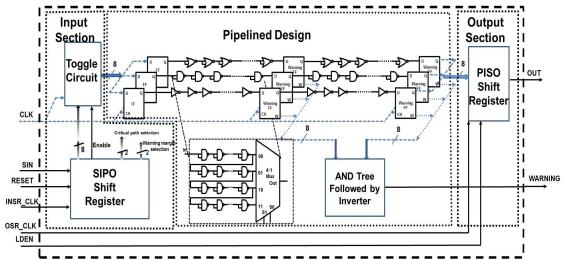

#### IV. EXPLAIN CHIP IMPLEMENTATION

A concept model to evaluate the FF functions has been launched. In the Fig, the test chip block is seen. 6. In the real short term, these blocks include input, pipeline setup, and exhaust. The Serial Integrated Pluggable Output (SIPO) is used to complete the circuit. The two-stage completely secured and working digital circuits are also provided in the category for design section. A parallel serial out (PISO) is included in the output section.

In the implementation of the specification, It uses a 13-bit SIPO change register. The FF warning margin for the pipeline specification entry is 8 bits., 1 bit for the Tug Circuit Signal Allowed, 2 bit for the vital path latency, and 2 bits for the FF notice margin each clock cycle, the crucial path must be enabled to validate the responsiveness of the proposed chip FF Alert that the entrances may be altered with the circuit toggles in the pipe configuration.

Volume 9 Issue III Mar 2021- Available at www.ijraset.com

SIPO shift register toggle circuitry. The key has been turned. In the FF alarm in the pipeline configuration necessary to determine in order to change the design feedback is in each clock cycle needed to determine is high. In this case, the SIPO registered The input data pattern may be reversed and inverted with each clock period utilizing the toggle circuit.

Fig.7.Alarm generator service for timing window 2 data transformations. (a) Previous to the change to grow. (b) Transformation following growth. (c) Before autumn change.

Fig.8.Procedures for employing this chip.

The pipeline specification is supplied. Because at the design period all pathways in the pipeline are essential, all paths work 100 percent throughout the runtime.

There are eight directions for each step of the pipeline design, constructed with NAND, NOR, and inverters. In the endpoints of all essential pathways, the planned alert FF is inserted. A configurable 4:1 multiplexer delay chain on the critical track will adjust the length of the critical route in the chip. This requires a different clock frequency to work in the same configuration. The warning signal is merged with the AND tree in one warn signal of all notification FFs. The AND tree power is transformed to an active signal Alarm by an inverter, which triggers the alert signal at a low FF level. The lower pulse width of the proposed FF warning signal shall be the AND tree latency, indicated by

$$td$$

, AND-tree = $TPW$ , min (4)

No matches between AND tree and TPW with its minimal pulse width minimizes any adverse results.

The setup loaded on a pipeline has several or 8 data pieces. Two external inputs are present in the PISO shift register: the clock reference (OSR) and the control signal (LDEN) for loading and adjusting the shift register architecture. Second big concern is power signals (LDEN). The second regulation is turning signals. When the LDEN is solid, each clock cycle loads the output of the pipelines in the PISO change register.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 9 Issue III Mar 2021- Available at www.ijraset.com

In each clock cycle, the stored PISO shift register data is serially transmitted and the LDEN is small.

#### V. MEASUREMENT RESULTS

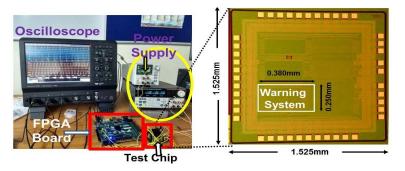

This is theoretical configuration of the electrical unit. A 130-nm size chip, an FPGA and a load chip QFN 48 has been shown. 7 leveraging the field-programmable gate array (FPGA) (GFD). The Change register hardware can obtain the input details from the FPGA (ZedBoard). The PISO register keeps the serial output continuously. In case of security event, all I&O audit details must be registered by the I&O registry

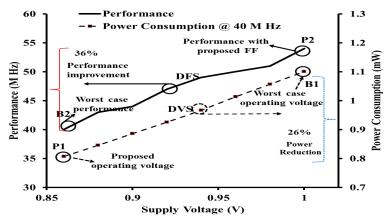

Fig. 9.Project output and energy use.

The frequency and worst case configuration is provided by the so-called AMOS calculation which is 10 percent voltage decrease, 85°C temperature, and 2-sigma process variance.

The B1 network will be 40 Mhz in the base load schedule and the B2 network will be 60 Mhz. 8. The tube design would result in a lower P1 voltage for the same performance, which would minimize dynamic voltage Scaling by 26 energy savings (DVS). The voltage is sustained constantly and the dynamic frequency geometry scaling frequency rises. The higher P2 frequency, resulting in a 36 percent improvement in tube output at supply voltage, allows pipelines with the expected FF and DFS to be designed.

#### VI. SIMULATION RESULTS

This field contains the FF warning requirements including the full loaded voltage (MCV) of the interim node and transistor sizes for alert generation. Section IV mentions the usage of the proposed FF alarm. The relation at FF level has been explored further to calculate areas and power savings for Warning FFs. The suggested FF is added to 130 nm CMOS tech. The post-layout simulation of the parasite was performed using HSPICE software.

#### A. Alert Meter.

The method of alarm induced was intended for its participants to interact. FF functionality is calculated by the display on the alarm generator node and by the measurement of its output capacity. Many simulations of Monte-Carlo were carried out at  $25^{\circ}$ C to validate the switching constant at node X at an input voltage of 0 - 1,3V. (see Fig. 4). This graph displays the MCV and the inverter X fault threshold in the tram (INV1). 12.

The function of the proposed netlist has been checked by postage simulations on parasite extracted netlist

Volume 9 Issue III Mar 2021- Available at www.ijraset.com

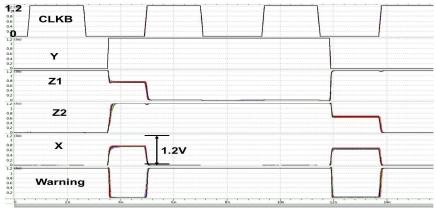

Fig. 10. Alert generator time diagram.

The generator of alarm. Picture. Photo. Photo. Picture. 16 CLKB time schedule (reversed clock), alert feedback (y), notification signals, intermediate Z1 and Z2 nodes for lifting/dropping changes. At Node Y, where the CLKB = 0.0 voltage is loaded up or down to more than half the voltage of supply, the Intermediate Node X is loaded up or down. For an intermediate boost transmission, The Z1 intermediate node discharges the X node and the Z2 node for voltage propagation. For the dropping power line, the billing node X along with the voltage supply node Z1 are often unloaded at intermediate values. In all instances, the alert signal is triggered by a dark red to pink pulse. In comparison to the alert duration of 2 seconds at 1.2 volts, the alarm time retardation is increased by 5 seconds at 0.7 volts. The percentage of difference of the latencies of 1.2 and 3-sigma phase differential gives at 0.7 volts is 8.7 and 32.0%. in every event . (Requires variety and variation in die-to-die.).

#### B. Comparison of flip-flop Degree

Industrial CMOS 130-nm processing, in comparison to current FFs, serves to measure the zone and save energy for the anticipated signal FF, for Canary FF as for sequential warning detection, location tracking and pulse-dependent timing. The three FFs being contrasted in Table III.

1) Area: The nation will save several tons of FF by upgrading the standard FF method. The suggested FF, however.

Table III Comparing Warning FFs

| Parameter                         | Proposed            | Ref [11]        | Ref [15]             | Ref [20]            | Ref [18]             | DFF  |

|-----------------------------------|---------------------|-----------------|----------------------|---------------------|----------------------|------|

| Area (layout)                     | 1.95×               | 3.45×           | 3.1×                 | 3×                  | 2.81×                | 1×   |

| Number of buffers                 | 1                   | 2               | 3                    | 1                   | 2                    | NA * |

| Monitoring node                   | Master latch output | FF input        | FF input             | Master latch output | Master latch output  | NA   |

| Architecture                      | Charge sharing      | Double sampling | Transition detection | Double sampling     | Transition detection | NA   |

| Clock to Q delay                  | 1.05×               | 1.05×           | 1.01×                | 1.03×               | 0.97×                | 1×   |

| Setup time(ps)                    | 113.6               | 71              | 77                   | 117.8               | 187.76               | 76   |

| Hold time(ps)                     | -10.3               | 1.9             | 1.9                  | -13.2               | -17                  | 2    |

| Clock power (µW)                  | 4.62                | 8.51            | 4.05                 | 8.49                | 4.04                 | 3.97 |

| Average Power<br>(No warning)(µW) | 11.5                | 20.45           | 15.6                 | 19.2                | 15.8                 | 7.32 |

| Average Power<br>(Warning)(µW)    | 14.5                | 19.21           | 17.1                 | 19.2                | 17.3                 | NA   |

| Peak Power<br>(No waming)         | 1.14×               | 2.45×           | 1,12×                | 2,42×               | 1,82×                | 1×   |

| Peak Power<br>(Warning)           | 1×                  | 1.66×           | 1.52×                | 1.81×               | 1.33×                | NA   |

<sup>\*</sup> Not Applicable

In comparison to [18], occupies 30 percent less ground. The savings in this region are attributed to the need for fewer transistors in the alarm generator. Also, In comparison to the proposed FF alarm, the only one includes a warning margin buffer, two warning margin buffers required, one for alert margins and the next for change detection. Regulation of communities also concentrates on double sampling and sequential audiovisual alert principles.

#### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 9 Issue III Mar 2021- Available at www.ijraset.com

2) Average Power: Compared to conventional FF, the FF alarm uses 1.57 pounds of energy. But with the operating frequency of 250 MHz, the suggested FF uses around 27 percent less power than the PTE at 50 percent of the data operation. The reduced usage of the workstation is because of the smaller number of transistors in the warning generator. The proposed FF high pulse in the FF alarm is ineffective in relation to the optimum pulse amplitude when triggered normally. While Canary FF models and in situ tracking consume 2.14 figures and 2.13 amounts, the conventional data FF consumes zero figures. The improvement in efficiency is consistent with the use of two sample architectures of a more accurate transistor. This act allows for greater use of electricity than no alert cases. However, due to the decreased data operation on Shadow FF, Canary FF uses less power and notifies the alarm signal without a warning. The cost of energy due to the warning window is not equivalent such that it can be broken into FFs.

3) Peak Power: For certain cycles, the maximal resistance of the proposed Formula is observed. The transmitting intensity of the data in the blinking margin window is higher than the transmission power generated by the system. Post-window alert margin change. Dual-Sample Techniques[11],[20] absorb a higher pitch than transitional detection methods [15], [18]. The full strength of the FF is seen in Table III. If the alert signal is flagged, the FF proposed consumes minimum peak capacity, out of the FFs compared. In the absence of an alert, 14 percent extra maximum strength relative to traditional DFF is absorbed by a planned FF. A 12% increased power in contrast to traditional DFF is used for the [15] alert detection series.

#### C. ISCAS89 Circuits of Benchmark

The ISCAS 89 benchmarking circuits[27] were configured for slow service, 125°C temperature and, in the worst conditions, a 10 percent drop in power supply voltage. It is suggested to concentrate on certain critical pathways with FFs less than 20 percent of the time. FFS replacement is a minimum of FFs in the method. The designs are simulated first on a gate-level simulator with a nominal 1.2 V voltage of 25°C in normal operating conditions. Cadence LIB is the timing library for microprocessors. The voltage is 20mV at the warning level. The POFW voltage is detected with simulations for each implementation. The realistic prototypes will operate with a lower pressure based on the simulated results of the actual FF reactor. Using FF benchmarking will save 22% of ISCAS89 prices. See table IV of the literature.

#### VII. CONCLUSIONS

DVS and DFS are optimal means of reducing the worst-case time guard bands. Timing Error Tracking This paper introduced an FF alarm that tracks the delayed performance of the master latch to forecast the violet's timing. The suggested FF alert uses 27% fewer resources and need30% less-power in the literature compared with available time error predictors. In order to verify the invention proposed to reduce the listening range, A 130 nm industrial CMOS technology test chip is produced. Our theoretical measurements indicate that the electrical configuration of the FF alerting system operates at a clock frequency 44 and 31 percent higher than the usual worst-case design in standard situations, respectively atvoltage of 0.9v and 1.05 V. Power consumption is 36 percent decreased.

#### **REFERENCES**

- [1] T. Kuroda et al., "Variable supply-voltage scheme for low-power high-speed CMOS digital design," IEEE J. Solid-State Circuits, vol. 33, no. 3, pp. 454–462, Mar. 1998.

- [2] J. W. Tschanz et al., "Adaptive body bias for reducing impacts of die-to-die and within-die parameter variations on microprocessor frequency and leakage," IEEE J. Solid-State Circuits, vol. 37, no. 11, pp. 1396–1402, Nov. 2002.

- [3] J. T. Kao, M. Miyazaki, and A. P. Chandrakasan, "A 175-mV multiply-accumulate unit using an adaptive supply voltage and body bias architecture," IEEE J. Solid-State Circuits, vol. 37, no. 11, pp. 1545–1554, Nov. 2002.

- [4] A. Drake et al., "A distributed critical-path timing monitor for a 65 nm high-performance microprocessor," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2007, pp. 398–399.

- [5] D. Ernst et al., "Razor: A low-power pipeline based on circuit-level timing speculation," in Proc. Int. Symp. Microarchitecture, Dec. 2003, pp. 7–18.

- [6] S. Das et al., "A self-tuning DVS processor using delay-error detection and correction," IEEE J. Solid-State Circuits, vol. 41, no. 4, pp. 792–804, Apr. 2006.

- [7] S. Das et al., "RazorII: In Situ error detection and correction for PVT and SER tolerance," IEEE J. Solid-State Circuits, vol. 44, no. 1, pp. 32–48, Jan. 2009.

- [8] M. Fojtik et al., "Bubble Razor: Eliminating timing margins in an ARM Cortex-M3 processor in 45 nm CMOS using architecturally independent error detection and correction," IEEE J. Solid-State Circuits, vol. 48, no. 1, pp. 66–81, Jan. 2013.

- [9] H. Fuketa, M. Hashimoto, Y. Mitsuyama, and T. Onoye, "Adaptive performance compensation with in-situ timing error prediction for subthreshold circuits," in Proc. Custom Integr. Circuits Conf. (CICC), 2009, pp. 215–218.

10.22214/IJRASET

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)