IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 9 Issue: IV Month of publication: April 2021

DOI: https://doi.org/10.22214/ijraset.2021.33857

www.ijraset.com

Call: 🕥 08813907089 🔰 E-mail ID: ijraset@gmail.com

## Low Latency Corrective Feedback Algorithm for Binary Compressed Sensing

Santhiya. A<sup>1</sup>, Nandhini. T<sup>2</sup>, Soundarya. V<sup>3</sup>, Sowmya. B<sup>4</sup>

<sup>1</sup>Assistant professor, <sup>2, 3, 4</sup> UG Students, Electronics and Communication Engineering, Jeppiaar Engineering College, Tamil Nadu, India.

Abstract: Compressed sensing takes advantage of the redundancy in many interesting signals. Compressed sensing typically starts with taking a weighted linear combination of samples also called compressive measurements in a basis different from the basis in which the signal is known to be sparse. In the existing system, low density parity check codes are used for the process of predicting the compressed sensing scheme through metric matching. The proposed architectures offer high frequency of operation and low reconstruction time when compared to the state-of-the-art designs. Specifically, the 65-nm ASIC realization operates at a maximum frequency of 500 and 666.67 MHz and offer a reconstruction time of 6.3 and 4.7 ns, respectively, for a 64  $\times$  256 deterministic measurement matrix. In the proposed system, design of low latency corrective feedback algorithm (LLCF) is developed. The algorithm is focused on correcting the binary dead codes and utilizes it to self-repair through a corrective iteration process. The system, performs better compared to the existing interval passing algorithm in terms of latency. These codes are encrypted through LDPC encoder. The proposed system is simulated in MODELSIM and implemented in XILINX ISE.

Keywords: Compressed sensing, low density parity check, interval passing algorithm, modelsim, Xilinx ISE

#### I. INTRODUCTION

Compressed sensing (CS) has drawn considerable attention in recent years. Introduced by Donoho, it is a technique for reconstructing sparse signals from a small set of measurements. Let  $x \in RN$  be a K-sparse signal with at most K nonzero entries, K, N. Let  $A \in RM \times N$  be a measurement matrix which maps x into a smaller measurement vector  $y \in RM$  as given by the following equation: y = Ax. One method of recovering x from y is to find x with the smallest l0-norm, which is a NP-hard technique. Another method is to find x with the smallest 11-norm. The 11- norm minimization based on linear programming (LP) for CS, called basis pursuit (BP), has an excellent performance in the recovery of the sparse signals. The high complexity of BP makes it impractical when the matrix dimension is large. There exist relatively less complex greedy algorithms such as orthogonal matching pursuit (OMP), CoSaMP, iterative hard thresholding (IHT) which iteratively compute an approximation to the original signal. Several hardware realizations of OMP have been reported in the literature, which exhibit trade off between complexity and accuracy.

#### II. EXISTING SYSTEM

In the existing system, low density parity check codes are used for the process of predicting the compressed sensing scheme through metric matching. The proposed architectures offer high frequency of operation and low reconstruction time when compared to the state-of-the-art designs. Specifically, the 65-nm ASIC realization operates at a maximum frequency of 500 and 666.67 MHz and offer a reconstruction time of 6.3 and 4.7 ns, respectively, for a  $64 \times 256$  deterministic measurement matrix.

- A. Drawbacks of Existing System

- 1) Processing delay is more.

- 2) Complex steps involved.

#### **III. PROPOSED SYSTEM**

The algorithm focuses on correcting the binary dead codes and utilizes it to self-repair through a corrective iteration process. The system performs better comparing to the existing interval passing algorithm in terms of latency. These codes are encrypted through LDPC encoder. The proposed system is simulated in MODELSIM and implemented in XILINX ISE.

- 1) Advantages of proposed system

- 2) Low Latency and Low Complexity

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 9 Issue IV Apr 2021- Available at www.ijraset.com

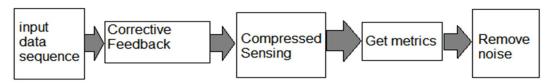

A. Block Diagram of Proposed System

Figure 1: Concept of the Proposed system

The input data sequence is provided and the corrective feedback mechanism corrects the incoming signals and based on the sparsity of the signal, only a portion of the signal is concentrated. The signal is encoded using the Low Density Parity Check mechanism and sent for compressed sensing. After the signal is compressed, and the performance measurement of the signal is measured using get metrics. Then finally, the noise is removed from the signal. This process is explained in the figure 1. Let x=[x1, x2, ..., xn] be a k-sparse signal with k non zero entries k<<N. In BCS, each entry xi of vector x is binary valued, that is xi belongs to  $\{0,1\}$ . The sparsity of the given signals are checked. For each sparsity atleast 100 random signals are generated and 50 reconstruction iterations takes place.

#### IV. RESULTS AND DISCUSSION

The software that is used in the project is mainly Modelsim 6.3G altera and Xilinx ise.

A. Creation And Simulation Of Attack Files

The attack files are programmed and executed in modelsim. After the computation and execution of these attack files, they are dumped into the hardware for further operations. Two attack files are coded namely,

- 1) Linear attack

- 2) Differential attack

Are shown in the figure 3. Similarly the proposed system files are also created and simulated as shown in the figure 4.

| Name                          | Date modified    | Туре | Size |

|-------------------------------|------------------|------|------|

| 🬷 Differential_Attack         | 29-03-2021 02:58 | vhd  | 1 KB |

| Untegration_lpa_Existing      | 25-03-2021 21:39 | vhd  | 2 KB |

| Unitegration_lpa_Existing.vhd | 25-03-2021 21:39 | bak  | 2 KB |

| UinearApprox_Ex               | 25-03-2021 21:39 | vhd  | 1 KB |

#### Figure 3 Attack files

| lame                           | Date modified    | Туре | Size |

|--------------------------------|------------------|------|------|

| 🖲 enc_mod                      | 05-01-2015 14:51 | vhd  | 5 KB |

| b integration_lpa_proposed.vhd | 17-03-2021 11:31 | bak  | 1 KB |

| b main_mod                     | 17-03-2021 11:29 | vhd  | 3 KB |

| b main_mod.vhd                 | 30-10-2011 15:01 | bak  | 3 KB |

| 🐻 mem_mod                      | 30-10-2011 18:54 | vhd  | 4 KB |

| ProposedStrobing               | 14-03-2020 09:13 | vhd  | 2 KB |

| ProposedStrobing_Config        | 14-03-2020 09:22 | vhd  | 2 KB |

| ProposedStrobing_partial       | 17-03-2021 11:45 | vhd  | 2 KB |

| ProposedStrobing_partial.vhd   | 14-03-2020 09:13 | bak  | 2 KB |

| test_dec_mod                   | 20-11-2014 08:01 | vhd  | 8 KB |

#### Figure 4 Proposed system files

The hardware used in this project is XILINX-XC9572XL based CPLD trainer kit is shown in the figure 5.

Figure 5 XILINX - XC9572XL based CPLD trainer kit

The proposed VLSI architectures of IPA and LLCF algorithms are implemented both in ASIC and FPGA environments. Since there are no prior implementation for BCS in the literature, we compare the proposed designs with implementations of OMP from the literature. The sparsity of an LDPC matrix which is equal to 64. The results are compared with those of some instances of existing related architecture. The computations involved are all integer operations and the hardware consumption of the proposed designs independent of the sparsity level K unlike OMP. Since the proposed architecture is fully parallel, each iteration takes a single clock cycle. So, the number of clock cycles the design takes to reconstruct the signal is equal to the number of iterations. The waveform of the existing method with the IPA algorithm is being synthesized. Thus this output is result of the existing method have less accuracy and require more time. Thus, the waveform of the binary compressed sensing has been synthesized with the help of the MIPA the time efficient and less complex result have been obtained.

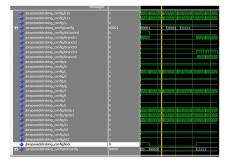

Thus from the below given figures 6 and 7 it can be inferred that the time interval of the waveforms in the proposed system signals are significantly reduced when compared with the existing system signal.

| Messages                                   |   |                                                                                                                 |

|--------------------------------------------|---|-----------------------------------------------------------------------------------------------------------------|

| /inearapprox_ex/1                          | 1 | ուստուսիսուստուվուստուսիսուստուսիս                                                                              |

| /inearapprox_ex/l3                         | 1 |                                                                                                                 |

| /inearapprox_ex/i6 /inearapprox_ex/i7      | 1 |                                                                                                                 |

| /inearapprox_ex/k1                         | 1 |                                                                                                                 |

| /inearapprox_ex/k2 /inearapprox_ex/k3      | 1 |                                                                                                                 |

| /inearapprox_ex/k4                         | 1 |                                                                                                                 |

| /inearapprox_ex/k5 /inearapprox_ex/k6      | 1 |                                                                                                                 |

| /inearapprox_ex/y1                         | 0 |                                                                                                                 |

| /inearapprox_ex/y2                         | 1 |                                                                                                                 |

| /inearapprox_ex/g24 /inearapprox_ex/g25    | 0 |                                                                                                                 |

| /inearapprox_ex/g26                        | 0 |                                                                                                                 |

| /inearapprox_ex/g27                        | 1 |                                                                                                                 |

| /inearapprox_ex/g29                        | 0 |                                                                                                                 |

| /inearapprox_ex/g30<br>/inearapprox_ex/g31 | 1 | טרברא הרביה הרביה הרבינים הרביו הרביו הרביו הרביו הרבים ה |

| /inearapprox_ex/g10                        | 1 |                                                                                                                 |

| /inearapprox_ex/g11 /inearapprox_ex/g19    | 0 |                                                                                                                 |

| /inearapprox_ex/g16                        | 1 |                                                                                                                 |

|                                            |   |                                                                                                                 |

Figure 6 Result waveform of existing system

Figure 7 Result waveform of proposed system

#### V. CONCLUSION

VLSI architecture to realize IPA for BCS has been proposed. The algorithm is further modified to reduce its complexity for which VLSI architecture has been developed. The recovery performance of the proposed MIPA algorithm has been demonstrated on a standard LDPC measurement matrix. The proposed designs are implemented on both ASIC and FPGA platforms, demonstrating their high frequency of operation and low reconstruction.

#### REFERENCES

- [1] D. L. Donoho, "Compressed sensing," in IEEE Transactions on Information Theory, vol. 52, no. 4, pp. 1289-1306, April 2006, doi: 10.1109/TIT.2006.871582.

- [2] R. Gallager, "Low-density parity-check codes," in IRE Transactions on Information Theory, vol. 8, no. 1, pp. 21-28, January 1962, doi: 10.1109/TIT.1962.1057683.

- [3] V. Ravanmehr, L. Danjean, B. Vasić and D. Declercq, "Signal recovery performance of the interval-passing algorithm," 2012 7th International Symposium on Turbo Codes and Iterative Information Processing (ISTC), Gothenburg, Sweden, 2012, pp. 106-110, doi: 10.1109/ISTC.2012.6325208.

- [4] T. B. Alakus, R. Das and I. Turkoglu, "An Overview of Quality Metrics Used in Estimating Software Faults," 2019 International Artificial Intelligence and Data Processing Symposium (IDAP), Malatya, Turkey, 2019, pp. 1-6, doi: 10.1109/IDAP.2019.8875925.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 9 Issue IV Apr 2021- Available at www.ijraset.com

- [5] S. Lee, K. Kwon and I. Park, "Pipelined Cartesian-to-Polar Coordinate Conversion Based on SRT Division," *in IEEE Trans. on Circuits and Systems II: Express Briefs*, vol. 54, no. 8, pp. 680-684, Aug. 2007.

- [6] A. G. Dimakis and P. O. Vontobel, "LP decoding meets LP decoding: A connection between channel coding and compressed sensing," 2009 47th Annual Allerton Conf. on Communication, Control, and Computing (Allerton), Monticello, IL, USA, 2009, pp. 8-15.

- [7] A. G. Dimakis, R. Smarandache and P. O. Vontobel, "LDPC Codes for Compressed Sensing," *in IEEE Transactions on Information Theory*, vol. 58, no. 5, pp. 3093-3114, May 2012.

- [8] D. Bickson, D. Baron, A. Ihler, H. Avissar and D. Dolev, "Fault Identification Via Nonparametric Belief Propagation," *in IEEE Transactions on Signal Processing*, vol. 59, no. 6, pp. 2602-2613, June 2011.

- [9] L. Bai, P. Maechler, M. Muehlberghuber and H. Kaeslin, "High-speed compressed sensing reconstruction on FPGA using OMP and AMP," 2012 19th IEEE International Conference on Electronics, Circuits, and Systems (ICECS 2012), Seville, Spain, 2012, pp. 53-56.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)