IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 9 Issue: VIII Month of publication: August 2021 DOI: https://doi.org/10.22214/ijraset.2021.37697

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

# A 129-level Asymmetrical Cascaded H-Bridge Multilevel Inverter with Reduced Switches and Low THD

Manoj H P<sup>1</sup>, T N Raghavendra<sup>2</sup>

<sup>1</sup> PG Scholar, <sup>2</sup>Assistant Professor, Department of Electrical Engineering, University Visveswaraya College of Engineering, Bangalore, Karnataka, India

Abstract: The multilevel inverter is a power conversion device which is uses multiple dc sources to provide required alternating current level. It is can be used for medium to high power applications. This paper presents a 129 level asymmetrical cascaded H-bridge multilevel inverter with reduced switching components and higher THD. The proposed inverter uses multiple dc sources with voltage ratio 1:1:2:4:8:16:32. The proposed inverter uses voltage reference technique to control the switching components of the topology. The comparative analysis of 129 level ASCHBMLI and conventional inverter topologies have been presented. The main advantages of the proposed topology is lower switching components, lower losses, and lower THD without the need of filter. MATLAB/SIMULINK software is used to perform simulation and analyse the performance of the proposed topology. Keywords: Multilevel Inverter (MLI), Asymmetrical Cascaded H Bridge Multilevel Inverter (ASCHBMLI), Cascaded H Bridge (CHB), MATLAB, Total Harmonic Distortion (THD).

#### I. INTRODUCTION

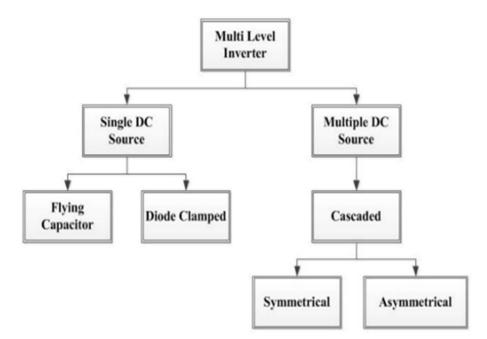

The basic function of Inverters is to convert DC electricity to AC electricity, for uses in either stand-alone systems or to connect dc source to AC grid. The Multilevel inverters are power electronic method to generate multiple level AC voltages from multiple medium voltage, dc sources. The multilevel inverters were first invented in 1979, as a three level MLI. It gained popularity due its high-power capability and lower THD, lower electromagnetic interference. Due its vast applications, including FACTS drives, VAR control, HVDC, renewable systems etc., MLIs are popular. today more commercial products are based on MLIs. Thus, there is increased efforts in developing multilevel inverters by changing its topology to obtain superior performance, decreased switching losses, lower THD, lower components requirement etc. There are several topologies having distinctive features. Fig.1 shows different multilevel topologies.

The Multilevel inverters are classified into 3 basic types:

- A. Diode clamped multilevel inverter

- B. Flying capacitor multilevel inverter

- C. Cascaded multilevel inverter

The diode-clamped multilevel inverter consists of clamping diode to generate multiple voltage levels through different phases to the capacitors which are connected in series. It requires (n-1) main dc link capacitors and (n-1)(n-2) diodes, where 'n' is number of levels required. Some of the advantages of Diode clamped multilevel inverter are that it has high efficiency for fundamental frequency, it can be used for high voltage back-to-back inter-connection or an adjustable speed drive. However, diode clamped MLI suffers from various limitations.

The maximum output voltage obtained is limited to one half of input DC voltage. The number of diodes required is quadratically equal to number of levels, thus it requires a large number of diodes to generate high number of levels, disturbed charge balance for more than three levels etc.

The Flying capacitor (FC) topology uses a large number of capacitors of equal value. The topology requires a total number of (n-1)(n-1)/2 capacitors per phase and (n-1) main bus capacitors. The main advantage of the Flying capacitor topology is that the phase redundancy is achievable for balancing voltage levels of capacitors.

The flying capacitor topology suffers from high switching losses, limited output voltage, requirement of large number of capacitors, complex start-up etc.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 9 Issue VIII Aug 2021- Available at www.ijraset.com

Fig.1 Basic Classification of Multilevel Inverter

The H-bridge topology derives its name from graphical representation of the circuit. A H-bridge consist of four active switches that can give positive, zero or negative polarity outputs to load depending on the switching conditions given to the switches. The cascaded H Bridge MLI consists of multiple DC sources and it is manipulated for various renewable energy sources like photovoltaic, fuel, biomass, etc. soft switching is employed to avoid bulky resistor-capacitor combinations. The advantages of this topology is modular design which makes the manufacturing of inverter, quicker and cheaper than other alternatives. The Cascaded H-Bridge inverters (CHB) are further classified into two categories. Symmetrical CHBMLI uses de sources of equal magnitude (1:1:1:1:1:1:1). Hence it requires more de sources to get higher levels. Asymmetrical CHBMLI uses de sources of unequal magnitude in the order of (1:1:2:4:8:16:32). It allows synthesis of higher output voltage level with same number of sources as compared to symmetrical CHBs. The major advantage of ASCHBMLI is its ability to create higher voltage levels by using lesser number of DC sources.

The proposed topology uses 7 dc sources with dc source voltage ratio of 1:1:2:4:8:16:32 and uses voltage reference switching technique is used generate 129 level AC voltage. The design, simulation, and performance are analyzed and presented.

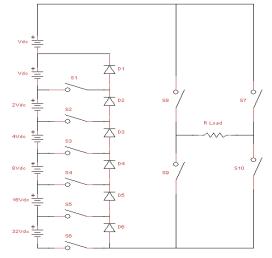

#### A. Schematic Diagram of Proposed Topology

#### II. PROPOSED TOPOLOGY

In conventional MLI topology, the number of levels depends on number of dc sources. In the proposed topology, high level voltage output can be obtained keeping number of dc sources required low. The schematic diagram of the proposed 129 level ASCHBMLI is shown in the Fig 1. The proposed topology consists of fourteen switches, five dc sources. The switches can be MOSFET or IGBT power semiconductor devices.

The proposed topology consists of two parts, a h bridge circuit and a level switching circuit. The H-bridge circuit functions as a polarity changing circuit. It changes polarity for every half cycle. In the Fig 1, the switches S7, S8, S9, S10 make up h-bridge circuit. To get positive polarity, S7, S9 are switched on together while S8, S10 are turned off. To get negative polarity, S7, S9 are switched off and S8, S10 are on. The switches, S1, S2, S3, S4, S5, S6 make up level generating circuit. This circuit generates multiple dc output voltage levels based on switching sequences. The switching sequence is generated by a switching control unit which uses voltage reference switching technique to generate switching pulses,

There are 129 different operating modes to generate 129 different output voltage levels for the proposed 129 level ASCHBMLI topology.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 9 Issue VIII Aug 2021- Available at www.ijraset.com

Fig 2. Proposed single phase 129 level ASCHBMLI topology

#### B. Comparative Analysis Of Proposed Inverter With Other Topologies

The comparative analysis of different topologies with the proposed topology is given in the table 1. The different parameters compared are number of switches, dc sources, capacitors, diodes. Where, n is the number of levels

| THELE I. Companison of anterent topologies. |            |              |         |                |  |  |  |  |  |

|---------------------------------------------|------------|--------------|---------|----------------|--|--|--|--|--|

| Inverter                                    | NPC        | FC           | CHB     | Proposed       |  |  |  |  |  |

| Topologies                                  |            |              |         | Topology       |  |  |  |  |  |

| Number of                                   | n          | n            | n       | n              |  |  |  |  |  |

| levels                                      |            |              |         |                |  |  |  |  |  |

| Number of DC                                | 1          | 1            | (n-1)/2 | $log_2(n-1)$   |  |  |  |  |  |

| sources                                     |            |              |         |                |  |  |  |  |  |

| Number of                                   | 2(n-1)     | 2(n-1)       | 2(n-1)  | $log_2(n-1)+3$ |  |  |  |  |  |

| switches                                    |            |              |         |                |  |  |  |  |  |

| Number of                                   | (n-2)(n-1) | -            | -       | $log_2(n-1)$   |  |  |  |  |  |

| Diodes                                      |            |              |         |                |  |  |  |  |  |

| Number of                                   | n-1        | (n-2)(n-1)/2 | -       | -              |  |  |  |  |  |

| Capacitors                                  |            |              |         |                |  |  |  |  |  |

TABLE 1: Comparison of different topologies.

From the table 1, it can be proved that proposed topology can generate 129 level output voltage with lesser number of DC sources, capacitors, power diode. The lesser number of components required reduces the switching losses of the system, reduces the system size, and makes the system cheaper.

#### C. Control Strategy

The switching sequence and the obtained voltage levels of the proposed topology is shown in the table 2 and table 3. The switches S1, S2, S3, S4, S5, S6 are controlled to supply different voltage levels and switching sequence for them is given in the table 2 and H-bridge switches S7, S8, S9, S10 are controlled to reverse polarity and its switching sequence is given in table 3. The switching sequence has 64 positive levels, 64 negative levels with only one '0' level in the output.

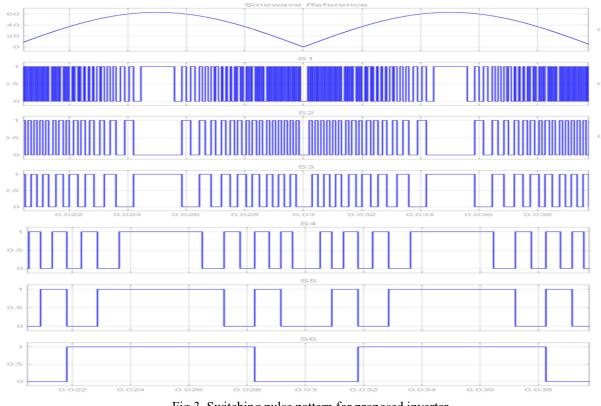

The switching control unit provides gate signals to the switches to control the switching states of the circuit. The control strategy is done by a voltage reference technique. In this technique, switching control unit will change the switching angles by comparing a reference signal, the switching pulses are generated by comparing absolute sine wave with multiple DC offset voltages. The comparator unit compares the absolute sine signal with DC offset values to generate binary values 0 or 1. The comparator outputs are 0, when reference signal is lesser than DC offset and 1, when reference signal is greater than DC offset. If the comparator outputs is 1 at that time, switching angle is achieved.

## International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 9 Issue VIII Aug 2021- Available at www.ijraset.com

| TABLE 2: Switching States for the proposed topology. |                                       |    |    |    |    |    |    |    |    |    |    |          |

|------------------------------------------------------|---------------------------------------|----|----|----|----|----|----|----|----|----|----|----------|

| Switching States                                     |                                       |    |    |    |    |    |    |    |    |    |    |          |

| Output Voltages                                      | Conducting Switches Conducting Diodes |    |    |    |    |    |    |    | 54 |    |    |          |

| (Vo)                                                 | S1                                    | S2 | S3 | S4 | S5 | S6 | D1 | D2 | D3 | D4 | D5 | D6       |

| +/- 64Vdc                                            | 1                                     | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0        |

| +/- 63Vdc                                            | 0                                     | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0        |

| +/- 62Vdc                                            | 1                                     | 0  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0        |

| +/- 61Vdc                                            | 0                                     | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0        |

| +/- 60Vdc                                            | 1                                     | 1  | 0  | 1  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0        |

| +/- 59Vdc                                            | 0                                     | 1  | 0  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 0        |

| +/- 58Vdc                                            | 1                                     | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 0  | 0        |

| +/- 57Vdc                                            | 0                                     | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0        |

| +/- 56Vdc                                            | 1                                     | 1  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 1  | 0  | 0        |

| +/- 55Vdc                                            | 0                                     | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 0  | 1  | 0  | 0        |

| +/- 54Vdc                                            | 1                                     | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 1  | 0  | 0        |

| +/- 53Vdc                                            | 0                                     | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0        |

| +/- 52Vdc                                            | 1                                     | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0        |

| +/- 51Vdc                                            | 0                                     | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 0        |

| +/- 50Vdc                                            | 1                                     | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 0        |

| +/- 49Vdc                                            | 0                                     | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0        |

| +/- 48Vdc                                            | 1                                     | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 1  | 0        |

| +/- 47Vdc                                            | 0                                     | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 1  | 0        |

| +/- 46Vdc                                            | 1                                     | 0  | 1  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0        |

| +/- 45Vdc                                            | 0                                     | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 0  | 1  | 0        |

| +/- 44Vdc                                            | 1                                     | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0        |

| +/- 43Vdc                                            | 0                                     | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 1  | 0        |

| +/- 42Vdc                                            | 1                                     | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 0        |

| +/- 41Vdc                                            | 0                                     | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 0  | 1  | 0        |

| +/- 40Vdc                                            | 1                                     | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 0        |

| +/- 39Vdc                                            | 0                                     | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0        |

| +/- 38Vdc                                            | 1                                     | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0        |

| +/- 37Vdc                                            | 0                                     | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 1  | 0        |

| +/- 36Vdc                                            | 1                                     | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 0        |

| +/- 35Vdc                                            | 0                                     | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 0        |

| +/- 34Vdc                                            | 1                                     | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 0        |

| +/- 33Vdc                                            | 0                                     | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 0        |

| +/- 32Vdc                                            | 1                                     | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1        |

| +/- 31Vdc                                            | 0                                     | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 1        |

| +/- 30Vdc                                            | 1                                     | 0  | 1  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1        |

| +/-29Vdc                                             | 0                                     | 0  | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 1        |

| +/-28Vdc                                             | 1                                     | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | <u>1</u> |

| +/- 27Vdc                                            | 0                                     | -  | 0  | 1  | 1  | 0  |    | 0  | 1  | 0  | 0  | _        |

| +/- 26Vdc                                            | 1                                     | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1        |

| +/-25Vdc                                             | 0                                     | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 0  | 1        |

| +/- 24Vdc                                            | 1                                     | 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1        |

| +/- 23Vdc                                            | 0                                     | 1  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1        |

| +/- 22Vdc                                            | 1                                     | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1        |

| +/-21Vdc                                             | 0                                     | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 1        |

| +/- 20Vdc                                            | 1                                     | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 1        |

| +/- 19Vdc                                            | 0                                     | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 1        |

| +/- 18Vdc                                            | 1                                     | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 1        |

| +/- 17Vdc                                            | 0                                     | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 0  | 1        |

#### TABLE 2: Switching States for the proposed topology.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 9 Issue VIII Aug 2021- Available at www.ijraset.com

| +/- 16Vdc | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

|-----------|---|---|---|---|---|---|---|---|---|---|---|---|

| +/- 15Vdc | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| +/- 14Vdc | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 |

| +/- 13Vdc | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| +/- 12Vdc | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

| +/- 11Vdc | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 |

| +/- 10Vdc | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 |

| +/- 9Vdc  | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 |

| +/- 8Vdc  | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

| +/- 7Vdc  | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 |

| +/- 6Vdc  | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 |

| +/- 5Vdc  | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 |

| +/- 4Vdc  | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| +/- 3Vdc  | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 |

| +/- 2Vdc  | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| +/- 1Vdc  | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0Vdc      | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

TABLE 3: Switching States for polarity changing h-bridge inverter

| Voltage  | Conducting Switches |            |    |     |  |  |  |  |  |  |

|----------|---------------------|------------|----|-----|--|--|--|--|--|--|

| Polarity | <b>S</b> 7          | <b>S</b> 8 | S9 | S10 |  |  |  |  |  |  |

| Positive | 1                   | 0          | 1  | 0   |  |  |  |  |  |  |

| Negative | 0                   | 1          | 0  | 1   |  |  |  |  |  |  |

The switching pulses for the operation of proposed 129 level ASCHBMLI is given the Fig 3

Fig 3. Switching pulse pattern for proposed inverter

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429

Volume 9 Issue VIII Aug 2021- Available at www.ijraset.com

#### **III.SIMULATION AND RESULTS**

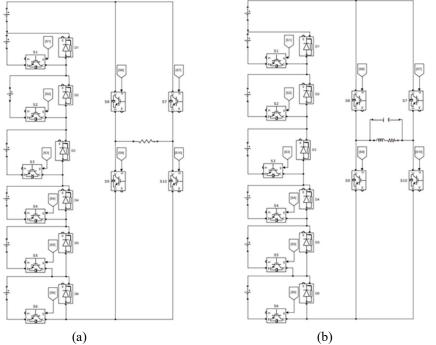

The proposed topology is simulated in MATLAB/SIMULINK software, and performance of the topology in different loading conditions is studied in simulation of topology. Fig 4. shows Simulink model. The output voltage and current waveforms, value of THD and output power is measured. The value of different dc voltage sources are chosen in the ratio of 1:1:2:4:8:16:32 and the value of resistor during resistive load condition is  $45\Omega$  and during RL loads, the resistors and inductors are  $45\Omega$  and 10mH respectively.

Fig 4. Simulink model of the 129 level Multilevel inverter for (a) R Load (b) RL Load

The DC sources in the simulation are of voltage magnitude 5Vdc, 10Vdc, 20Vdc, 40Vdc, 80Vdc, 160Vdc. The inverter generates output voltage of maximum voltage magnitude of 310V and minimum voltage magnitude of -310V. The switches used are IGBT which have fundamental operating switching frequency of 50 Hz. A capacitor of  $1.2\mu$ F is connected in parallel to RL load to reduce the spikes.

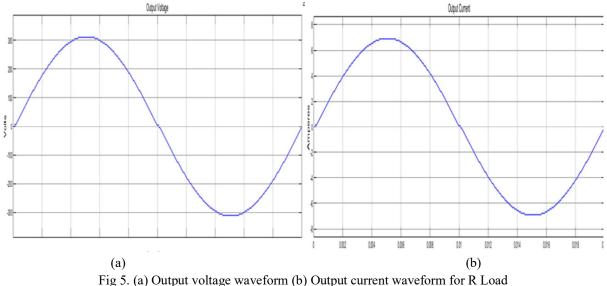

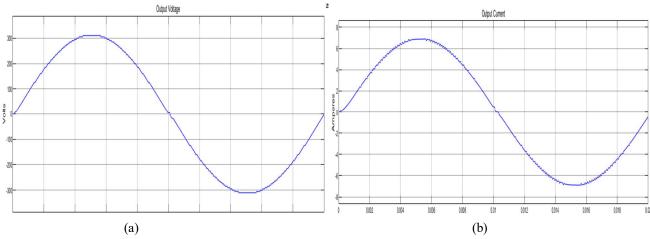

The output waveform of 129 level inverter for R Load and R-L Load is given in the Fig 5 and Fig 6 respectively. The peak positive output current is found to be 6.88 A for R load and R-L load.

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 9 Issue VIII Aug 2021- Available at www.ijraset.com

Fig 6. (a) Output voltage waveforms (b) Output current waveforms for R-L Load

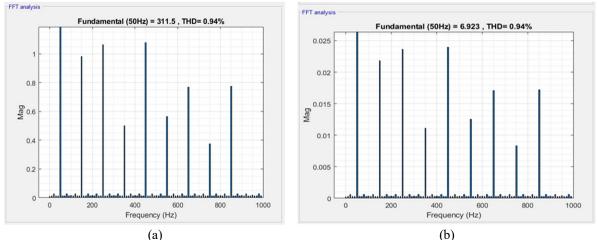

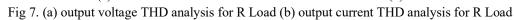

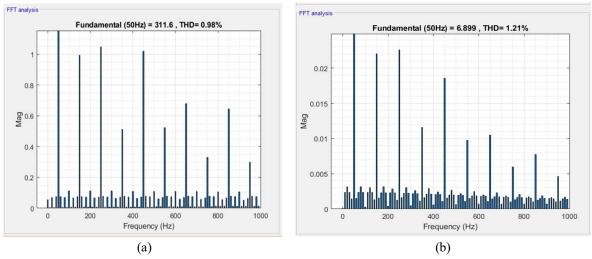

The Fast Fourier Transfer Function (FFT) is used to calculate the Total Harmonic Distortion of the proposed converter for different loads. The FFT analysis is done for output voltage waveform and current waveform.

Fig 8. (a) output voltage THD analysis for RL Load (b) output THD analysis for RL Load

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.429 Volume 9 Issue VIII Aug 2021- Available at www.ijraset.com

#### **IV.CONCLUSION**

The simplified and reduced component cascaded H bridge inverter topology is proposed. The topology produces 129 level output voltage using less switches and lower THD value. The proposed topology has THD value of 0.94 % for voltage waveforms for R load and 0.98% for RL Load which is very less and within IEEE standards. For output currents, the FFT analysis gives THD values of 0.94 % and 1.21 % for R and RL loads respectively. The proposed inverter has output power measured to be 1072W. Due to low THD values and good power capacity, the proposed inverter is suitable for medium to high voltage applications.

#### REFERENCES

- Kamaldeep Arjun Tyagi, Himanshu "A New Multilevel Inverter Topology with Minimal Power Electronics Component" 3rd International Conference on Recent Developments in Control, Automation & Power Engineering (RDCAPE), 978-1-7281-2068-3/19/\$31.00 ©2019 IEEE pp-687-692, 2019

- [2] Ponkumar, S.; Rivera, M.; Kamroon, F.; Kumar, S.G. "Realization of cascaded multilevel inverter". In Proceedings of the 2017 CHILEAN Conference on Electrical, Electronics Engineering, Information and Communication Technologies (CHILECON), Pucon, Chile, 18–20 October 2017; pp-1–7.

- [3] Chacko S. and Thomas J., "THD analysis of multilevel inverter with different loads, International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineerin"g. Vol-3,No-5,pp-200-201.

- Gautam Shivam Prakash, "Novel H-bridge Based Topology of Multilevel Inverter with Reduced Number of Devices", IEEE Journal of Emerging and Selected Topics in Power Electronics, 10.1109/JESTPE.2018.2881769, pp-1-10.2018

- [5] M. Vijayakumar, S. M. Ramesh, "Component Count Reduced, Filter less H-Bridge Multilevel Inverter with Series and Parallel Connected Switches", Journal of Circuits, Systems and Computers, doi:10.1142/S0218126621500523 pp-1-38.

- [6] Malinowski M.. "Recent advances and industrial applications of multilevel converters, IEEE Transactions on industrial electronics", Vol.57, No.8, pp- 2553-2580. 2010

- Saqib Hayat, Shahzada Sufyan Syed, S. Subhan Syed, Saqib Shabbir, "63-level Reduce Switch Asymmetrical Cascaded H Bridge Multilevel Inverter", 978-1-7281-9893-4/20/2020 IEEE. 2020

- [8] P.Ganesh., N. Shanmugavadivu., Dr.K.R.Shantha.,, "Single-Phase 63-Level Modular Multilevel Inverter fed Induction Motor Drive for Solar PV Applications 4th International Conference on Electrical Energy Systems (ICEES)" 978-1-5386-3695-4 2018 IEEE pp- 596-604. 2018

- [9] Ezzidin Hassan Elmabrouk Aboadla1, Sheroz Khan2, Mohamed Hadi Habaebi, Teddy Gunawan, Belal Ahmed Hamidah, Majdee Tohtayong,, "Selective Harmonics Elimination Technique in Single Phase Unipolar H-Bridge Inverter", proceedings of 2016 IEEE Student Conference on Research and Development (SCOReD) 10.1109/SCORED.2016.7810057, p-11-14. 2016

- [10] J.Gowri Shankar, Dr.J.Belwin Edward, "Design and Implementation of 15-Level Asymmetric Cascaded H Bridge Multilevel Inverter", Journal of Electrical Engineering. 17. Pp- 396-404.2018

- [11] Sarbojit Mukherjee, Sayan De, Santomit Sanyal, Suman Das, Sumit Saha,, "A 15-level asymmetric H-bridge multilevel inverter using d-SPACE with PDPWM technique, International Journal of Engineering, Science and Technology", Vol. 11, No. 24 1, pp. 22-33. 2019

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)