# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 4 Issue: II Month of publication: February 2016

DOI:

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

Volume 4 Issue II, February 2016 ISSN: 2321-9653

www.ijraset.com Volume IC Value: 13.98 ISSN: 2

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

# Comparison of Driver-Interconnect-Load System with Doped and Neutral Graphene Nano-Ribbon in Nano Scale Regime

Praggya Agnihotry<sup>#1</sup>, Shailendra Mishra<sup>\*2</sup>, R.P.Agarwal<sup>#3</sup>

\*\*ECE Department, Shobhit University, Meerut

Abstract— In the progressively growing VLSI area graphene nano-ribbon interconnects are widely used by scientists for interconnection purpose in VLSI/ULSI chips. In the work which has been presented in this paper graphene nano-ribbon (GNR) interconnects with multi layers have been used to find out the propagation delay of a Driver-Interconnect-Load system. Two forms of graphene nano-ribbon have been used for the study such as multi layer graphene nano-ribbon (MLGNR) with doping and MLGNR without doping (neutral). The study has been done beyond 16 nm and comparison has been made with the result of 16 nm technology node. TSPICE software has been used to obtain results.

Keywords— Driver-interconnect-load system, FinFET, Interconnect, Multi layer Graphene nano-ribbon, Propagation delay.

#### I. INTRODUCTION

In recent technology culture graphene nano-ribbon has been observed as a good candidate for making interconnects due to its properties [1][2][3][4] and large mean free path [5] and also can be used in many other applications [6]. Researchers have already started their work in the direction of graphene and its applications [7]. The performance of graphene interconnect can be enhanced by doping and study on this aspect has already been done by many researchers [8][9]. In this paper effect of doping on propagation delay of a driver-interconnect-load system (DIL) using graphene interconnect has been studied and compared with the performance of driver-interconnect-load system with neutral multi layer graphene nano-ribbon (MLGNR) interconnect beyond 16 nm and also the improvement in delay has been studied over the values of propagation delay obtained by Agnihotry in [16] at 16 nm.

The MLGNR is doped with AsF5 in order to increase its conductivity [10] and this is due to the fact that by doping density of carriers increases which makes mean free path more than that of neutral MLGNR, also spacing between the GNR layer increases due to doping [10][11]. By making the specular edges of GNR conductance can also be increased but the work in this paper is showing the study of propagation delay of a DIL system by only considering doped MLGNR interconnect.

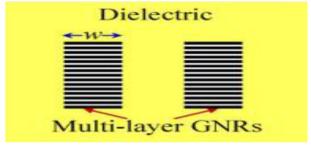

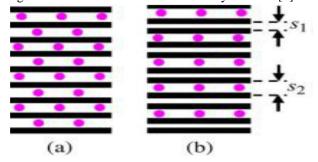

Fig. 1 Schematic view of neutral multilayer GNRs [9].

Fig. 2 Schematic view of two types of intercalated GNR [12].

www.ijraset.com IC Value: 13.98

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

#### II. DRIVER-INTERCONNECT-LOAD (DIL) SYSTEM

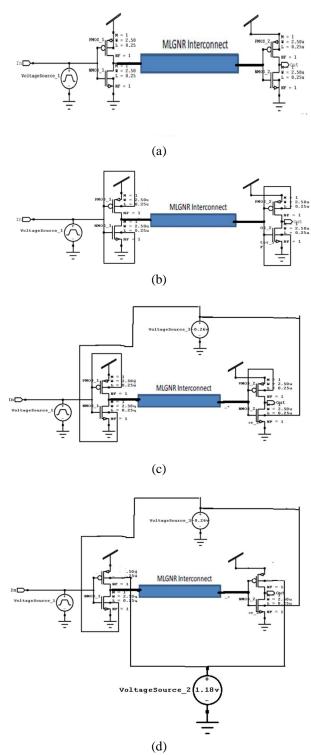

This work has used four DIL systems which are shown in Figure 3. Figure 3 (a) is showing the DIL system which comprises of CMOS driver and load stages, (b), (c), and (d) DIL system carries short gate (SG), independent gate (IG), and low power (LP) FinFET as driver and load stages.

Fig. 3 Driver-interconnect-load system using (a) CMOS driver-load (b) SG FinFET driver-load (c) IG FinFET driver-load (d) LP FinFET driver-load.

Volume 4 Issue II, February 2016 ISSN: 2321-9653

www.ijraset.com Volum IC Value: 13.98 ISSN:

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

In SG FinFET the front and back gates of PMOS and NMOS transistors are connected with each other, in IG FinFET (n-type) front and back gates of PMOS transistor are short with each other and back gate of NMOS transistor is providing with another voltage source, and for LP FinFET both gates are provided with a different potentials in the case of PMOS and NMOS transistors [13].

Doped and neutral MLGNR has been used in this work, and for a doped MLGNR EF = 0.6eV, inter layer spacing 0.575 nm, and mean free path  $1.03~\mu m$  [14][8] has been taken and for a neutral MLGNR EF = 0.1eV, inter layer spacing 0.34 nm, and mean free path  $0.4~\mu m$  has been taken[15][8][18]. The study has been done in three operating regions such as super threshold region, near threshold region, and sub threshold region[16][19][20].

#### III.RESULT AND DISCUSSION

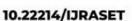

The set up which has been used for simulation is a DIL system shown in Figure 3. Performance characteristic of DIL system in terms of propagation delay has been studied with the variation of length ( $100\mu m$ ,  $200\mu m$ ,  $_{-}$ ,  $1000\mu m$ ) and width (10nm, 20nm,  $_{-}$ , 50nm) of MLGNR. The effect has also been noticed for different number of devices connected in parallel.

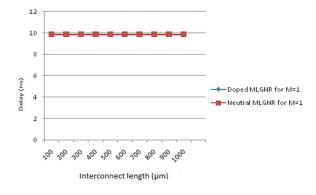

Figure 4 shows the delay variation with respect to the length of the interconnect. In [16] Agnihotry has shown the effect of propagation delay for doped and neutral MLGNR at 16 nm technology node and concluded that at 16 nm doped MLGNR has less delay as compared to neutral MLGNR.

During my research work it has been found that the DIL systems shown in Figure 3 practically performed similar in terms of propagation delay. Therefore graphs which are shown in this paper are similar for every DIL system which has been considered in the work.

Figure 5 shows delay variation with the variation of width and it has shown that delay will decrease with the variation of width. From the study it is also clear that delay will not change its value with length as well as with width in near threshold and sub threshold regions.

www.ijraset.com IC Value: 13.98

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig. 4 Comparison of doped and neutral MLGNR in (a) super threshold region, (b) near threshold region, and (c) sub threshold region for GNR layer = 3.

(c)

Fig.5 Delay variation with respect to width of doped and neutral MLGNR in super threshold region for GNR layer = 3.

TABLE 1.

PERCENTAGE IMPROVEMENT OF PROPAGATION DELAY OF DIL SYSTEM BEYOND 16 NM OVER 16 NM NODE FOR GNR LAYERS =3

| % improvement of delay at GNR layer = 3 |                                                 |       |       |                                                     |       |       |  |

|-----------------------------------------|-------------------------------------------------|-------|-------|-----------------------------------------------------|-------|-------|--|

|                                         | Doped MLGNR beyond 16 nm vs doped MLGNR at 16nm |       |       | Neutral MLGNR beyond 16 nm vs Neutral MLGNR at 16nm |       |       |  |

|                                         | M=1                                             | M=3   | M=6   | M=1                                                 | M=3   | M=6   |  |

| CMOS DIL                                | 99.53                                           | 99.62 | 99.67 | 99.57                                               | 99.51 | 99.57 |  |

| SG FinFET DIL                           | 99.38                                           | 99.62 | 99.64 | 99.47                                               | 99.51 | 99.57 |  |

| IG FinFET DIL                           | 99.77                                           | 99.73 | 99.69 | 99.75                                               | 99.65 | 99.60 |  |

| LP FinFET DIL                           | 99.78                                           | 99.74 | 99.74 | 99.76                                               | 99.66 | 99.66 |  |

www.ijraset.com Volume 4 Issue II, February 2016 IC Value: 13.98 ISSN: 2321-9653

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

TABLE 2.

PERCENTAGE IMPROVEMENT OF PROPAGATION DELAY OF DIL SYSTEM BEYOND 16 NM OVER 16 NM NODE FOR GNR LAYERS =10

| % improvement of delay at GNR layer = 10 |                                                 |       |       |                                                     |       |       |  |

|------------------------------------------|-------------------------------------------------|-------|-------|-----------------------------------------------------|-------|-------|--|

|                                          | Doped MLGNR beyond 16 nm vs doped MLGNR at 16nm |       |       | Neutral MLGNR beyond 16 nm vs Neutral MLGNR at 16nm |       |       |  |

|                                          | M=1                                             | M=3   | M=6   | M=1                                                 | M=3   | M=6   |  |

| CMOS DIL                                 | 99.59                                           | 99.64 | 99.73 | 99.53                                               | 99.66 | 99.71 |  |

| SG FinFET DIL                            | 99.46                                           | 99.64 | 99.71 | 99.47                                               | 99.66 | 99.70 |  |

| IG FinFET DIL                            | 99.78                                           | 99.75 | 99.75 | 99.75                                               | 99.76 | 99.73 |  |

| LP FinFET DIL                            | 99.79                                           | 99.75 | 99.78 | 99.78                                               | 99.76 | 99.77 |  |

TABLE 3.

Percentage improvement of propagation delay of DIL system beyond 16 nm over 16 nm node for GNR layers = 20

| % improvement of delay at GNR layer = 20 |                                                 |       |       |                                                     |       |       |  |

|------------------------------------------|-------------------------------------------------|-------|-------|-----------------------------------------------------|-------|-------|--|

|                                          | Doped MLGNR beyond 16 nm vs doped MLGNR at 16nm |       |       | Neutral MLGNR beyond 16 nm vs Neutral MLGNR at 16nm |       |       |  |

|                                          | M=1                                             | M=3   | M=6   | M=1                                                 | M=3   | M=6   |  |

| CMOS DIL                                 | 99.59                                           | 99.65 | 99.61 | 99.58                                               | 99.66 | 99.57 |  |

| SG FinFET DIL                            | 99.46                                           | 99.65 | 99.61 | 99.52                                               | 99.66 | 99.57 |  |

| IG FinFET DIL                            | 99.78                                           | 99.76 | 99.76 | 99.76                                               | 99.76 | 99.74 |  |

| LP FinFET DIL                            | 99.79                                           | 99.76 | 99.78 | 99.80                                               | 99.76 | 99.75 |  |

#### **IV.CONCLUSIONS**

Study of driver-interconnect-load (DIL) system along with multi layer graphene nano-ribbon interconnect has been studied and it has been concluded that when doped multi layer graphene nano-ribbon (MLGNR) interconnect has been used in the driver-interconnect-load system the speed is much better than the DIL system using neutral multi layer graphene nano-ribbon interconnect. This paper also presents the improvement of propagation delay of doped and neutral MLGNR beyond 16 nm over at 16 nm

www.ijraset.com Volume 4 Issue II, February 2016 IC Value: 13.98 ISSN: 2321-9653

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

technology from which it has been concluded that the overall performance of the system under test shows better results when used beyond 16 nm.

Also the calculated value of propagation delay has not shown any change with respect to length and width in near threshold and sub threshold region. The numbers of graphene layers which have been used in the work are 3, 10, and 20. And the performance of DIL system for large number of layers is better than the DIL system using multi layer GNR of less number of layers [17].

Therefore from the overall results the main thing which can be concluded here is that for the VLSI/ULSI circuits doped multi layer graphene nano-ribbon interconnect is a very good candidate for interconnection purpose.

#### V. ACKNOWLEDGMENT

This work has been performed within the research programe in Shobhit University, Meerut. I am very thankful to Prof.(Dr) R.P.Agarwal for being my research guide.

#### **REFERENCES**

- [1] T.J Echtermeyer, M.C Lemme, M. Baus, B.N Szafranek, A.K Geim, and H. Kurz, Nonvolatile Switching in Graphene Field-Effect Devices, IEEE Electron Device Lett., 29, 952-954,2008.

- [2] M.C Lemme, T.J Echtermeyer, M. Baus, and H. Kurz, A Graphene Field-Effect Device, IEEE Electron Device Lett., 28, 282-284,2007.

- [3] Y. Ouyang, Y. Yoon, J.K. Fodor, and J. Guo, Comparison of performance limits for graphene nanoribbon and carbon nanotube transistors, Appl. Phys. Lett., 89, 203 107-1–203 107-3,2006.

- [4] L. Gengchiau, N. Neophytos, D.E Nikonov, and M.S. Lundstrom, Performance projections for ballistic graphene nanoribbon field-effect transistors, IEEE Trans. Electron Devices, 54, 677–682, 2007.

- [5] A.K Geim, and K.S Novoselov, The rise of graphene, Nat. Mat., 6,183–191,2007.

- [6] D. Pribat, and Y.H. Lee, Carbon nanotubes and graphene for variousapplications in electronics: competition and synergy, IEEE Technology Time Machine Symposium on Technologies Beyond 2020 (TTM),1-2, 1-3,2011.

- [7] P. Agnihotry, and R.P. Agarwal, Graphene Based Planar VLSI Interconnects, International Journal of Engineering Trends and Technology (IJETT),22, 253-254,2015.

- [8] C. Xu, H. Li, and K. Banerjee, Graphene nano-ribbon (GNR) interconnects: A genuine contender or a delusive dream?, IEDM Tech. Dig.,201–204.2008.

- [9] C.Xu, H. Li, and K. Banerjee, Modeling, analysis, and design of graphene nanoribbon Interconnects. IEEE transactions on electron devices, 56, 1567-1578,2009.

- [10] J.E Fischer and T.E. Thompson, Graphite intercalation compounds. Phys. Today, 31, 36–45,1978.

- [11] L.R. Hanlon, E.R. Falardeau, and J.E. Fischer, Metallic reflectance of AsF5-graphite intercalation compounds, Solid State Commun., 24, 377–381,1977.

- [12] M.S.Dresselhaus and G. Dresselhaus, Intercalation compounds of graphite. Adv. Phys., 51, 1–186,2002.

- [13] P. Mishra, Low-power FinFET Circuit Design and Synthesis under Spatial and Temporal Variations. Ph.D Thesis, Princeton University, New Jersey, United States, 2012.

- [14] N. Srivastava, and K. Banerjee, Interconnect challenges for nanoscale electronic circuits, TMS J. Mater., 56, 30-31,2004.

- [15] M.K.Majumdar, N. Reddy, B.K. Kaushik, and S.K Manhas, Comparison of propagation delay in single and multi-layer graphene nanoribbon interconnects. In 5th International conference on computers and devices for communication (CODEC), ,1-4, 17-19 Dec. 2012.

- [16] P. Agnihotry, and R.P.Agarwal, Effect of Doping of MLGNR on Propagation Delay of a Driver-Interconnect-Load system, Int. Journal of Engineering Research and Applications, 5, 154-156,2015.

- [17] P. Agnihotry, and R.P. Agarwal, Comparative Study of Multi Layer Nano Ribbon in Nano Scale Region, Journal of Multidisciplinary Engineering Science and Technology (JMEST), 2,1558-1561,2015.

- [18] N. Reddy, M.K. Majumdar, B.K. Kaushik, M.K. Manhas, and B. Anand, Dynamic crosstalk effect in multilayer graphene nanoribbon interconnects,In International conference on communication, devices and intelligent systems (CODIS), 472-475, 28-29 Dec. 2012.

- [19] P. Agnihotry, and R.P. Agarwal, Performance Analysis Of CMOS and FinFET Driver With Mlgnr At 16nm. International Journal of Science, Technology & Management, 4, 88-94, 2015.

- [20] P. Agnihotry, and R.P. Agarwal, Simulation of Propagation Delay of Multi and Single Conductor MLGNR in Nano Scale Region, IOSR Journal of VLSI and Signal Processing (IOSR-JVSP), 5, 22-27,2015.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)