IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 4 Issue: VII Month of publication: July 2016 DOI:

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

www.ijraset.com IC Value: 13.98 *Volume 4 Issue VII, July 2016 ISSN: 2321-9653*

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

## Design of Pseudorandom Pattern Generator for MIHST

Nagaveni<sup>1</sup>, Dr. Baswaraj Gadgay<sup>2</sup>, Suman Pujari<sup>3</sup>

<sup>1</sup>PG student Dept of VLSI Design & Embedded systems VTU PG Centre Kalaburagi

<sup>2</sup>Research Guide and Professor VTU PG Centre Kalaburagi

<sup>3</sup> Assistant Professor Dept of VLSI & ES VTU PG Centre Kalaburagi

Abstract -: The paper describes a system generator which produces Pseudo random sequence with user defined toggling range. The patterns were generated using PRPG; Detection of errors is done using Microprocessor Hardware Self Test (MIHST) for each pattern produced by generator. The MIHST is a permutation of BIST and SBST principles. A method is introduced for mechanical selection of some control signals of generator offering simple and exact tuning. The main intend is that due to PRESTO (pre-selected toggling level) switching activity for the period of scan loading is reduced. Using Micro processor hardware self test unit processor executes compact test sequences like SBST. Microprocessor Hardware Self Test is mainly used for processors online test rooted on system-on-chip, it overcomes limitations of SBST. The major benefit of MIHST is it utilizes less resources compared to SBST. The MIHST reduces time essential for the execution by removing instructions necessary for the test flow management.

Keywords: Built-in self-test (BIST), low-power (LP) test, pseudorandom test pattern generators (PRPG), SBST.

I.

#### INTRODUCTION

In future, the most crucial target of test assembling will stay same, basically to guarantee solid and high element semiconductor item conditions furthermore critical movement has been experienced by test arrangements. The design procedure, semiconductor technology and design characteristics are the key in components which will affect this development. Decade back test compression techniques were introduced, which has become quickly the core stream of Design for Test methodology. LBIST (logic-built-in-self-test) created for framework, board and test field is ahead of time for test generation as it will give exceptionally powerful Outline to Test and it has been used gradually more with test compression. Preserving all scan firmness and LBIST advantages, it can diminish the manufacturing cost of test.

The variety of schemes used to decrease power through scan testing proposed. There are various arrangements purposely projected for BIST, to maintain the peak power and average beneath given limit. For instance, the power used during test is decreased by preventing transitions at recollection elements. This will be generated by adding up gating logic in between logic driven by them and scan cell results.

A burst clock controller backs off a portion of the movement cycles to diminish the voltage hang identified with a higher circuit action. It allows steady increase of circuit activity, in this manner decreasing di/dt effect. Depending upon the requirements for bit by bit warming of circuit shift clocks were gated by controller.

#### II. RELATED WORK

Michal Filipek proposed the work on preselected toggling sequence generation using LFSR, it shows test compression technique by which accurate and predictable result will be obtained. Generated sequence includes toggling levels of user distinct. The main intend is that due to PRESTO (pre-selected toggling level) switching activity for the period of scan loading is reduced <sup>[1]</sup>S. Bhunia proposes new circuit so power dissipation during testing is reduced; this is obtained at input level of logic circuit by signal alteration masking. Addition of extra one transistor in logic circuit results advantages in the field of area, power and delay fields <sup>[2]</sup> H. Mahmodi proposed the implementation of masking effect by addition of supply gating in the path from supply to ground, at flip-flop output <sup>[2].</sup> E. G. McCluskey proposed method fault coverage perfection for test per each scan, BIST is used for test circuit modification by adding test points or the redesigning of circuit is done. Bit fixing sequence generator architecture is designed by him, architecture is designed to change bits of pseudorandom sequence shifted to scan chain for the addition of test cubes into sequence <sup>[4].</sup>

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Patrick Girard proposed a technique, i.e. irregular one information change test creation, which produces test succession of low power, so during circuit testing fault coverage at high level is achieved. Christian Landrault proposes equivalent BIST execution of RSIC producer and surveys the region overhead effect <sup>[8].</sup>

In this paper we are using MIHST for testing purpose, MIHST is Micro processor hardware built in self test. It is a permutation of BIST and SBST principles, by using Micro processor Hardware self test unit the processor execute the compact SBST test sequences. The main advantages of MIHST are, it decreases execution time for test, it better preserves the intellectual property of core processor and memory structure is not obligatory to neither preserve the test sequences nor test memory.

#### III. PROPOSED WORK

In this section will see the design of each block. The proposed method describe about the generation of patterns using PRESTO (Pre selected toggling level) and testing the device for each pattern generated by using microprocessor Hardware self test.

A. Test Design

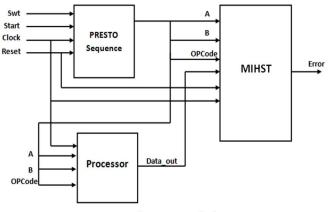

Fig -1: Test design

The test design consists of PRESTO, MIHST and Processor

Fig-1 shows test design block diagram, designed to test the processor for every sequence generated by PRESTO using MIHST the fault will be detected. The 32-bit preselected sequence is generated using PRPG.PRPG is designed using LFSR. The patterns generated by PRESTO consist of user distinct toggling rate. PRESTO pattern is given as input to MIHST test unit; processor performs operation to which it is designed for each sequence generated by PRESTO.

The 32-bit sequence from PRESTO is divided into two 8-bit inputs A and B and five bit OPCode. Using A, B and OPCode processor performs operation and processor output is given to MIHST. Test unit performs the operation like And, OR and rotate etc operations, check unit in MIHST detects fault present in processor by comparing output from processor and test unit.

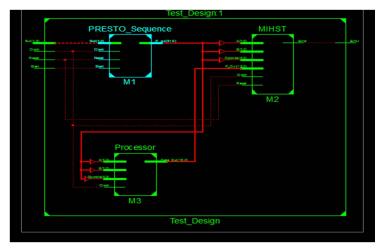

Fig-2: Test design RTL schematic

Volume 4 Issue VII, July 2016 ISSN: 2321-9653

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

#### B. Presto Generator Basic Architecture

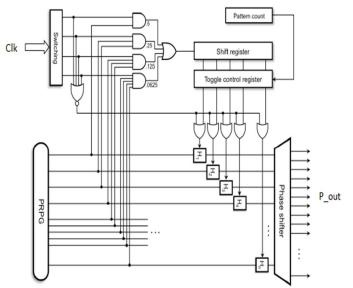

The PRESTO structure consist of PRPG, Shift register, Phase shifter, switching circuit

Fig-3 shows the PRESTO Generator basic architecture. Phase shifter will be connected to the PRPG by supplying scan chains, pseudorandom patterns are produced.

The n numbers of hold latches are located between phase shifter and PRPG. Every hold latch is separately controlled by equivalent stage of n-bit control register. When latch is enable data to the phase shifter will be given from scan chains, if latches are disabled data to phase shifter will be given from PRPG.

Loading the scan string with low transitions count patterns are not only allowed by PRESTO generator thus drastically reduces power dissipation, along with it enables the selections of its control such that generated test sequence consist of user distinct toggling rates.

Fig-3: PRESTO Structure

For each pattern the reloading of control register is done by using the substance of shift register. The enable signals which are given to shift register be produced within probabilistic manner using PRPG which is original with programmable sets of weight.

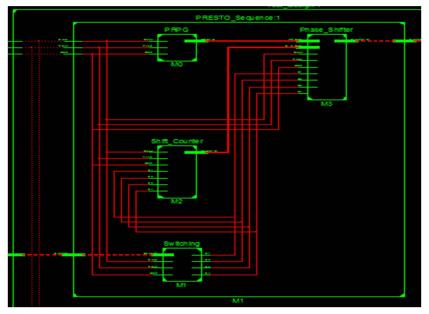

Fig-4: PRESTO RTL Schematic

Volume 4 Issue VII, July 2016 ISSN: 2321-9653

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

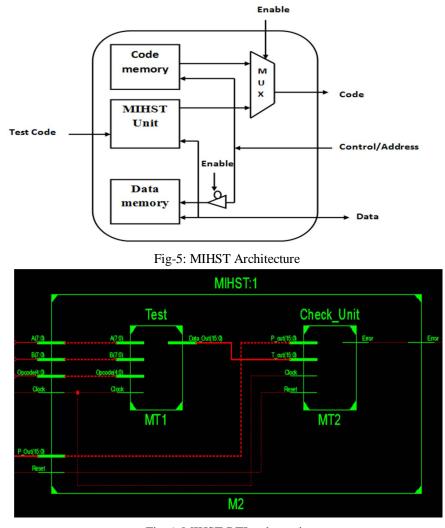

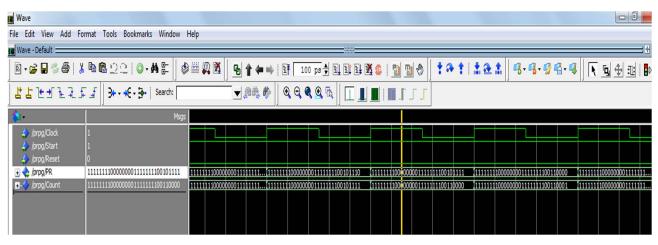

#### C. MIHST Architecture

Microprocessor Hardware Self Test is mainly used for processors online test rooted on system-on-chip, it overcomes limitations of SBST. This existing method adds significant features of functional based as well as Hardware based techniques. MIHST Method exists on two thoughts

- 1) The device executes in two states one is normal state another is test state. When the device is in normal state, the processor runs commands which are translated from code memory. When test state exists the device runs the commands from MIHST unit.

- 2) The MIHST element encodes program which is to be tested internally in convention manner which shows the regularity of test program, hardware required for storage of test program is reduced.

By the result of above thoughts the processor runs commands from MIHST element but it will not control flow of execution. This operational principle is critical because

1) When manipulating test program the collection of address will be manipulated by test engineer.

2) This allows monitoring the execution of instruction on bus without completing test procedure which is caused by faults.

The main benefit of MIHST is it utilizes less resources compared to SBST, as data and test code is stored in system memory. The MIHST reduces time required for the execution by removing instructions required for the test flow management.

MIHST unit will be programmed by extremely encoded data which is hardwired within it or uploaded by outside, in each case MIHST has advantages over SBST in case of IP protection, core users will not provided by test program. Thus architectural design of unit will be easily understood by test unit.

Fig-6: MIHST RTL schematic

► **5**. 4<sup>2</sup> • **7**2 • **5**0

International Journal for Research in Applied Science & Engineering

## **Technology (IJRASET)**

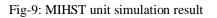

IV. SIMULATION RESULTS

Fig-7: PRESTO simulation results

| 出 上 上 王 王 王   → - +€ - →   Search: |                  |                  |                                         |                                                     |           |  |  |  |  |  |

|------------------------------------|------------------|------------------|-----------------------------------------|-----------------------------------------------------|-----------|--|--|--|--|--|

| <b>•</b>                           | Msgs             |                  | 12                                      |                                                     |           |  |  |  |  |  |

| /processor/Clock                   | 1                |                  |                                         | نی ز اسا اسالا بر زیر زیر اسا اسالا بر زیر زیر اسال |           |  |  |  |  |  |

| 🛨 🌛 /processor/A                   | 11110000         | 11110000         |                                         |                                                     |           |  |  |  |  |  |

| 🖅 🥠 /processor/B                   | 00001111         | 00001111         |                                         |                                                     |           |  |  |  |  |  |

| 🚛 🍫 /processor/Opcode              | 01011            | 01010            |                                         | 01011                                               |           |  |  |  |  |  |

|                                    | 000000000001111  |                  | 000000000000000000000000000000000000000 |                                                     | 000001111 |  |  |  |  |  |

| I processor/Add                    | 11111111         | 11111111         |                                         |                                                     |           |  |  |  |  |  |

| 🛶 /processor/Sub                   | 11100001         | 11100001         |                                         |                                                     |           |  |  |  |  |  |

| 🚽 /processor/Mul                   | 0000111000010000 | 0000111000010000 |                                         |                                                     |           |  |  |  |  |  |

| 🚽 /processor/Divi                  | ບບບບບບ           |                  |                                         |                                                     |           |  |  |  |  |  |

| 🚽 /processor/INCA                  | 11110001         | 11110001         |                                         |                                                     |           |  |  |  |  |  |

|                                    | 00010000         | 00010000         |                                         |                                                     |           |  |  |  |  |  |

|                                    | 00001110         | 00001110         |                                         |                                                     |           |  |  |  |  |  |

|                                    | 11110001         | 11110001         |                                         |                                                     |           |  |  |  |  |  |

|                                    | 0000000          | 0000000          |                                         |                                                     |           |  |  |  |  |  |

| ⊢� /processor/O                    | 11111111         | 11111111         |                                         |                                                     |           |  |  |  |  |  |

| 🛶 /processor/NTA                   | 00001111         | 00001111         |                                         |                                                     |           |  |  |  |  |  |

|                                    | 11110000         | 11110000         |                                         |                                                     |           |  |  |  |  |  |

| 🛶 /processor/Xo                    | 11111111         | 11111111         |                                         |                                                     |           |  |  |  |  |  |

|                                    | 11111111         | 11111111         |                                         |                                                     |           |  |  |  |  |  |

| +                                  | 0000000          | 0000000          |                                         |                                                     |           |  |  |  |  |  |

Fig-8: Test design block simulation result

|                                               | 🖹 🕶 🖬          | ê 📙 🗇 🖨   🐰                             | ) 🖻 🖪 🖄 🔔   🤇 | ▶•#4 Ё  ]    | ي 💥 🛍 🍪  | <u>6</u> | <b>* *</b> * | • I II | 100 p     | 3 🔶 🚉 🛛 | i i i | <b>5</b> 6   _ | <b>1</b> | •       | <b>9</b> 🚦 |

|-----------------------------------------------|----------------|-----------------------------------------|---------------|--------------|----------|----------|--------------|--------|-----------|---------|-------|----------------|----------|---------|------------|

|                                               |                |                                         |               |              |          |          |              |        |           |         |       |                |          |         |            |

| <u>ĽĽ</u> ±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±± |                |                                         |               |              |          |          |              |        |           |         |       |                |          |         |            |

| 🔕 🗸                                           |                | Msgs                                    |               |              |          |          |              |        |           |         |       |                |          |         |            |

| - 🍲                                           | /test/Clock    | 1                                       |               |              |          |          |              |        |           |         |       |                |          |         |            |

| •                                             | /test/A        | 11110000                                | υψυυυυυ       | 11110000     |          |          |              |        |           |         |       |                |          |         |            |

| •                                             | /test/B        | 00001111                                | υυυυυυυ       | 00001111     |          |          |              |        |           |         |       |                |          |         |            |

| 🗉 🌧                                           | /test/Opcode   | 01000                                   | υψυυυ         | 01010        |          | )        | 01001        |        |           |         | 01000 |                |          |         |            |

| • <b>-</b>                                    | /test/Data_Out | 000000000000000000000000000000000000000 | υψυυυυυυυυυυυ |              | 00000000 | 11111111 |              |        | 000000000 | 0000000 |       |                | 00000000 | 1101111 |            |

|                                               | /test/Add      | 11111111                                |               | 11111111     |          |          |              |        |           |         |       |                |          |         |            |

| •                                             | /test/Sub      | 11100001                                |               | 11100001     |          |          |              |        |           |         |       |                |          |         |            |

|                                               | /test/Mul      | 0000111000010000                        |               | 000011100001 | 0000     |          |              |        |           |         |       |                |          |         |            |

|                                               | /test/Divi     | 0000000                                 | υψυυυυυ       |              |          |          |              |        |           |         |       |                |          |         |            |

|                                               | /test/INCA     | 11110001                                |               | 11110001     |          |          |              |        |           |         |       |                |          |         |            |

| <b>≞</b> -⇒                                   | /test/INCB     | 00010000                                |               | 00010000     |          |          |              |        |           |         |       |                |          |         |            |

|                                               | /test/DCB      | 00001110                                |               | 00001110     |          |          |              |        |           |         |       |                |          |         |            |

|                                               | /test/DCA      | 11101111                                |               | 11101111     |          |          |              |        |           |         |       |                |          |         |            |

| <b>-</b>                                      | /test/AN       | 0000000                                 |               | 0000000      |          |          |              |        |           |         |       |                |          |         |            |

| <b>≞</b> -♦                                   | /test/O        | 11111111                                |               | 11111111     |          |          |              |        |           |         |       |                |          |         |            |

|                                               | /test/NTA      | 00001111                                |               | 00001111     |          |          |              |        |           |         |       |                |          |         |            |

| •                                             | /test/NTB      | 11110000                                |               | 11110000     |          |          |              |        |           |         |       |                |          |         |            |

| •                                             | /test/Xo       | 11111111                                |               | 11111111     |          |          |              |        |           |         |       |                |          |         |            |

| <b>H</b> -                                    | /test/N        | 11111111                                |               | 11111111     |          |          |              |        |           |         |       |                |          |         |            |

| •                                             | /test/No       | 0000000                                 |               | 0000000      |          |          |              |        |           |         |       |                |          |         |            |

www.ijraset.com IC Value: 13.98 Volume 4 Issue VII, July 2016 ISSN: 2321-9653

## **International Journal for Research in Applied Science & Engineering**

### **Technology (IJRASET)**

#### CONCLUSIONS

Proposed a Test pattern generation method, where patterns are generated using PRPG. The PRESTO configuration is proposed here, it generates pattern with preselected toggling rate, i.e. the pattern produced have user distinct toggling rate. So the switching activity of sequence will be reduced due preselected toggling and power utilization is reduced. PRESTO is low power pattern generator. The MIHST architecture is developed for self test, used to test IP core of processor in SoC. MIHST approach overcomes limitations of SBST. Test cost and time is reduced using MIHST method.

#### REFERENCES

- [1] Michał Filiipek, Grzeegorz Mrugalski "Low-Power Programmable PRPG with Test Compression Capabilities" 1063-8210 on VLSI IEEE 2015.

- S. Bhunia, Mahmoodi, D. Ghoosh, S. Mukhoopadhya, "Low-power scan design using first-level supply gating" 0n vlsi vol-13 pp 384-395 no 03 IEEE. (VLSI) 2005

- [3] Maurizio REBAUDENGO, Fulvio CORNO," Low Power BIST via Non-Linear Hybrid Cellular Automata" pp no 29 34 in proc IEEE VTSI 2000

- [4] Edaward J. McClusky, Nur A. Touba" Bit-Fixing in Pseudorandom Sequences for Scan BIST" vol-20 pp 545-555 no 4 IEEE on VLSI 2001

V.

- [5] P. Girarad, C. Landralt, S. Pravosoudovitch, A. Virazell, and H.-J. Wunderliich, "High fault coverage with low-power test sequences in a BIS environment," design test IEEE n0-5 pp 44-52 vol 19 200

- [6] Ernesto Sanchez, Paolo Bernardi," MIHST: A Hardware Technique for Embedded Microprocessor Functional On-Line Self-Test" pp.no. 11 vol. 63, IEEE November 2014.

- [7] Abbu-Issa and S. F. Quigleiy, "Bit-swapping LFSR for low-power BIST," Electron. Lett., vol. 44, no. 6, March-2008 pp. 401–411,

- [8] P. Girarad, L. Guiller, C. Landrault, and S. Pravossoudovitch, "A test vector inhibiting technique for low energy BIST design," April-1999, pp. 407–412. IEEE VLSI

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)