# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 2 Issue: VI Month of publication: June 2014

DOI:

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653

## INTERNATIONAL JOURNAL FOR RESEARCH IN APPLIED SCIENCE AND ENGINEERING TECHNOLOGY (IJRASET)

### FPGA Implementation OF Iterative Log Multiplier Using Operand Decomposition For Image Processing Application

Pragyan Paramita Mohanty 1, Mrs. Annapurna K.Y.2

PG Scholar at PESIT Bangalore1, Asst. Prof, Dept of E&C PESIT, Bangalore2

Abstract—Faster multiplier is the vital procedure mainly for DSP and image processing application. Log multiplier converts the multiplication into addition, hence speed up the multiplication. Mitchell's approximation based log multiplier does this but with errors. OD-Mitchell reduces the AEP (Average Error Percent) while the iterative Mitchell reduces the MPE (Maximum Possible Error). This project focuses on combining both the method to improve AEP and MPE. Further this multiplier is used in case of Gaussian filter to improve PSNR (Peak Signal To Noise Ratio). Hence the accuracy is improved here. The hardware implementation is done by using the FPGA board. The simulation is done using XILINX 14.5 and Modelsim.

Keywords—AEP, MPE, Gaussian filter, PSNR,FPGA

#### I. INTRODUCTION

The binary multipliers operate on the binary operands and calculate products by using partial product additions. Logarithmic multiplier converts the binary operands into their corresponding logarithmic form. In LNS (Logarithmic Number System) multiplication is achieved by means of addition. Hence the Multiplication is obtained by first calculating logarithms of binary numbers and then adding individual log values, finally calculating antilog value of the added sum.

The multiplication using logarithm function is used in a large number of applications such as digital signal processing image processing. biomedical systems, telecommunication systems and so on. Calculation of logarithm function using software is not fast enough, and hence a dedicated hardware should be used. Also the dedicated hardware has become much attractive to design the arithmetic blocks in 3-D graphics systems for mobile applications and for Cartesian-to-polar coordinate translation systems. Logarithmic number system of base two is used to optimize the arithmetic block like multiplication, division and square root. It maintains high performance without incurring excessive area and power increment.

Basically in a large number of DSP applications, speed is the significant criteria compared to accuracy. In these cases, the most suitable multiplier is the truncated and Logarithmic multipliers. In case of truncated multipliers, the less important partial products are left out and recompense is provided. So it partly compensates for left out terms. In the Logarithmic multipliers rounding of products can be done. It is alternatively used for fixed point number and floating point number. This translates multiplication into addition and division into subtraction. The main goal of Log Multiplier is to lessen errors with power utilization. One of the methods to calculate log and antilog is to use LUT method, but it requires more area to store the log and antilog values. The Mitchell log multiplier uses only some shift operations for log and antilog calculations .So it require fewer hardware overhead and results high speed with less power utilization.

#### II.LITERATURE SURVEY

Till now papers are published based on OD-Mitchell and Iterative Mitchell separately. A paper for the process of binary logarithm has been also published. How the multipliers are used in filters to improve the accuracy also has been done. The filter has removed the salt pepper noise, Gaussian noise and high frequency noise.

ISSN: 2321-9653

## INTERNATIONAL JOURNAL FOR RESEARCH IN APPLIED SCIENCE AND ENGINEERING TECHNOLOGY (IJRASET)

#### II. PROPOSED SYSTEM

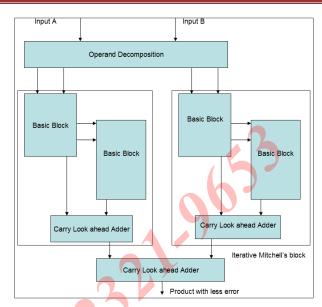

The proposed system aims at solving the accuracy problem. It reduces the maximum possible error by using iterative method and also reduces the average error rate by using the operand decomposition method. Operand decomposition is done prior to the Mitchell logarithm. After skipping the leading one from both the number, again these are given as input to one more basic block. Finally both the output is added to give the final output.

The key component in the Gaussian filter is the convolution between the Gaussian mask and the 255\*255 pixel values. Hence according to the accuracy of the multiplier, the PSNR of an image having Gaussian noise and salt pepper noise has been improved.

#### III. WORK METHODOLOGY

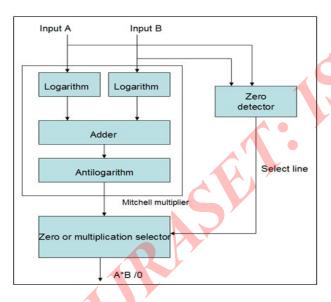

The basic block includes logarithm block, adder, and antilogarithm block along with zero detector. The error involved here is more. So the proposed architecture has been implemented. The below figure is the basic Mitchell block.

Fig 1: Basic Mitchell Block

As shown in the figure Operand decomposition reduces the error caused by the carry over generated from the mantissa part to the characteristic part. Hence when we apply this through the Mitchell block the error will be reduced compared to the only Mitchell block. The iteration of the Mitchell again reduces the maximum possible error.

Fig 2: Proposed Mitchell Block

The Gaussian filter is implemented using FIFO memory, hence reduces the area utilization. The image with Gaussian noise and the salt pepper noise are made noise free with the help of Gaussian filter that uses the proposed multiplier.

#### V.RESULT

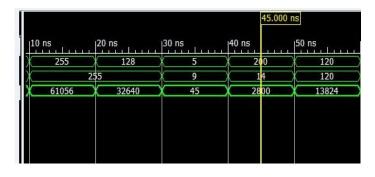

Simulations of the proposed design will be conducted in the Xilinx 14.5 and modelsim . The verified Verilog code will be then dumped into FPGA board.

Fig 3: Simulation result of the proposed multiplier using XILINX

ISSN: 2321-9653

## INTERNATIONAL JOURNAL FOR RESEARCH IN APPLIED SCIENCE AND ENGINEERING TECHNOLOGY (IJRASET)

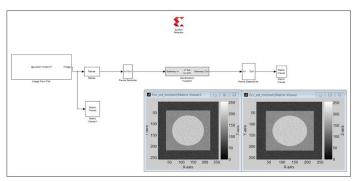

Fig 4: Verilog simulation result in Spartan-6 FPGA board using system generator

| Standard | Filter   | Filter   | Filter | Filter   |

|----------|----------|----------|--------|----------|

| Deviatio | using    | using    | using  | using    |

| n with   | Basic-   | OD-      | Ecc-   | Ecc-OD-  |

| mean=0   | Mitchell | Mitchell | basic- | Mitchell |

|          |          |          | block  |          |

| 1        | 31.2288  | 31.2288  | 35.896 | 36.0896  |

| 1.2      | 28.1308  | 29.0459  | 32.567 | 34.15140 |

| 1.4      | 28.1308  | 29.049   | 32.567 | 34.1514  |

| 1.6      | 29.0459  | 31.22884 | 33.15  | 34.15    |

TABLE I: PSNR comparison of an image

We have shown a proposed method of multiplier in order to get more speed with less error. Also we have shown the application of multiplier in Gaussian filter to increase the PSNR.. This proposed architecture can be applied to the MAC unit, where we require large number of convolution, FFT filter, FIR filter if pipeline can be achieved.

#### REFERENCES

- [1] JOHN N.Mitchell, "Computer multiplication and division using binary logarithm," IRE Trans. On electronic computers.August. 1962,pp.512-517.

- [2] V. Mahalingam, N. Rangantathan," Improving accuracy in Mitchell's logarithmic multiplication using operand decomposition", IEEE Transactions on Computers ,Vol.55 No.12,pp. 1523–1535,December 2006.

- [3] Duncan J. McLaren, "Improved Mitchell-Based Logarithmic Multiplier for Low-power DSP Applications",pp.53-56,2003.

- [4] Satish S Bhairannawar, Rathan R, Raja K B, Venugopal K R, L M Patnaik, "FPGA based recursive error free Mitchell log multipler for image filters", 2012 IEEE International Conference on Computational Intelligence and Computing Research

- [5] P.Karunakaran, S.Venkatraman, I.Hameem Shanavas, T.Kapilachander, "Power Optimized Multiplier Using Shannon Based Multiplexing Logic", I.J. Intelligent Systems and Applications, vol. 6, pp. 39-45, June 2012.

- [6] Hui Kong, Sanjay E. Sarma, Feng Tang "Generalizing Laplacian of Gaussian Filters for Vanishing-Point Detection" Vol. 14, No. 1, pp.408-418, March 2013

- [7] Keokanlaya Sihalath, Somsak Choomchuay"Fingerprint Image Enhancement with Second Derivative Gaussian Filter and Directional Wavelet Transform" 2010 Second International Conference on Computer Engineering and Applications.

- [8] Yuanxin Wu, Dewen Hu, Meiping Wu, Xiaoping Hu, "A Numerical-Integration Perspective on Gaussian Filters" IEEE TRANSACTIONS ON SIGNAL PROCESSING, Vol. 54, No. 8,pp.2910-2921, August 2006.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)