IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 4 Issue: XII Month of publication: December 2016

DOI:

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

www.ijraset.com IC Value: 13.98

# International Journal for Research in Applied Science & Engineering Technology (IJRASET) Skew Managed Global Clock Network Using Type Matching

Jeba Saral Darling<sup>1</sup>, Jessintha D<sup>2</sup>

Electronics and Communication Department, Easwari Engineering College

Abstract—Clock gating has emerged as an effective low power technique these days. Various researches are being made in the optimization of this technique. While clock gating finds its applications in the clock tree synthesis, it's crucial that this additional circuitry does not include skew to the entire chip design. Also when the clock gating involves the use of all gates, (i.e.) NAND, NOR which has different timing behaviours, there is a definite possibility of an increase in skew. Therefore, in this paper a global clock tree design called type matching is proposed, wherein same type of gate at every level of clock tree is maintained, replacing even the buffers with the same type of gate buffers with the proposed mechanism. Also a comparison on the normal clock gated tree and type matched clock tree is done and proved that the clock skew minimization is achieved in type matched clock trees at the cost of clock tree area and power consumption.

Keywords— Clock tree, Skew, Type matching, Clock gating.

#### I. INTRODUCTION

One of the most extensively used techniques for dropping dynamic power is clock gating, a number of techniques to diminish the dynamic power have been urbanized, of which clock gating is predominant. Clock gating is a popular technique used in many synchronous circuits for reducing dynamic power dissipation. Clock gating saves power by adding more logic to a circuit to clip the clock tree. Clipping the clock disables portion of the circuitry so that the flip-flops in them do not have to switch states. Switching states consumes power. When not being switched, the switching power consumption goes to zero, and only leakage currents are acquired. Clock gating works by taking the enable conditions attached to registers[7] and utilizes them to gate the clocks. This clock gating logic. This clock gating logic is generally in the form of "Integrated Clock Gating" (ICG) cells[2]. Here the symmetric clock tree is used. All flops of a symmetric clock tree, traced back from the clock tree root are passing the same number of levels and the same cell references at each level. The clock tree is balanced at a specific corner which should fit all corners.

#### II. PRACTICAL METHODS TO IMPLEMENT CLOCK GATING

- A. By the addition of enable into the RTL code in such that it can be implemented into clock gating.

- B. RTL designers can directly include the clock gating cells in to design circuit.

- C. By the usage of tools like Cadence SoC Encounter, CTS (Clock Tree Synthesis) we can include clock gating in designs.

#### **III. GATED CLOCK TREE**

Very often we have the possibility that only a portion of the circuit is active. Therefore, clock gating is an efficient technique to drastically bring down the power consumption.

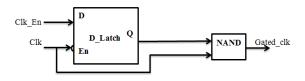

Making use of the below clock gating circuit in Fig.1, different types of gated clock trees can be designed. A normal clock gating circuit consist of a latch usually D – latch, which is preceded by any gate of the designer's choice. This latch is being added to the circuit such that it can boost the signals so that the clock gating is efficient.

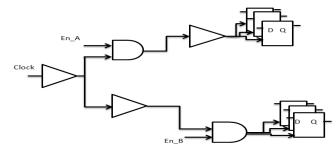

By the use of the above explained clock gating design, the normal gated clock tree can be formed as in fig 2. This design[5], as it is evitable that the area it occupies is small, but the skew is obviously added in addition to the design's skew.

Figure 1: Clock Gating Circuit

**International Journal for Research in Applied Science & Engineering**

**Technology (IJRASET)**

Figure 2: Normal Clock gating circuit

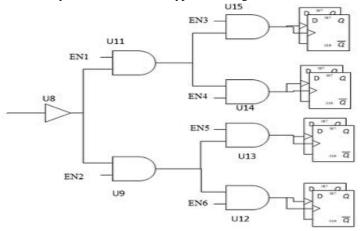

#### IV. TYPE MATCHING CLOCK TREE

The main alteration that has to be done in a type matched tree design is that, the design of the logical buffers [1]. These logical buffers can be designed in contrary of the buffers which are to be replaced as the same type of gates. In this way, we have the different gate buffers according to the controlling values of the universal gates. The possibility of type matching is proved with the help of two lemmas provided below.

Lemma 1: Any clock control logic can be implemented using only NAND gates.

Lemma 2: Any clock control logic can always be transformed to type-matching clock tree.

Figure 3: Type matched clock tree

#### V. BLOCK DIAGRAM OF THE PROPOSED DESIGN

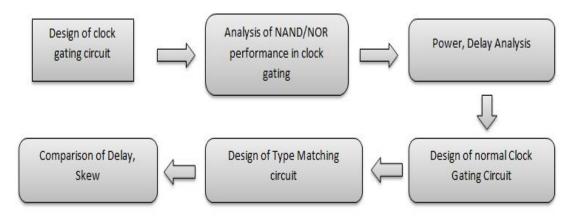

The mechanism in which the proposed design works is given by means of a block diagram in Fig.4.

Figure 4: Block diagram of the proposed design

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

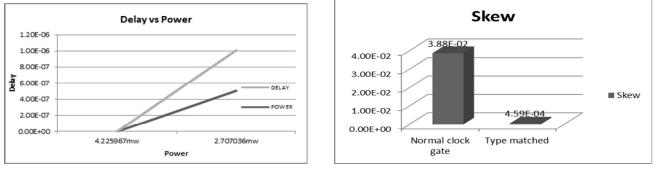

#### VI. DELAY AND POWER EVALUATION OF THE CLOCK GATING CIRCUITS

The proposed idea was designed by means of the results analysed from the H-Spice on the clock gating circuits using two types of the universal gates, NAND/NOR[3]. From the results, it is evident that the clock gating circuit involving NAND has less delay (i. e) skew, and therefore the type matched clock tree was designed with the NAND gate. On the other hand, the normal clock gated tree was also designed with the help of the buffers and NAND gates. Finally, the two circuits were simulated using TANNER, and the further analysis was done with the help of H-SPICE and the results are tabulated in the next section.

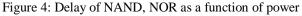

#### VII.SIMULATIONS AND EXPERIMENTAL RESULTS

The normal clock gating circuits using NAND, NOR were simulated and verified using TANNER tool. The same architectures were analyzed using HSPICE for its power, delay. Then the normal and type matched gated clock tree were simulated using TANNER and it was verified using HSPICE for its skew. From the table 1, it is evident that the clock gating circuits involving NAND gate[6] produces less delay when compared to the other. Hence the NAND gate was used in the clock gating circuitry. In addition, the H-SPICE signifies that the type matching technique holds good when designed with the NAND gates rather than using various types of gates in different levels of the clock tree design.

Table 1: Simulation results

| Circuits                     | Power      | Delay(s)   |

|------------------------------|------------|------------|

| Gating circuit<br>using NAND | 4.225967mw | 6.6853E-11 |

| Gating circuit<br>using NOR  | 2.707036mw | 5.0528E-07 |

| Normal gated clock tree      | 4.939207w  | 3.8754E-02 |

| Type matched<br>clock tree   | 8.664184w  | 4.5936E-04 |

#### VIII. CONCLUSION

In the clock gating circuit, the efficiency of using NAND, NOR gates are analyzed and based upon the results, a global clock tree network involving gating circuits is designed with the new proposed method called type matching circuits. The circuit is compared with the normal clock gated tree and found that it can significantly reduce the clock skew in every process corner with a small penalty on the clock tree area and the clock tree power consumption. This type matched circuit can be used instead of industry strength gated clock tree.

#### REFERENCES

- Chang CM, Huang SH, Ho YK, Lin JZ, Wang HP, Lu YS. Type-matching clock tree for zero skew clock gating. 45th ACM/IEEE Design Automation Conference, DAC'08; Anaheim, CA. 2008 Jun 8-13. p. 714–9..

- [2] Borkovic D, McElvain KS. Reducing clock skew in clock gating circuits. USA; Synplicity Inc: 2003.

- [3] Garret D, Stan M, Dean A. Challenges in clock gating for a low power ASIC methodology. International Symposium on Low Power Electronics and Design;

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

San Diego, CA, USA. 2002 Aug 17. p. 176-81.

- [4] S. Kumar, K. Kim, and S. Sapatnekar, "Impact of NBTI on SRAM read stability and design for reliability," in Proc. Int. Symp. Quality Electron. Des., Mar. 2006, pp. 213–218.

- [5] W. C. Chao and W. K. Mak, "Low-Power Gated and Buffered Clock Network Construction," ACM TODAES, Vol. 13, No. 1, Article 20, January 2008.

- [6] G. Chen, K. Chuah, M. Li, D. Chan, C. Ang, J. Zheng, Y. Jin, and D. Kwong, "Dynamic NBTI of PMOS transistors and its impact on device lifetime," in Proc. IEEE Int. Reliab. Phys. Symp., Mar. 2003, pp. 196–202.

- [7] W. Shen, Y. Cai, X. Hong, and J. Hu, "An Effective Gated Clock Tree Design Based on Activity and Register Aware Placement," IEEE Transactions on VLSI Systems, Vol. 18, No. 12, pp. 1639-1648, 2009.

- [8] S. Mahapatra, D. Saha, D. Varghese, and P. Kumar, "On the generation and recovery of interface traps in MOSFETs subjected to NBTI, FN, and HCI stress," IEEE Trans. Electron Devices, vol. 53, no.7, pp. 1583–1592, Jul. 2006.

- [9] Su YS, Hon WK, Yang CC, Chang SC, Chang YJ. Value assignment of adjustable delay buffers for clock skew minimization in multi-voltage mode designs. IEEE/ACM International Conference on Computer-Aided Design - Digest of Technical Papers, ICCAD 2009; San Jose, CA. 2009 Nov 2-5. p. 535–8.

- [10] Lin KY, Lin HT, Ho TY. An efficient algorithm of adjustable delay buffer insertion for c10ck skew minimization in multiple dynamic supply voltage designs. 2011 Proceedings of the 16th Asia and South Pacific Design Automation Conference (ASP-DAC); 2011. p. 825–30.

- [11] Vennelakanti S, Saravanan S. Design and analysis of low power memory built in self test architecture for SoC based design. Indian Journal of Science and Technology. 2015 Jul; 8(14):1–5.

- [12] Wu Q, Pedram M, Wu X. Clock gating and its application to low power design of sequential circuits. IEEE Transactions on Circuits and Systems I: Fundamental, Theory and Applications. 2000 Mar; 47(3):415–20.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)