IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: IV Month of publication: April 2017

DOI: http://doi.org/10.22214/ijraset.2017.4224

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

International Journal for Research in Applied Science & Engineering

## Technology (IJRASET) Design and FPGA Implementation of DDR SDRAM Controller

Aadhar Agarwal<sup>1</sup>, Pooja Choudhary<sup>2</sup>, Kalpesh Jain<sup>3</sup>, Chetan Kumhar<sup>4</sup>, Abhiroop Goyal<sup>5</sup>, Harshita Rohatgi<sup>6</sup> <sup>1,3,4,5,6</sup>ECE Department, SKIT M&G, Jaipur <sup>2</sup>Asst. Prof. ECE Department, SKIT M&G, Jaipur

Abstract: Technology is increasing day by day. The world is obsessed with smart phones, laptops and computers. RAM which is used in these devices is the internal memory of CPU for storing data, program and program result. SDRAM or Synchronous Dynamic Random Access Memory is able to work efficiently. It is synchronised with the clock of the processor. The advance version of SDRAM is DDR (Double Data Rate) SDRAM which transfer data on both rising and falling edges of the clock resulting in double data transfer rate. In this paper, DDR SDRAM controller is designed and implemented on FPGA. Transfer rate is 266 M bits/s/pin and clock frequency is 133 MHz This has been done using Verilog HDL on Xilinx ISE 14.2 and finally the controller is targeted to Xilinx Spartan 3E FPGA kit.

Keywords: DDR SDRAM Controller, FPGA, Read, Write, Precharge, Burst.

#### I. INTRODUCTION

Computer memory is the storage space where data processing and instructions are stored. From toys to satellite for navigation systems, every appliance almost use high speed and high throughput memory to function. The SD RAM fetches twice the data for a single clock cycle which increases speed as well as throughput. The memory is divided into number of small parts called a cell. Each cell has a unique address. If a computer has memory of 64k then it will have 64k (64\*1024) memory locations. The address of these locations will vary from 0 to 65535. [1]

Physically, RAM is made up of small electronic chips mounted on modules. There are 2 types of RAM: (a)Static(SRAM) and (b) Dynamic(DRAM). The use of Dynamic RAM is useful since memory density is increased and power consumption and area is reduced. DRAM is an array of memory cells. Compared to the structural design of SRAM, additional memory cells are packed into the memory by DRAM architecture.

In terms of speed, SRAM is faster. DRAM requires refreshing thousands of times per second in order to maintain the data while SRAM does not need refreshing, which is what makes it faster than DRAM. DRAMs memory cells are composed of capacitor and transistor. DRAM supports access times of about 60 nanoseconds, while static RAM can give access times as low as 10 nanoseconds. [2]

Double Data Rate-Synchronous DRAM, a type of DRAM that transfers the data on both the rising and falling edges of each clock cycle, doubling the memory chip's data throughput. DDR-SDRAM also consumes less power, making it suitable to notebook computers. The basic DDR SDRAM is also called DDR1\_SDRAM. DDR SDRAM has the advantage of high speed and large capacity, various time latencies decrease the data transmission efficiency of DDR SDRAM greatly.

While the motherboards which are intended to employ DDR are similar to those that use SDRAM, but they are not backward compatible with SDRAM. Similarly, SDRAM motherboards are not compatible with DDR. [2 - 5]

There are burst oriented read and write accesses to the DDR SDRAM; access start at a selected location and continue for a programmed number of locations in a programmed sequence. Beginning with the registration of an ACTIVE command, access is then followed by a READ or WRITE command. Programmable read or write burst lengths of 2, 4, or 8 are provided by DDR SDRAM. To provide a self-timed row precharge that is initiated at the end of the burst access, an Auto-Precharge function is provided. [5]

#### **II. OPERATIONS**

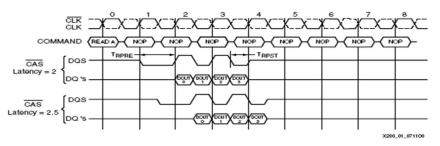

#### A. Burst Read Operation

The burst read operation in DDR SDRAM is performed in the same manner as the SDRAM. The read command is given the beginning column and row address and auto precharge is either enabled or disabled for that burst. If auto-precharge is enabled, at the completion of the burst the row is precharged. Throughout read bursts, the valid data-out component from the beginning column

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

address are available following the CAS latency after the read command each subsequent data-out component will be valid nominally at following positive or negative clock edgeDQS is driven by the DDR SDRAM alongside output data. The initial DQS LOW state is termed as the read preamble; the DQS LOW state coincident with the last data out component is termed as the read postamble.

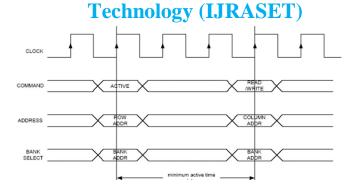

Fig. 2.1: Burst Read Operation

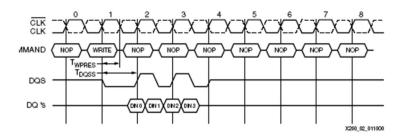

#### B. Burst Write Operation

The burst write operations are initiated with a WRITE command. The beginning column and bank addresses are supplied with the WRITE command, and auto precharge is either enabled or disabled for that access. If auto-precharge is enabled, the row being accessed is precharged at the completion of the burst. throughout WRITE bursts, the primary valid data-in component is registered on the primary rising edge of DQS following the WRITE command, and subsequent data components will be registered on consecutive edges of DQS. The DQS LOW state between the WRITE command and the initial rising edge is termed as the write preamble; the DQS LOW state following the last data-in component is termed as the write postamble. [7]

Fig 2.2: Burst Write Operation

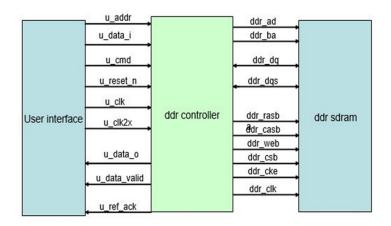

#### C. Top Level Block Diagram

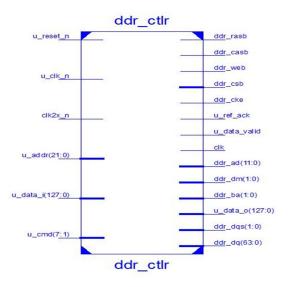

Fig 2.3: Block Diagram of DDR Controller with user interface

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

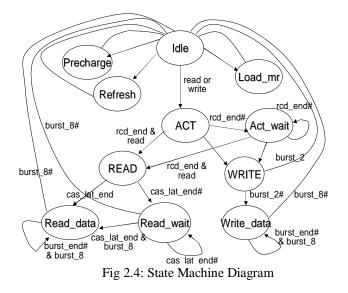

#### D. Controller State Machine

#### **III. COMMANDS**

The commands that would be issued by the user to the DDR SDRAM Controller.

#### A. No Operation (Nop)

The NOP command instruct the selected DDR SDRAM to perform No Operation. Unwanted commands are prevented from being registered during idle or wait states. Already progressive operations are not affected.

#### B. Mode Register

Inputs A0 to A11 load the mode registers. The load command can only be registered when all banks are idle and simultaneously another command cannot be issued. [8]

#### C. Active

To activate a row in a particular bank address, Active command is used. For bank selection B0 and B1 are used and A0-A11 selects the row address. This row remains active for accesses until a precharge command is issued to that bank. [9]

#### D. Read

The Read command is used to initiate a burst read access to an active row. The B0, B1 inputs selects the bank, and inputs A0-A7 selects the starting column. If auto precharge (A10) is selected, the row will be precharged at the end of the READ burst, else the row will remain open for subsequent accesses. [10]

#### E. Write

The Write command initiates a burst write access to an active row. The inputs B0, B1 select the bank, and the address provided on inputs A0-A7 selects the starting column. If auto precharge is selected (from A10), at the end of the burst, the row will be precharged, else the row will remain open for subsequent accesses. Input data on the DQS is written to the memory array according to the DM input logic level appearing coincident with the data. If a LOW DM signal is registered, the memory is written with the corresponding data, else the corresponding data inputs will be ignored, and WRITE will not be executed to that location. [12]

#### F. Precharge & Auto-Precharge

The precharge command is used for deactivating an open row in a particular bank or in all the banks. Input A10 determines the banks to be precharged, inputs B0, B1 select the bank. After a bank has been precharged, it remains in the idle state and must be activated prior to any command being issued. A precharge command will be treated as a NOP if there is no open row. The Auto Precharge feature performs the same precharge function described above, but without requiring an explicit command. It is accomplished from A8 bit to enable auto precharge in conjunction with a specific command(R/W). [13-14]

## International Journal for Research in Applied Science & Engineering

Fig. 3.1: Minimum Active Timing.

#### **IV. SIMULATIONS & RESULTS**

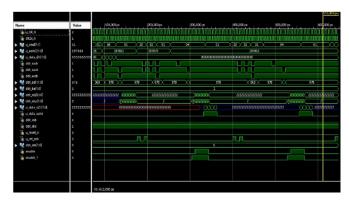

The Proposed design is simulated on iSim 14.2 and synthesized on Xilinx ISE 14.2 and then finally targeted to the Xilinx Spartan 3 FPGA device. The simulations, RTL Schematic and synthesis summary is shown below.

#### A. RTL Schematic

Fig 4.1: RTL Schematic

#### B. Simulation Results

Fig. 4.2: Read Cycle Simulation

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig. 4.3: Write Cycle Simulation

C. Synthesis Report

| Component        | Count         |

|------------------|---------------|

| Speed            | 256 Mbits/pin |

| Slices           | 458           |

| Slice Flip Flops | 788           |

| 4 input LUTs     | 319           |

| IOs              | 378           |

| Bonded IOBs      | 376           |

| GCLKs            | 2             |

TABLE 4.1 Synthesis Report

#### V. CONCLUSIONS

Implementation of a 256Mb, 133MHz DDR SDRAM Data Controller architecture on FPGA is done that obviates high-speed, low-power data transmission between microprocessor (ALU) and memory devices. A digital FPGA path is introduced. A prototype implemented in Spartan-3E FPGA process operates at 256Mb and 133MHz with a 2.5V supply. The Language used is Verilog HDL. Xilinx (ISE) is used for the simulation and implementation purpose. This is operated in Base Mode Register.

#### VI. ACKNOWLEDGMENT

This work has been done in Project lab, Electronics & communication Department. The authors would like to thank the Director (Academics) and the Management of SKIT, Jaipur for permission to carry out this work.

#### REFERENCES

- [1] Synthesizable DDR SDRAM controller, Application note, 2002(Xilinx Inc., XAPP200)

- [2] Using the Virtex Select I/O Resource, Application note, 1999(Xilinx Inc., XAPP133)

- [3] B. Ram, "Advanced Microprocessors and Interfacing", (3rd Reprint), Tata McGraw-Hill, 2007.

- [4] Virantha N. Ekanayake and Rajit Manohar,"Asynchronous DRAM Design and Synthesis", Proceedings of the Ninth International Symposium on Asynchronous Circuits and Systems (ASYNC'03), 2003.

- [5] Hiroaki Ikeda and Hidemori Inukaiq,"High-Speed DRAM Architecture Development," IEEE Journal of Solid-State Circuits, Vol. 34, No. 5, May 1999.

- [6] Micron Technology Inc., Double Data Rate (DDR) SDRAM, Datasheet, 1999 (http://www.micron.com/products/dram/ddrsdram)

- [7] Deepali S h a r m a, Shruti bhargava, M a h e n d r a Vucha, "Design and VLSI Implementation of DDR SDRAM Controller for High Speed Applications", (IJCSIT) International Journal of Computer Science and Information Technologies, Vol. 2 (4), 2011, 1625-1632.

- [8] J. W. Li Wang, Qian Zhang, "Design and Implementation of DDR SDRAM Controller Based on FPGA in Satellite Navigation System," Signal Processing (ICSP), vol. 1, pp. 456 - 460, 2012.

- [9] M. S. K. SAK Patel, "DESIGN OF DDR SDRAM CONTROLLER FOR EMBEDDED SYSTEM" Journal of Information, Knowledge and Research in Electronics and Communication Engineering, Nov12 to Oct13.

- [10] Heithecker, S. and Ernst, R., "Traffic Shaping for An FPGA Based SDRAM Controller with Complex QoS Requirements", Design Automation Conference 2005, June2005, pp.575-578.

www.ijraset.com IC Value: 45.98 Volume 5 Issue IV, April 2017 ISSN: 2321-9653

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

- [11] Zude Zhou, Songlin Cheng, and Quan Liu,"Application of DDR Controller for High-speed Data Acquisition Board," Proceedings of the First International Conference on Innovative Computing, Information and Control(ICICIC'06),2006.

- [12] A. C. Bonatto, A. B. Soares, and A. A. Susin, "DDR SDRAM Memory Controller Validation for FPGA Synthesis," in LATW2008: Proceedings of the 9th IEEE Latin-American Test Workshop, Puebla, Mexico, Feb. 2008, pp.177–182.

- [13] ALTERA, DDR SDRAM Controller White Paper, Ver1.1, 2002, 8.

- [14] Guo Li, Zhang Ying, Li Ning, and Guo Yang, "The Feature of DDR SDRAM and the Implementation of DDR SDRAM Controllers via VHDL", The Journal of China Universities of Posts and Telecommunications, 2002, vol.9, no. 1, pp. 61-65.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)