IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: VII Month of publication: July 2017 DOI:

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

## Implementation of Modified Decimal Matrix Code for Multiple Cell Upset

Anjali Kumari<sup>1</sup>, Dr. Prachi Chaudhary<sup>2</sup> <sup>1</sup>M.Tech in ECE (VLSI DESIGN), <sup>2</sup>Assistant Professor Deenbandhu Chhotu Ram University of Science and Technology, Murthal, Sonepat

Abstract : The reliability of memory cells is becoming an essential issue today. Transient single bit errors and multiple bit upsets (MBUs) are responsible to limit the reliability of memory which causes due to radiation environment. To maintain good reliability of memory cell some codes are used to correct these single and multiple bit errors. But the main issue with these codes is that they require large area and delay overhead. The codes like hamming code are used to remove single bit upsets (SBUs) are simpler than multiple bit upsets (MBUs), but can correct single error and detect double or triple adjacent error. So to improve the memory reliability with lesser area and delay overhead, a new method Decimal Matrix Code (DMC) has been presented based on divide symbol and arrange in matrix logically which can detect and correct multiple errors. In this paper, 32-bits MDMC is proposed to enhance the memory reliability based on divide symbol which can detect and correct up to 16 errors. To reduce the area overhead of extra circuit's encoder-reuse technique (ERT) is used in which same circuit used for encoding and decoding process. Verilog HDL used for low power design and simulation and implementation can be done using Xilinx Vivado. Keywords: Single Bit Upsets (SBUs), Multiple Bit Upsets (MBUs), Error Correction Code (ECC), Modified Decimal Matrix Code (MDMC), Encoder-Reuse Technique (ERT)

## I. INTRODUCTION

As the scaling technology increases, the reliability of memory cell becomes limited due to radiation environment and territorial environment. Error produce in memory cell because of radiation environment called soft error which may cause of falling rate of reliability of memories [1]. These soft errors may be single cell upset or multiple cell upset. These errors can be removed using error correction code like Hamming codes, Reed Solomon, CRC technique, matrix code and decimal matrix code etc.

Hamming codes are simpler coding technique which can only detect and correct single error so double error can be mistaken and mis-corrected for a single error [2]. To remove this problem hamming codes are extended which can correct single error but detect up to double and triple adjacent error through selective shortening and bit replacement. Reed Solomon code is used to correct the multiple errors, specially the burst type errors in storage devices like DVD, hard disk drives, barcode tags, mobile communications and wireless units, digital TV, modem technologies, digital video broadcasting (DVB), and satellite links [3]. But the drawback of this code is that they can correct two or burst error and require large area and delay overhead. To improve the memory reliability new technique Matrix code has been proposed which is based on parity detection method. The correct- capability of matrix code is determined based on the width of error in MCU.

In this paper, Decimal Matrix Code is modified to increase the memory reliability with lesser delay and area. The proposed Modified DMC utilize the decimal integer subtraction to detect the errors. Proposed MDMC increase the error detection and correction capability which leads to enhance the memory reliability. Using the encoder reuse technique (ERT) the area of extra circuits can be diminished because encoder circuit also used as decoder circuit without interrupting the complete encoding and decoding process.

The paper is organized as follows; in section 2 the literature survey of different technique is presented. The Proposed Modified DMC and its Encoder, Decoder architecture is presented in section 3. Implementation and results of proposed technique is shown in section 4. Finally in Section 5 the conclusion of paper and ideas for future work is presented.

## II. LITERATURE SURVEY

Soft errors occur in memories due to cosmic rays etc are protected with Error Correction Codes (ECCs). Simple error correction codes used to minimize the impact of the ECC on memory complexity. For example, Single Error Correction (SEC) codes, like Hamming codes are much simpler than codes used to protect multiple corrupted bits. Hamming codes are mostly used for single error correction with reduce power consumption. These codes can identify double error but correct only single error. To prevent the

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VII, July 2017- Available at www.ijraset.com

occurrence of multiple bit errors Reed Solomon, Bose–Chaudhuri –Hocquenghem (BCH), Built in current sensor (BICS) and Interleaving techniques are used. But these codes have more power consumption, delay and area overhead. To overcome these problems Decimal Matrix Code (DMC) is presented with better memory reliability and reduced power consumption and area. Hamming codes are also called Forward Error Correction code can correct single error and identify up to double bit errors. The minimum distance of the hamming code should be equal to 3. The hamming codes have the following parameters:

| $n=2^{m}-1$   | (1) |

|---------------|-----|

| k=n-m         | (2) |

| $d_{min} = 3$ | (3) |

Where n represents the code size, k is the number of data bits, m is the number of check bits and  $d_{min}$  is the minimum distance of the code [2]. The position of check bits gives different error present in stored data. The parity bits are calculated using parity generator and decoder used to calculate a syndrome value. Zero value of syndrome bit indicates no error. If the value of syndrome bit is non-zero, it means error is present. The main drawback of Hamming codes is that a double error generates a syndrome assigned to a single error correction which leads to a mis-correction and can be cause of wrong decoding. To overcome this drawback SEC-DED extended Hamming codes were proposed. To increase memory reliability more than one error such that double and triple adjacent error can be detect using enhanced hamming code by reordering the code bits.

Extended Hamming codes can be implemented by adding the Triple-Adjacent Error detection capability which includes an additional check bit. Selective shortening is performed on original hamming matrix and the main objective to identify triple adjacent error is to get an even weight syndrome.

Shortened Hamming codes can detect some multiple errors, but does not provide a given kind of errors systematically [2]. Reed-Solomon codes are mainly used to correct the burst errors. These codes have its own error correcting capability so useful in saving time for identification and correction of error. Reed Solomon code can detect and correct multiple random symbol errors by adding t check symbols to the data [3]. An RS code can identify any combination of up to t erroneous symbols and can correct up to [t/2] symbols. The main problem of RS codes is that they require more power and area overhead. Interleaving technique has also been used to deal with multiple bit errors in memory cell. Interleaving technique rearrange cells into different physical positions to separates the different bits of different physical words from the same logical word. Interleaving technique has tight coupling of hardware structure from both cells and circuit structure so may not be used in content-addressable memory (CAM). Built-in current sensors (BICS) are proposed to provide protection against multiple corrupted bits with correction of single error and identification of double-error. However, BICS technique can correct only two errors in a word [7].

To correct the multiple corrupted bits 2-D matrix codes (MCs) are proposed which require low decoding delays. In this code, data word is divided into multiple rows and multiple columns logically. Hamming code are used to protest the bits per row, while bits per column are protected by Parity code. The 2-D Matrix codes can correct only two errors which are identified by Hamming code and can be correct when the vertical syndrome bits are activated [9]. As different error correction coding techniques used to prevent the occurrence of multiple bit error, however the main problem is that they require complex encoder and decoder circuit, power, area and delay overhead. To minimize these drawbacks compared to existing codes, Decimal matrix code is proposed which increase the memory reliability by improving the error correction capability [9].

Decimal matrix code (DMC) is based on divide symbol method and use decimal algorithm to obtain the maximum error identification capability. DMC use the encoder- reuse technique (ERT) in which DMC encoder used as a part of decoder, soreduce the area overhead. ERT technique is proposed in fault tolerant memory.

## III. METHODOLOGY

The Modified DMC method is proposed to decrease the number of check bits so that more number of information bits can be stored in memory cell. The parallel check bits "H" and vertical check bits "V" are calculated to identify and correct the corrupted bits present in memory cells. To increase the reliability of memory cells with lesser area the Modified DMC is presented with same circuit for encoder and decoder using encoder- reuse technique. The fault tolerant system is used to reduce the possibility of faults in encoder and decoder circuit.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VII, July 2017- Available at www.ijraset.com

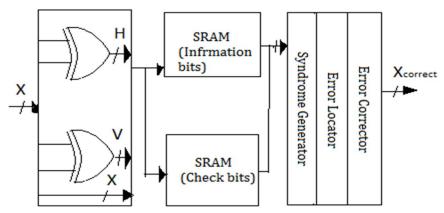

## A. Fault Tolerant System of Proposed MDMC

The fault tolerant system schematic includes DMC encoder, SRAM to store the data and redundancy bits and DMC decoder as shown in figure 3.1. Firstly, the data bits X are provided to encoder and obtained the parallel and vertical redundancy bits H and V respectively. After the end of encoding process these redundant bits are stored in memory. If any radiation particle hits the memory cells, MBUs happen in memory and these corrupted bits can be corrected in decoding process. To reduce the area overhead ERT technique is proposed.

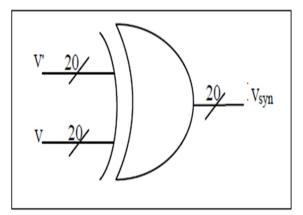

Figure 3.1 Schematic of fault tolerant system of Modified DMC [4].

## B. Proposed MDMC Encode

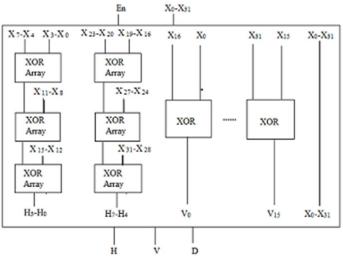

Proposed MDMC is performed on the basis of divide the symbol and arrange in matrix form ideas where matrix is implemented logically so changes in physical structure of memory do not require. In this proposed method the N-bit data word is divided into m symbols of n bits where  $N = m \times n$ , and these m symbols are arranged in  $m_1 \times m_2$  2-D matrix (m=m1  $\times$  m2) where values of  $m_1$  represent the number of rows and values of  $m_2$  represent number of columns in the logical matrix [4]. 32-bit (X<sub>0</sub>-X<sub>31</sub>) codeword divided into 8 symbols (S<sub>0</sub>-S<sub>7</sub>) of 4 bits and arranged in matrix form is shown in figure 3.2.

The parallel (horizontal) check bits H are obtained by implementing the decimal integer subtraction of sort out symbols per row and vertical check bits V are achieved by implementing the binary operation among the bits per column. In the presented paper, 32-bit binary codeword is taken as example. The information bits  $X_0$ - $X_{31}$  directly stored in memory while the  $H_0$ - $H_{15}$  parallel check bits and  $V_0$ - $V_{15}$  vertical check bits are calculated using decimal integer subtraction and then stored in memory. The parallel and vertical check bits in encoder called as Write Redundant.

Figure 3.2 32-bit encoder circuit of Modified DMC [5].

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VII, July 2017- Available at www.ijraset.com

Parallel Check Bits Calculation: 32 bit data word is divided into 8 symbols S<sub>0</sub>-S<sub>7</sub> of 4 bits. The symbols S<sub>0</sub>-S<sub>3</sub> are applied to XOR array to get the parallel check bits [H<sub>3</sub>H<sub>2</sub>H<sub>1</sub>H<sub>0</sub>]. Similarly symbol S<sub>4</sub>-S<sub>7</sub> are applied to XOR array to generate their check bits [H<sub>7</sub>H<sub>6</sub>H<sub>5</sub>H<sub>4</sub>]. Equation 1 and 2 are used to calculate the parallel check bits.

$$X_{15}X_{14}X_{13}X_{12}^{A}X_{11}X_{10}X_{9}X_{8}^{A}X_{7}X_{6}X_{5}X_{4}^{A}X_{3}X_{2}X_{1}X_{0} = H_{3}H_{2}H_{1}H_{0}$$

$$X_{31}X_{30}X_{29}X_{28}^{A}X_{27}X_{26}X_{25}X_{24}^{A}X_{23}X_{22}X_{21}X_{20}^{A}X_{19}X_{18}X_{17}X_{16} = H_{7}H_{6}H_{5}H_{4}$$

(2)

2) Vertical Redundant bits Calculation: Vertical check bits are acquired by XOR operation performed on the bits per column. For example Vertical bit  $V_0$  is calculated by XOR operation of bit  $X_0$  and  $X_{16}$ . Similarly all other vertical check bits are evaluated as follows:

$$\begin{array}{l} X_0^{\ }X_{17} = V_1 \\ X_1^{\ }X_{18} = V_2 \end{array} \tag{3}$$

The generalized form to calculate vertical parallel bits can be given as -

$$\mathbf{X}_{n}^{\mathbf{A}}\mathbf{X}_{n+16} = \mathbf{V}_{n}$$

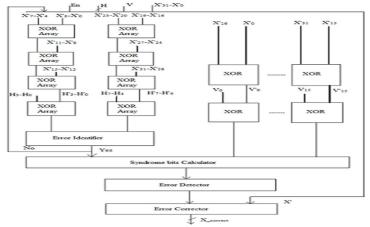

## C. Proposed MDMC Decode

MDMC decoder used the same circuit as encoder using encoder- reuse technique (ERT). Decoding process is done to get the original data. Table1 explain how same circuit can be used for both encoder and decoder circuits where En (enable) signals distinguish the encoder from the decoder.

Table1

| Encoder circuit behavior in MDMC [4] |           |       |          |

|--------------------------------------|-----------|-------|----------|

| Extra<br>Circuit                     | En Signal |       | Function |

|                                      | Read      | Write | Function |

| Encoder                              | 0         | 1     | Encoding |

|                                      | 1         | 0     | Decoding |

The proposed technique detect all possible errors in codeword, therefore it increase the error detection capability from all other related techniques and enhance the memory reliability. MDMC decoder includes Syndrome calculator, Error locator and Error corrector as shown in figure 3.4. Each module of proposed MDMC decoder executes their specific job. In MDCM decoder the data in each row decoded to recalculate the parallel and vertical check bits for detection and correction of corrupted bits.

Figure 3.4. 32-bits decoder circuit of Modified DMC

A S Course Cours

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VII, July 2017- Available at www.ijraset.com

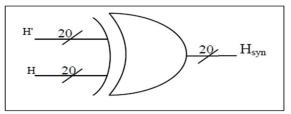

Redundant bits are recalculated from received information bits to calculate the syndrome bits. Computation of these redundant bits in decoder is called as RR (Read Redundant). The difference between stored check bits and re-evaluated check bits provide the horizontal syndrome bits  $H_{syn}$  and vertical syndrome bits  $V_{syn}$  as shown in figure 3.5 and figure 3.6. The difference between stored check bits and re-evaluated check bits gives the syndrome bits.

Figure 3.5 Horizontal Syndrome bits using XOR operation [11].

Figure 3.6 Vertical Syndrome bits using XOR operation [11].

Parallel syndrome bits can be calculated as-

$\Delta H_3 H_2 H_1 H_0 = H_3 H_2 H_1 H_0 \wedge H_3 H_2 H_1 H_0$  $\Delta H_7 H_6 H_5 H_4 = H_7 H_6 H_5 H_4 \wedge H_7 H_6 H_5 H_4$

Vertical syndrome are calculated as

$$\mathbf{V}_{\mathrm{syn},0} = \mathbf{V}_0' \wedge \mathbf{V}_0$$

Error locator locates the error using the syndrome bits which can be become error-free by flipping the values of corrupted bits. The horizontal syndrome bits and vertical syndrome bits with same length are grouped to locate the corrupted bit in any symbol. The grouping of these syndrome bits is shown as

$$\begin{array}{c} H_{syn} \\ (8\text{-bits}) \\ \end{array} \begin{array}{c} H_{syn,3-0} \\ H_{syn,7-4} \\ \end{array} \\ V_{syn} \\ (16\text{-bits}) \\ \end{array} \begin{array}{c} V_{syn,7-4} \\ V_{syn,7-4} \\ V_{syn,11-8} \\ V_{syn,15-12} \\ \end{array}$$

Similarly other vertical syndrome bits can be calculated. If the value of syndrome bit is equal to zero, no error occurs in stored data otherwise error is present. Error locator locates the error using the syndrome bits which can be become error-free by flipping the values of corrupted bits.

The error corrector corrects the corrupted bits by inverting the corrupted bits. The bits are inverted using the XOR operation.

$$D_{0\_correct} = D_0 \land S_0$$

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VII, July 2017- Available at www.ijraset.com

In the presented MDMC technique, the area of extra circuit is minimized by reusing its encoder circuit as decoder known as ERT. The En signal used to decide whether the encoder circuit will act as decoder so mainly used to distinguish the encoder and decoder under manage of write and read signal.

## A. RTL View of Modified DMC

## IV. IMPLEMENTATION AND RESULTS

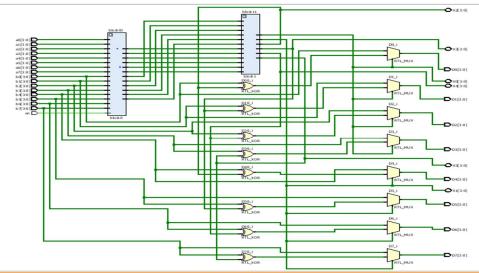

RTL view of proposed Modified DMC is shown in figure 4.1 which includes the two blocks. The first block provide the parallel and vertical check bits of stored data and received data word and the second block provide the syndrome bits by comparing these parallel and vertical check bits.

Figure4.1. RTL View of 32-bit Modified DMC

## B. Simulation Result

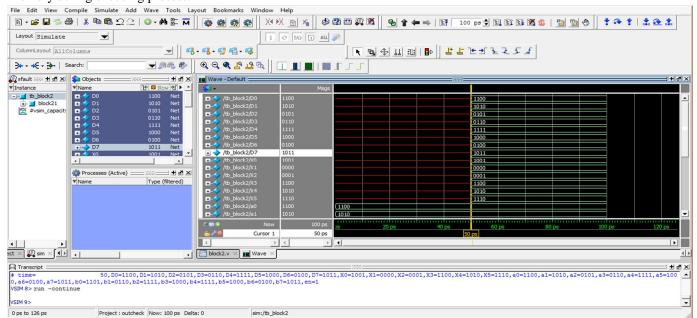

Simulation result of 32-bit Modified DMC is shown in figure 4.2. The output waveform shows the data same as the data word stored in memory during encoding process.

Figure 4.2. Simulation Result of 32-bit Modified DMC

Volume 5 Issue VII, July 2017- Available at www.ijraset.com

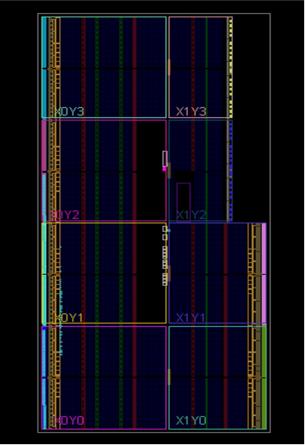

*C. Synthesis Result* The synthesis result of 32-bit Modified DMC is shown in figure 4.3.

Figure 4.3. Synthesis result of Modified DMC.

## V. CONCLUSION AND FUTURE WORK

The proposed paper presents the detection and correction of corrupted bits stored in memory cells using the Modified Decimal Matrix Code. Decimal integer subtraction used to calculate the horizontal check bits and XOR operation is used to calculate the vertical check bits. These check bits are calculated from the original data word stored in memory during encoding process and from received data in decoder. The proposed Modified DMC technique enhances the memory reliability with less number of redundancy bits. The number of redundant bits is 24 and corrects up to 16 multiple bits error in 32 bit data word.

In the future, more number of corrupted bits can be identify and correct to increase the memory reliability. The number of check bits also can be decrease with less area and delay so that more number of information bits can be store in memory cell.

## REFERENCES

- Robert C. Baumann, "Radiation-Induced Soft Errors in Advanced Semiconductor Technologies" IEEE Transactions on Device and Materials Reliability, Vol.5, NO.3, September 2005.

- [2] A. Sanchez-Macian, P. Reviriego, and J.A. Maestro, "Enhanced Detection of Double and Triple Adjacent Errors in Hamming Codes through Selective Bit Placement," IEEE Transactions on Device and Materials Reliability, vol. 12(2), June.2012,pp.357-362.

- [3] Priyanka Shrivastava, Uday Pratap Singh, "Error Detection and Correction Using Reed Solomon Codes," International Journal of Advanced Research in Computer Science and Software Engineering, Volume 3, Issue 8, pp. 965-969, August 2013.

- [4] Jing Guo, Liyi Xiao, Zhigang Mao and Qiang Zhao, "Enhanced Memory Reliability Against Multiple Cell Upsets Using Decimal Matrix Code", IEEE Transactions on Very Large Scale Integration Systems, Vol.22 No.1, pp.127-135, January 2014.

- [5] Satyabala, Akhilesh Jain, "Memory Reliability Enhancement against Multiple Cell Upsets Using Decimal Matrix Code for 32-Bit Data" International Journal on Recent and Innovation Trends in Computing and Communication, Vol. 4, Issue 4, pp. 654 – 659, April 2016.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VII, July 2017- Available at www.ijraset.com

- [6] Linz Elizabeth Kurian, Binu K Mathew, "Performance Comparison of an Error Correction Technique in Memory" International Conference on Control, Instrumentation, Communication and Computational Technologies (ICCICCT), pp. 355-359, 2014.

- [7] Preethi.k, Karthik.T, "Protection Of Memory Using Code Redundancies A Survey," International Conference on Green Engineering and Technologies, 2015 IEEE.

- [8] Anshul Soni, Ashish Raghuwanshi, "Review on DMC encoding of data for enhanced memory reliability against multiple cell upsets," EPRA International Journal of Research and Development, Volume 1, Issue 3, pp. 54-59, May 2016.

- [9] David S, and Gayathree K., "A Comparative Study of Various Error Correction Codes", International Journal of Computer Science and Mobile Computing(IJCSMC), Vol.3 Issue 8, pp.196-200, August 2014.

- [10] E. Abinaya, D. Somasundareswari and S. Mathan Prasad, "Implementation of a Decimal Matrix Code for Correcting Multiple Cell Upsets in SRAM based FPGA Memories", International Journal of Advanced Research Trends in Engineering Technology (IJARTET), Vol.2,Issue 8, pp.87-93, 2015.

- [11] V. Vithya and P. Sakthivel, "Memory Reliability enhancement against Multiple Cells Upset using Decimal Matrix Code for 32-bit data", International Journal on Recent and Innovation Trends in Computing and Communication", vol. 4, April 2016, ppp. 654-659.

- [12] Sandeep M. D. and Rajashekhargouda C. Patil, "An approach to Reduce Number of Redundant Bits used to Overcome Cell Upsets in Memory using Decimal Matrix Code", ACEEE International Conference on Recent Trends in Signal Processing, Image Processing and VLSI (ICRTSIV), 2014.

- [13] Anagha. K.Nand Raghu.M.C, "Modified decimal matrix codes for error detection in memory using pipeline architecture," International Journal of Advanced Research, Volume 4, Issue 7, pp. 1454-1459, 2016.

- [14] Gayathree.K, David.S and Moortheeswari.M, "Reliability Enhancement Using Parity Algorithm," International Journal of Innovative Science, Engineering & Technology, Vol. 2 Issue 4, pp. 1176-1180, April 2015.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)