# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: VII Month of publication: July 2017

DOI:

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VII, July 2017- Available at www.ijraset.com

### FPGA Implementation of Pipelined 2D-IDCT for JPEG Image Decompression

Ms. Pallavi D Chakole<sup>1</sup>, Prof. Amit Fulsunge<sup>2</sup>

1,2 Electronics and Communication Engineer, RTM Nagpur University

Abstract: Digital age of world has faced a vast amount of information, which results in many difficulties to deals that vast information. We must store, retrieve, analyze and process Digital information in an efficient way, so as to be put to practical use. There are many aspects of digital technology have been developed. Specifically in the fields of image acquisition, data storage and bitmap printing. Compressing an image is significantly different than compressing raw binary data. Every Image has certain statistical properties which can be exploited by encoders specifically designed for them so, the result is less than optimal when using general purpose compression programs to compress images.

Keywords: Digital age, bitmap Compressing, binary data, encoder, optimal.

### I. INTRODUCTION

One of many techniques under image processing is image compression. Image compression has many applications and plays an important role in efficient transmission and storage of images. The image compression aims at reducing redundancy in image data to store or transmit only a minimal number of samples And from this we can reconstruct a good accession of the original image by decompression method in accordance with human visual perception. Multiple compression schemes have been introduced. Data compression method is different depending on the type of data for several applications such as: MPEG4, H2642 for video compression, and JPEG and JPEG 2000 for image compression. One of the most popular compression method is JPEG. JPEG stands for Joint Photographic Expert Group. JPEG provides for lossy compression of images. The main block present in the compression scheme is the transformation domain block. Discrete Cosine Transform (DCT) with applications in audio filtering to video compression is a mathematical tool which converts the information from the time or space domains to the frequency domain. The Discrete Cosine Transform (DCT) is used in order to reduce the spatial redundancies by transforming the spatial domain in the spectral domain. The principal behind the transformation with DCT algorithm is the removal of redundancy between neighboring pixels. Efficiency of the coder can be evaluated by its ability to compress data into as few coefficients as possible. This allows the quantizer to eliminate the coefficients with small amplitudes without introducing visual degradation. DCT achieves important energy reduction for highly correlated images. DCT's energy compaction efficiency is also greater than any other transform. The one-dimensional DCT is useful in processing one-dimensional signals such as speech waveforms. For analysis of two dimensional (2D) signals such as images, we need a 2D version of the DCT data, especially in coding. As far as decoding is concerned 2D-IDCT (Inverse Discrete cosine Transform) mathematical tool can be used for decompression of compressed image for extraction of original images. This paper focuses only in a pipelined hardware implementation of the main part of the JPEG standard: the Two Dimensional Inverse Discrete Cosine Transform for retrieving original images to be transmitted by the users. This is the most critical module to be designed in JPEG compressor hardware because of its high algorithm complexity. This work proposes initially a FPGA implementation for flexibility, time-to-finish and development purposes. [1].

### II. RESEARCH ANALYSIS

: "FPGA Implementation of Forward 2D-DCT and Inverse 2D-DCT Based On Row-Column Decomposition Method 2Dimension Discrete Cosine Transform, Field Programmable Gate Array (FPGA), Very Large Scale Integrated Hardware Discreptional Language VHDL, image compression, video compression. This paper describes the FPGA implementation of two dimensional forward Discrete Cosine Transform and inverse DCT. 2D-DCT is computed by combining two 1D-DCT that connected by a transpose buffer. Firstly we implemented the forward 1D-DCT row wise that requires addition, subtraction, registers and multipliers, and then column wise. For inverse 1D-DCT we implemented 1D-DCT column wise and then row wise. It possesses features of regularity and modularity, and is thus well suited for VLSI implementation. It can be used for the computation of either the forward or the inverse 2D DCT. Each of the sub-operation is researched for different implementations and then synthesized onto a Xilinx14.2 ISE device to be chosen for best performance. "Jpeg Image Compression Using Discrete osine Transform - A Survey" International Journal of Computer Science & Engineering Survey Image Compression, JPEG, Discrete Cosine Transform Due to

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VII, July 2017- Available at www.ijraset.com

the increasing requirements for transmission of images in computer, mobile environments, the research in the field of image compression has increased significantly. Image compression plays a crucial role in digital image processing, it is also very important for efficient transmission and storage of images. When we compute the number of bits per image resulting from typical sampling rates and quantization methods, we find that Image compression is needed. Therefore development of efficient techniques for image compression has become necessary. This paper is a survey for lossy image compression using Discrete Cosine Transform, it covers JPEG compression algorithm which is used for full-colour still image applications and describes all the components of it. JPEG, discrete cosine transform (DCT), quantization, zigzag, FPGA, Model Sim This paper presents the architecture and the VHDL design of a Two Dimensional Discrete Cosine Transform (2-D DCT) for JPEG image compression. This architecture is used as the core of a JPEG compressor and is the critical path in JPEG compression hardware. Many algorithms and VLSI architectures for the fast computation of DCT have been proposed [10,11,12] The 2-D DCT calculation is made using the 2-D DCT separability property, such that the whole architecture is divided into two 1-D DCT calculations by using a transpose buffer. These parts are described in this paper, with an architectural discussion and the VHDL synthesis results as well. The 2-D DCT architecture uses 5,651 logic cells of one Spartan3 FPGA and reaches an operating frequency of 123 MHz. One input block with 8×8 elements of 8 bits each is processed in 5.2 µs and the pipeline latency is 160 clock cycles. This paper provides the architectural view and FPGA implementation of 2D-DCT for JPEG image compression. DCT, FPGA, Image Compression, JPEG Image compression is the application of data compression on digital images. DCT has been widely used in signal processing of image. The one-dimensional DCT is useful in processing one-dimensional signals such as speech waveforms. For analysis of two dimensional (2D) signals such as images, we need a 2D version of the DCT data, especially in coding for compression, for its near-optimal performance. JPEG is a commonly used standard method of compression for photographic images. We propose to work on an efficient architecture for the design of a Two Dimensional Discrete Cosine Transform (2-D DCT) for JPEG image compression. We will consider an area optimized architecture for 2D DCT and FPGA implementation of 2D-DCT for JPEG image compression. Our proposed method will utilize Xilinx and Altera EDA tools for both Simulation and synthesis. We have selected the hardware description language as VHDL and hardware implementation on FPGA.

### **III.IMPLEMENTATION**

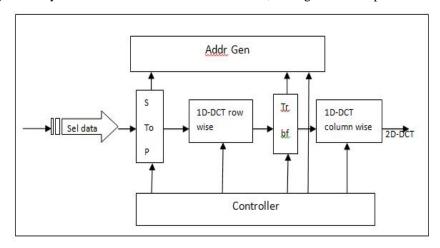

The Transform are widely used in video and image applications. Several groups, such as The International Organization for Standardization (ISO), International Telecommunication Union Telecommunication Standardization Sector (ITU-T), and Microsoft Corporation, have developed various transform dimensions and coefficients, corresponding to different applications. The most popular technique for image compression was Discrete cosine transform (DCT). Its selection as the standard for JPEG is one of the major reasons for its popularity. The discrete cosine transform (DCT) has emerged as the most popular transform for many image/video compression applications owing to its near optimal performances. Its energy compaction efficiency is also greater than any other transform. The 2D-DCT, in particular, is one of the major operations in current image/video compression standards. It is today the most widely used orthogonal transform for applications including videophone, video conferencing and high definition television. The 2D-DCT is computationally intensive and as such there is a great demand for high speed, high throughput and short latency computing architectures. Due to the high computation requirements, the 2D-DCT processor design has been concentrated on small non overlapping blocks (typical 8x8). Many 2D-DCT algorithms have been proposed to achieve reduction of computational complexity and thus increase the operational speed and throughput. The output port DOUT provides the results of the 2-D DCT. The output control signal RDY when asserted indicates that the value on the DOUT port is valid. The width (Wres) of DOUT is defined by the resulting width parameter, depending on the precision control selected for the results. The results of the 2-D DCT are provided sequentially on this port DOUT, column-wise. Selection of input data is serially goes to the serial to parallel block. The transpose buffer/ parallel to parallel block operates like a temporal barrier between the first and the second 1D-DCT. The control module is implemented using a state machine. The state machine is divided into three states: idle state, row 1D-DCT state, and column 1D-DCT state. After the valid reset signal, the initial state is the idle state. When the valid pixel data come in, the state machine enters into row 1D-DCT state. After maintaining 64 clock cycles, it goes into column 1D-DCT state. While the column 1D-DCT state finished, the state machine recalls the idle state and sets the done signal meanwhile, then it just waits for the next  $8 \times 8$ point 2D-DCT. It has the ability to pack energy in the lower frequencies for image data. (2) It has the ability to reduce the blocking artefact effect and this effect results from the boundaries between sub-images become visible. We refer to the DCT basis functions shown in Figure 2. In performing a DCT on an 8x8 image block, what we are essentially doing is correlating the input image with

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VII, July 2017- Available at www.ijraset.com

each of the 64 DCT basis functions and recording the relative strength of correlation as coefficients in the output DCT matrix. The coefficients corresponding to high-frequency details are located to the right and bottom of the DCT block, and it is precisely these weights which we try to nullify the more zeroes in the 8x8 DCT block, the higher the compression that is achieved.

Fig 1: Internal Architecture of 2D-DCT

### IV, PROPOSED SYSTEM

Although there are many specified versions of JPEG, Baseline JPEG compression (referred to herein simply as "JPEG") embodies a minimum set of requirements. It is lossy, such that the original image cannot be exactly reconstructed (although a "Lossless JPEG" specification exists as well). JPEG exploits the characteristics of human vision, eliminating or reducing data to which the eye is less sensitive. JPEG works well on grayscale and color images, especially on photographs, but it is not intended for two-tone images.

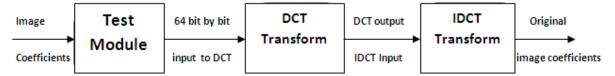

Fig2. Block Diagram

Our Proposed system having three stages Test module, DCT Transform encoder, and IDCT Transform decoder blocks. Original Image pixels coefficients of 8\*8 matrix given to test module, module can transfer data of 64 bits, bit by bit to DCT transform encoder block, it will generate the dct output ,i.e. compressed image of original input image. The DCT output applied to Inverse discrete cosine Transform decoder block for decompression purpose, so that we can get original image back. Figure 1 shows the basic encode process, The DCT stage of JPEG exploits the fact that the human eye favors low-frequency image information over high-frequency details. The 8x8 DCT transforms the image from the spatial domain into the frequency domain. Although other frequency transforms can be effective as well, the DCT is chosen because of its decorrelation features, image independence, efficiency of compacting image energy, and orthogonality (which makes the inverse DCT very straightforward). Also, the separable nature of the 2D DCT allows the computation of a 1D DCT on the eight column vectors, followed by a 1D DCT on the 8 row vectors of the resulting 8x8 matrix. For uniform handling of different image components, the DCT coder usually requires that the expected average value for all pixels is zero. Therefore, before the DCT is performed, a value of 128 may be subtracted from each pixel (normally ranging from 0 to 255) to shift it to a range of --127 to 127. This offset has no effect on the AC characteristics of the image block. It is instructive to take a visual view of the DCT transform. The main purpose of this chapter is to present the implementation results of the area and power efficiency analysis performed on the proposed AES design. Synthesis and Power analysis reports of the AES design using Xilinx ISE and Quartus II are presented. Power analysis tools can be used to estimate how much power a design will use on a specific device before being actually uploaded to it. The tools have a model of the power consumption of each of the device's components and can evaluate how much power a design will dissipate based on the usage of

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VII, July 2017- Available at www.ijraset.com

each of the components by a design. The tools determine which routing, logical and functional resources are used by a design using information from the post place and route design file, and use frequency and activity factor information obtained either by estimation or from post place and route simulation of the design. We can implement IDCT with the help of CORDIC processor which results in a multiplier less architectures and comparison is made between the DCT using Chen's algorithm and DCT using CORDIC as well as new CORDIC algorithm.

### IV.IMPLEMENTATION RESULT

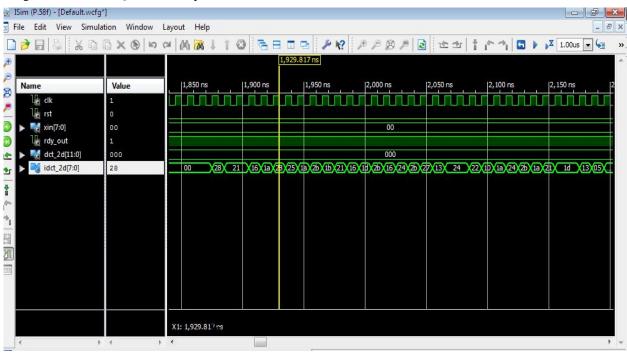

The design for Advanced Encryption Standard using the above design goals and strategies has been coded by VHDL. The synthesis and simulation results are obtained using Xilinx ISE 14.5. The main purpose of this chapter is to present the implementation results of the area and power efficiency analysis performed on the proposed AES design. Synthesis and Power analysis reports of the AES design using Xilinx ISE and Quartus II are presented.

Power analysis tools can be used to estimate how much power a design will use on a specific device before being actually uploaded to it. The various results and simulation of the project are discussed as below with program logic, logic diagram and RTL viewer. The tools have a model of the power consumption of each of the device's components and can evaluate how much power a design will dissipate based on the usage of each of the components by a design. The tools determine which routing, logical and functional resources are used by a design using information from the post place and route design file, and use frequency and activity factor information obtained either by estimation or from post place and route simulation of the design. In this situation the proper scaling is usually performed in the stage of DCT coefficient dividing to the scale factors before the Huffman coding. When this signal is high it acknowledges that the data is correct and can be observed. We can implement IDCT with the help of CORDIC processor which results in a multiplier less architectures and comparison is made between the DCT using Chen's algorithm and DCT using CORDIC as well as new CORDIC algorithm. In this project module idct output can be obtained from dct input. So it is must to calculate dct output and then give it to IDCT block to reconstruct the original pixle coefficients.

### V. CONCLUSIONS

The JPEG image compression is designed in VHDL. We proposed a new direct 2D IDCT architecture for a fast efficient scaled transform. The preprocessors predict the zero quantized coefficients and can reduce up to 50% of the total operations. Discrete

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VII, July 2017- Available at www.ijraset.com

Cosine Transform 2-dimensional transformed followed by inverse Discrete Cosine Transform 2-dimensional transformed. In this thesis we present FPGA based 2D-IDCT for decompression purpose. The design implemented in the Xilinx IES 14.5 FPGA chip can complete the 2D-DCT/IDCT logic operations correctly at 136.212MHz clock Frequency with the clock period of 7.432ns.

### REFERENCES

- [1] Enas Dhuhri Kusuma, Thomas Sri Widodo "FPGA Implementation of Pipelined 2D-DCT and Quantization Architecture for JPEG Image Compression" 978-1-4244-6716-7/10/\$26.00 ©2010 IEEE

- [2] Sanjeevannanavar, S. Nagamani, A.N. "Efficient design and FPGA implementation of JPEG encoder using verilog HDL"

- [3] Zulkalnain Mohd-Yusof, Ish& Suleiman, Zulfakar Aspar "Implementation Of Two Dimensional Forward DCT And Inverse DCT Using FPGA". **0-**7803-6355-8/00/\$10.00020IEEE

- [4] Hatim Anas, Said Belkouch, M. El Aakif "FPGA Implementation Of A Pipelined 2D-DCT And Simplified Quantization For Real-Time Applications". 978-1-61284-732-0/11/\$26.00 ©2010 IEEE

- [5] Prashant Chaturvedi, Prof. Tarun Verma and Prof. M. Zahid Alam," A Novel VLSI based Architecture for Computation of 2D-DCT Image Compression", International Journal of Electrical, Electronics ISSN No. (Online): 2277-2626 and Computer Engineering 1(2): 65-70(2012)

- [6] K. Deepthi, R. Ramprakash "Design and Implementation of JPEG Image Compression and Decompression" International Journal of Innovations in Engineering and Technology (IJIET) Vol. 2 Issue 1 February 2013 ISSN: 2319 1058.

- [7] Home site of the JPEG and JBIG committees" <a href="http://www.jpeg.org/">http://www.jpeg.org/</a> (21/04/01

- [8] V. Bhaskaran, K. Konstantinides. Image and Video Publishers, USA, 1999.

- [9] I. Basri, B. Sutopo, "Implementation 1D-DCT Algoritma Feig-Wino grad di FPGA Spartan-3E(Indonesian)". Proceedings of CITEE 2009, vol. 1, 2009, pp. 198-203

- [10] Design & Implementation of JPEG2000 Encoder using VHDL, "Kanchan H. Wagh, Pravin K. Dakhole, Vinod G. Adhau", Proceedings of the World Congress on Engineering 2008 Vol IWCE 2008, July 2 - 4, 2008, London, U.K.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)