## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: VIII Month of publication: August 2017

DOI: http://doi.org/10.22214/ijraset.2017.8168

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887

Volume 5 Issue VIII, August 2017- Available at www.ijraset.com

# VHDL Implementation of UART with Reducing Power Consumption by Linear Feedback Shift Register

Simarjeet Singh, Amandeep Kaur

<sup>1</sup>Assistant Professor, <sup>2</sup>Student, ECE Dept.,

University College Of Engineering, Punjabi University Patiala

Abstract: In Serial communication long Distance signal Distortion. So feedback is important concept for reducing Signal Distortion. In this paper proposed reduction power consumption in UART communication by using LFSR register. In experiment analysis reducing energy by feedback register.

Keywords: Power consumption, LFSR, Integrity, CPU, UART

### I. INTRODUCTION

In parallel communication the cost and many-sided quality of the framework increments because of concurrent transmission of data bits on different wires. Serial communication reduces this disadvantage and develops as compelling strategy in numerous applications for long separation communication as it lessens the flag distortion in light of its basic structure. All inclusive Asynchronous Receiver Transmitter (UART) is a sort of serial communication protocol. The Universal Asynchronous Receiver Transmitter (UART) is a well-known also, broadly utilized gadget for data communication in the field of telecommunication. It has many preferences, for example, straightforward assets, solid execution, and solid antijamming ability, simple to work and acknowledge etcetera. The UART is a huge scale incorporated circuit which contains all the product programming important to completely control the serial port of a PC (Personnel computer). UART performs parallel-to-serial change on data character gotten from the host processor into serial data stream, furthermore, serial-to-parallel transformation on serial data bits got from serial gadget to the host processor. It likewise includes the begin and stop bit to the data for synchronization. Moreover to the fundamental occupation of changing over data from parallel to serial for transmission and from serial to parallel on gathering, a UART will more often than not give extra circuits to signals that can be utilized to demonstrate the condition of the transmission media and to manage the stream of data if the remote gadget is not set up to acknowledge more data [1].

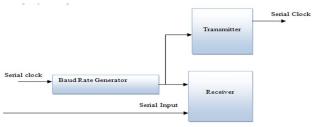

## A. The UART Module

The UART serial correspondence module is isolated into three sub-modules: the baud rate generator, receiver module and transmitter module Therefore, the usage of the UART correspondence module is all things considered the acknowledgment of the three sub-modules. The baud rate generator is really a frequency divider that can be ascertained by framework clock frequency and the sought baud rate. The capacity of baud rate generator is to deliver a neighbourhood clock flag which is considerably higher than the baud rate to control the UART receive and transmit. The receiver performs serial-to-parallel transformation on the asynchronous data outline received from the serial data input. The transmitter module changes over the bytes into serial bits as indicated by the fundamental edge organize received from the CPU. So as to synchronize the asynchronous serial data and to guarantee the data integrity, start, parity and stop bits are included to the serial data.

Fig. 1 UART Module

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887

Volume 5 Issue VIII, August 2017- Available at www.ijraset.com

In second section we discussed the literature review. In third section we show the proposed methodology. In fourth section we result is discussed.

## II. LITERATURE REVIEW

Dr.T.V.S.P.Guptaet. al. [2] The simulated waveforms exhibited in this paper has demonstrated the unwavering quality of the VHDL usage to depict the attributes and the engineering of the composed UART with embedded BIST. The recreated waveforms additionally have demonstrated the spectator to what extent the test outcome can be accomplished by utilizing the BIST system. With the execution of BIST, costly analyzer prerequisites and testing techniques beginning from circuit or rationale level to handle level testing are limited. The LFSR replaces the capacity of the outside analyzer components, for example, a test design generator via naturally creating pseudo arbitrary examples to give 100% blame scope to the UART module. The MISR goes about as a pressure instrument, packing the yield result when programmed pseudo arbitrary example is encouraged to the UART.

Dr.GarimaBandhawarkarWakhleet. al. [3] The proposed paper describes the universal asynchronous receiver/transmitter i.e. UART which is the kind of serial communication protocol which allows the full duplex communication in serial link. This paper presents the hardware implementation of a high speed and efficient UART using FPGA. The UART consists of three main components namely transmitter, receiver and baud rate generator which is nothing but the frequency divider. This has been simulated on ModelSim SE 10.0a and has been implemented by using Verilog description language which has been synthesized on FPGA kits such as Virtex4 and Spartan3.

FANG Yi-yuan et.al. [4] UART (Universal Asynchronous Receiver Transmitter) is a sort of serial correspondence convention; for the most part utilized for short-remove, low speed, ease data trade amongst PC and peripherals. Amid the genuine mechanical generation, now and again does not require the full usefulness of UART, but rather essentially integrate its center part. UART incorporates three kernel modules which are the baud rate generator, receiver and transmitter. The UART executed with VHDL dialect can be integrated into the FPGA to accomplish conservative, steady and reliable data transmission. It's critical for the outline of SOC. The reenactment comes about with Quartus II are totally steady with the UART convention.

Naresh Patel et.al. [5] In parallel communication the cost and additionally multifaceted nature of the framework increments because of simultaneous transmission of information bits on different wires. Serial communication mitigates this disadvantage and develops as viable candidate in numerous applications for long separation communication as it decreases the flag twisting on account of its straightforward structure. This paper concentrates on the VHDL usage of UART with status register which bolsters asynchronous serial communication. The paper introduces the engineering of UART which demonstrates, amid gathering of information, parity error, framing error, overrun error and break error utilizing status register. The entire plan is practically checked utilizing Xilinx ISE Simulator.

T. Praveen Blessington et. al. [6] This paper subtle elements the outline and execution of SoC's DART-SPI Interface. The DART-SPI interface gives utilization to the universal asynchronous receiver/transmitter (DART) to serial peripheral interface (SPI). This interface can be utilized to impart to SPI slave gadgets from a PC with DART port. The interface comprises of three hinders: the DART interface, the DART - toSPI interfacing square and the SPI Master interface.

DipanjanBhadra et.al. [7] All inclusive Asynchronous Receiver Transmitter (UART) actualizes serial correspondence amongst peripherals and remote inserted frameworks. The UART convention is characterized in light of settled frequencies with an inspecting strategy to accomplish strength under sensible recurrence varieties between frameworks. Such outline details are normal for timed spaces. This work examines whether this straightforward timed equipment convention can be favorably actualized utilizing non-concurrent outline methods. A full duplex timed and non-concurrent UART are executed and thought about. The offbeat outline brings about normal energy of around one fourth that of the timed plan under standard working modes.

Ritesh Kumar Agrawalet. al. [8] a UART is the microchip with programming that controls a PC's interface to its connected serial gadgets. The UART is effectively actualized by utilizing Verilog HDL. Assemblage, elaboration, reproduction and blend are performed by utilizing Cadence Tool. The rapid serial information transmits at the rate of 20Mbps by utilizing 20MHz master clock rate. The UART speed is constrained just by transmission media amongst transmitter and recipient and furthermore by CPU speed. The alteration in design as per speed is required just in baud rate generator.

P R Singh et.al. [9] In this work, it accomplished 99.72% diminishment in IOs control utilization of Universal Asynchronous Receiver Transmitter (UART) in the event that it downsized yield stack from 10,000pf to 5pF in IOB setting of FPGA. All inclusive Asynchronous Receiver and Transmitter are a handset circuits that transmit/get information amongst parallel and serial structures and the other way around. Configuration condition of its plan is high on the grounds that no black box found. Bit width is high on

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887

Volume 5 Issue VIII, August 2017- Available at www.ijraset.com

the grounds that 57.6% of primitives in RTL net rundown speak to 1-bit rationale. Here, IO control utilization is 17,226mW on 10,000pF yield stack which altogether lessen to 47mW on 5pF yield stack. Alongside decrease in IOs control, it likewise watched 24.5% lessening in static power utilization from 1322mW on 10,000pF yield load to 1004mW on 5pF yield stack.

L. Supriyaet. al. [10] In this paper, the architecture of BIST empowered UART was outlined and different squares of bist and uart are demonstrated in VHDL. The plan is practically checked by reenacting the code in ModelSim from Mentor Graphics. The FPGA combination is finished utilizing Xilinx ISE device and the outline is executed on SPARTAN 3E FPGA, which depicts the attributes and the architecture of the planned UART with embedded BIST

Ashwini D. Dhanadravye et.al. [11] All inclusive Asynchronous Receiver Transmitter (UART) is generally utilized serial data transmission protocol to bolster full duplex correspondence. UART can be executed in a few routes as indicated by the application required by the planner. A portion of the UART contains FIFOs for the beneficiary or transmitter as data buffer; some of them have the 9 data bits mode etcetera. This paper introduces the survey on such unique systems which were utilizing with UART for solid data transmission. The outline of UART primarily comprises of three piece modules which are beneficiary module, transmitter module and baud rate generator assuming an imperative part in serial correspondence between the UART and host CPU.

Mohd Yamani Idnaldris et.al. [12] This paper is highlight the consideration given by most clients who are anticipating the creator to incorporate testability includes that will increment their item dependability. This paper concentrates on the plan of a UART chip with implanted Built-In-SelfTest (BIST) design utilizing FPGA innovation. The paper begins by portraying the conduct of UART circuit utilizing VHISC Hardware Description Language (VHDL). In the execution stage, the BIST procedure will be fused into the UART outline before the by and large configuration is incorporated by methods for reconfiguring the existing outline to match testability necessities.

BuseUstaoglu et.al. [13] A fault in a single piece in the microprocessors may bring about delicate blunders. It has diverse effects on the program result whether the fault changes a circumstance in the application. Keeping in mind the end goal to dissect the conduct of the applications under the broken conditions they have outlined a custom confirmation framework. The check framework has two sections as Field Programmable Gate Array (FPGA) what's more, personnel computer (PC). They have changed Natalius open source microchip so as to infuse stuck-at-deficiencies into it. They have dealt with a blame infusion strategy and utilized it to expand arbitrariness. On FPGA, they have executed adjusted Natalius chip, the blame infusion technique furthermore, the correspondence protocol.

## **Transmitter side:**

# Start Is LFSR No Ready No Load Data Feedback Is data available Parity generation Transmit by LFSR (Linear Feedback Shift Register) Transmit serially

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887

Volume 5 Issue VIII, August 2017- Available at www.ijraset.com

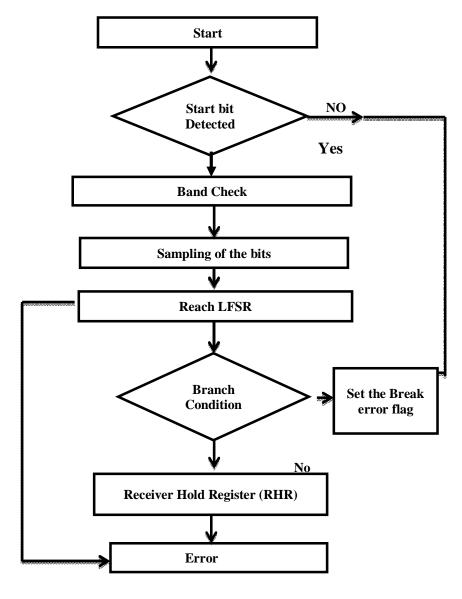

## **Receiver Side:**

## IV. RESULTS

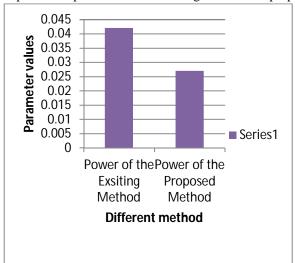

Figure 4.1 Power of existing method:

Figure 4.2 Power of the proposed work:

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VIII, August 2017- Available at www.ijraset.com

Table 4.1 Comparison of power between existingmethod and proposed method:

| Power of the    | Power of the Proposed |

|-----------------|-----------------------|

|                 | rower of the Proposed |

| Existing Method | Method                |

|                 |                       |

| 0.042           | 0.027                 |

Figure 4.3 Comparison of power between existing method and proposed method:

## V. CONCLUSION

UART can be executed in a few routes as indicated by the application required by the planner. A portion of the UART contains FIFOs for the beneficiary or transmitter as data buffer. in serial communication using UART but signal distortion should be reduce with less power using. In this paper experiment proof LFSR reduce power use.

## REFERNCES

[1] Dhanadravye, Ashwini D., and Samrat S. Thorat. "A Review on Implementation of UART using Different Techniques." *International Journal of Computer Science and Information Technologies* 5.1 (2014): 394-396.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VIII, August 2017- Available at www.ijraset.com

- [2] Gupta, Dr TVSP, Y. Kumari, and M. Ashok Kumar. "UART realization with BIST architecture using VHDL." the proceedings of International Journal of Engineering Research and Applications 3.1 (2013): 636-640.

- [3] Wakhle, GarimaBandhawarkar, ItiAggarwal, and ShwetaGaba. "Synthesis and Implementation of UART using VHDL Codes." *Computer, Consumer and Control (IS3C), 2012 International Symposium on.* IEEE, 2012.

- [4] Fang, Yi-yuan, and Xue-jun Chen. "Design and simulation of UART serial communication module based on VHDL." *Intelligent Systems and Applications (ISA), 2011 3rd International Workshop on.* IEEE, 2011.

- [5] Patel, Naresh, Vatsalkumar Patel, and Vikaskumar Patel. "Vhdlimplementation of uart with status register." Communication Systems and Network Technologies (CSNT), 2012 International Conference on IEEE, 2012.

- [6] Blessington, T. Praveen, et al. "Optimal implementation of UART-SPI interface in SoC." *Devices, Circuits and Systems (ICDCS), 2012 International Conference on.*IEEE, 2012.

- [7] Bhadra, Dipanjan, Vikas S. Vij, and Kenneth S. Stevens. "A low power UART design based on asynchronous techniques." *Circuits and Systems (MWSCAS)*, 2013 IEEE 56th International Midwest Symposium on.IEEE, 2013.

- [8] Agrawal, Ritesh Kumar, and VivekRanjan Mishra. "The design of high speed UART." Information & Communication Technologies (ICT), 2013 IEEE Conference on.IEEE, 2013.

- [9] Singh, P. R., et al. "Output load capacitance based low power implementation of UART on FPGA." Computer Communication and Informatics (ICCCI), 2014 International Conference on.IEEE, 2014.

- [10] Supriya, L., J. Lingaiah, and G. Kalyan. "FPGA Implementation of BIST (Built-in Self-test) Enabled UART for Real Time Interface Applications." *International Journal of Science, Engineering and Technology Research* 4.7 (2015): 2645-2647.

- [11] Dhanadravye, Ashwini D., and Samrat S. Thorat. "A Review on Implementation of UART using Different Techniques." *International Journal of Computer Science and Information Technologies* 5.1 (2014): 394-396.

- [12] Idris, Mohd Yamani Idna, and MashkuriYaacob. "A VHDL implementation of BIST technique in UART design." TENCon 2003. Conference on Convergent Technologies for the Asia-Pacific Region. Vol. 4.IEEE, 2003.

- [13] Ustaoglu, Buse, and BernaOrs. "Design and implementation of a custom verification environment for fault injection and analysis on an embedded microprocessor." *Technological Advances in Electrical, Electronics and Computer Engineering (TAEECE), 2015 Third International Conference on.* IEEE, 2015.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)